Fターム[5F152MM04]の内容

再結晶化技術 (53,633) | 半導体素子等への用途 (2,408) | 電子素子 (1,201) | トランジスタ (962) | MOSFET (619)

Fターム[5F152MM04]に分類される特許

201 - 220 / 619

炭化珪素単結晶基板および炭化珪素単結晶エピタキシャルウェハ

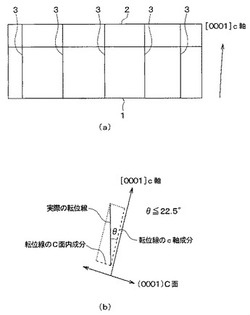

【課題】デバイス特性の劣化や、歩留まりの低下を抑制するため、貫通転位の転位線の方向を規定する方法を提供する。

【解決手段】貫通転位3の転位線の方向が揃えられ、貫通転位3の転位線の方向と[0001]c軸との為す角度θが22.5°以下となるようにする。[0001]c軸方向に転位線を持つ貫通転位3は、基底面転位の転位線の方向と垂直であるため、C面内の拡張転位とはならず、積層欠陥を発生させることがない。このため、貫通転位3の転位線の方向が[0001]c軸であるSiC単結晶基板1に対して電子デバイスを形成すれば、デバイス特性は良好となり、劣化が無く、歩留まりも向上したSiC半導体装置。

(もっと読む)

結晶性半導体膜の作製方法及び薄膜トランジスタの作製方法

【課題】結晶粒径が大きく、均一な結晶性半導体膜を作製する方法を提供する。

【解決手段】絶縁膜上に接して結晶性半導体膜を形成する第1の工程と、前記第1の工程よりも核生成頻度が低い条件により結晶性半導体膜を成長させる第2の工程と、により結晶性半導体膜を作製する。第2の工程は、第1の工程よりも半導体材料ガスの流量比が小さい条件で行う。これにより、結晶粒径が大きく、均一性の高い結晶性半導体膜を得ることができ、結晶性半導体膜の下地膜に対するプラズマダメージを従来よりも低減することができる。

(もっと読む)

半導体材料の薄層の形成

GaAs、またはSiGeのようなゲルマニウム材料のいずれかの層を形成する方法を開示する。例えばゲルマニウム材料は、GaAs面上にエピタキシャル成長することができる。ゲルマニウム材料を一部の残留GaAsと共にレシーバ基板に転写するために、層転写が使用される。次いで残留GaAsは、GaAsとゲルマニウム材料との間の境界がエッチストップとなり、選択的エッチングによって除去することができる。 (もっと読む)

SOI基板の作製方法及び半導体装置の作製方法

【課題】レーザー光の照射による単結晶半導体層の端部からの膜剥がれを抑制した、SOI基板の作製方法及び半導体装置の作製方法を提供する。

【解決手段】加速されたイオンを単結晶半導体基板に照射することによって、単結晶半導体基板中に脆化領域を形成し、絶縁層を介して単結晶半導体基板とベース基板とを貼り合わせ、脆化領域において単結晶半導体基板を分離してベース基板上に絶縁層を介して単結晶半導体層を形成し、単結晶半導体層の端部を除去し、端部を除去した単結晶半導体層の表面にレーザー光を照射する。

(もっと読む)

歪誘起合金及び段階的なドーパントプロファイルを含むその場で形成されるドレイン及びソース領域

【解決手段】

トランジスタのドーパントプロファイルは、その場で(in situ)ドープされた歪誘起半導体合金に基いて得ることができ、段階的なドーパント濃度が高さ方向に沿って確立され得る。その結果、半導体合金をチャネル領域にごく近接して位置させることができ、それにより全体的な歪誘起効果を高めることができる一方で、最終的に得られるドーパントプロファイルについて過度に妥協しなくてよい。更に、半導体合金を選択的に成長させるのに先立ち追加的な注入種が組み込まれてよく、それにより内部歪の注入誘起緩和を回避することができる。

(もっと読む)

電界効果トランジスタ

【課題】歪みチャネルを用いた場合のリーク電流を低減することができ、不良の発生を抑制して歩留まりの向上をはかる。

【解決手段】半導体基板10上に設けられた、基板10とは格子定数の異なる合金半導体からなる下地層20と、下地層20上に設けられた、下地層20とは格子定数が異なり、チャネル長方向及びチャネル幅方向の一方に引っ張り応力、他方に圧縮応力が付与されたチャネル半導体層30と、チャネル半導体層30を挟むように下地層20上に設けられたソース・ドレイン領域60,70と、チャネル半導体層30上にゲート絶縁膜40を介して設けられたゲート電極50とを備えた電界効果トランジスタであって、下地層20は、ソース・ドレイン領域60,70の下部に形成される空乏層61,71が下地層20内に収まる厚さよりも厚く形成され、且つ熱平衡臨界膜厚よりも薄く形成されている。

(もっと読む)

スレッショルド調節半導体合金を堆積させるのに先立ちパターニング不均一性を低減することによる前記半導体合金の厚みばらつきの低減

【解決手段】

シリコン/ゲルマニウム合金のようなスレッショルド調節半導体合金を堆積させるための選択的エピタキシャル成長プロセスにおける成長速度は、選択的エピタキシャル成長プロセスを実行するのに先立ちプラズマ支援エッチングプロセスを実行することによって、高められ得る。例えば、プラズマ支援エッチンプロセスに基いてマスク層がパターニングされてよく、それにより後続の成長プロセスの間に優れたデバイストポグラフィを同時にもたらすことができる。従って、スレッショルド調節材質を高い厚み均一性で堆積させることができ、全体的なスレッショルドばらつきを低減することができる。

(もっと読む)

SOI基板の作製方法、半導体装置の作製方法

【課題】SOI基板の単結晶半導体層中の酸素濃度を低減させる方法を提供する。

【解決手段】単結晶半導体層を溶融状態にすることによって酸素の外方拡散を促進する。具体的には、ベース基板上に設けられた酸素を含有する接合層と、前記酸素を含有する接合層上に設けられた単結晶半導体層と、を有するSOI構造を形成し、前記ベース基板の温度を500℃以上の温度であって前記ベース基板の融点よりも低い温度に加熱した状態において、前記単結晶半導体層をレーザー光の照射により部分溶融させることによって、SOI基板を作製する。

(もっと読む)

半導体電子デバイス

【課題】耐圧性が高く反りが小さい半導体電子デバイスを生産性高く提供すること。

【解決手段】陽極化成してSi基板の一部を多孔質化したSi層を含む基板と、前記基板上に形成された、前記基板よりも格子定数が小さく熱膨張係数が大きい窒化物系化合物半導体からなる第一半導体層と、前記第一半導体層よりも格子定数が小さく前記基板よりも熱膨張係数が大きい窒化物系化合物半導体からなる第二半導体層とが、交互に積層した2層以上の複合層を有するバッファ層と、前記基板と前記バッファ層との間に形成された、前記第一半導体層よりも格子定数が小さく前記基板よりも熱膨張係数が大きい窒化物系化合物半導体からなる介在層と、前記バッファ層上に形成された、窒化物系化合物半導体からなる半導体動作層と、を備えた半導体電子デバイス。

(もっと読む)

半導体装置、半導体装置の製造方法、半導体基板、および半導体基板の製造方法

【課題】化合物半導体と絶縁性材料との界面に形成される界面準位が低減した半導体装置を提供する。

【解決手段】閃亜鉛鉱型の結晶構造を有する3−5族化合物半導体と、3−5族化合物半導体の(111)面、(111)面と等価な面、または、(111)面もしくは(111)面と等価な面から傾いたオフ角を有する面に接する絶縁性材料と、絶縁性材料に接し、金属伝導性材料を含むMIS型電極とを備える半導体装置を提供する。

(もっと読む)

基板上に単結晶半導体層を作製する方法

【課題】基板上に高品質の単結晶半導体層を形成する。

【解決手段】基板上に単結晶の半導体材料の層を形成する方法に関し、この方法は、基板1を準備する工程と、基板上に少なくとも1つの半導体材料の単分子層2を含むテンプレートをエピタキシャル成長する工程と、テンプレート上に半導体材料のアモルファス層3を堆積する工程と、熱処理またはレーザアニールを行い、半導体材料のアモルファス層を、半導体材料の単結晶層に完全に変える工程とを含む。

(もっと読む)

エピタキシャルシリコンウェーハとその製造方法

【課題】シリコン結晶育成時にリンのような電気抵抗率降下用ドーパントとゲルマニウムが一緒に高濃度にドープされた低電気抵抗率のシリコン結晶基板をベースにしたエピタキシャルシリコンウェーハにおいて、ミスフィット転位とスタッキングフォルト(SF)の双方を抑制する。

【解決手段】シリコン結晶育成時に例えばリンとゲルマニウムが一緒に高濃度ドープされたシリコン結晶基板上に、シリコンエピタキシャル層をCVD法で成長させるプロセスにおいて、そのプロセス温度を1000〜1090℃の範囲内(より望ましくは、1050〜1080℃)の範囲内にする。これにより、SFに起因してエピタキシャルシリコンウェーハの表面に生じるLPD(SFに起因して生じる)の個数が大幅に減る。

(もっと読む)

半導体基板の製造方法、半導体基板、電子デバイスの製造方法、および反応装置

【課題】耐熱性の低い部分を有する基板であっても加熱処理が可能となる、基板の熱処理方法を提供する。

【解決手段】熱処理される被熱処理部を備えるベース基板を熱処理して半導体基板を製造する方法であって、電磁波を吸収して熱を発生し、被熱処理部を選択的に加熱する被加熱部をベース基板上に設ける段階と、ベース基板に電磁波を照射する段階と、被加熱部が電磁波を吸収することにより発生する熱によって、被熱処理部の格子欠陥密度を低減する段階とを備える半導体基板の製造方法を提供する。

(もっと読む)

半導体基板の製造方法、半導体基板、電子デバイスの製造方法、および反応装置

【課題】耐熱性の低い部分を有する基板に加熱処理をして半導体基板を製造する。

【解決手段】単結晶層を有し熱処理される被熱処理部と、熱処理で加えられる熱から保護されるべき被保護部とを備えるベース基板を熱処理して半導体基板を製造する方法であって、被保護部の上方に、ベース基板に照射される電磁波から被保護部を保護する保護層を設ける段階と、ベース基板の全体に電磁波を照射することにより被熱処理部をアニールする段階とを備える半導体基板の製造方法を提供する。

(もっと読む)

ホウ素ドープ半導体ナノワイヤ及びその製造方法

【課題】成長軸方向に径の均一なホウ素ドープ半導体ナノワイヤ及びその製造方法を提供する。

【解決手段】成長軸方向に径の均一なホウ素ドープ半導体ナノワイヤは、次の工程を含む製造方法により製造できる。

工程(1):半導体原料ガスを用いて、基板上にIV族半導体ナノワイヤを成長させる;

工程(2):ジボランガスのみを導入することにより、前記半導体ナノワイヤの表面にホウ素膜を堆積させる;

工程(3):表面にホウ素膜を堆積させた前記ホウ素膜付き半導体ナノワイヤを、半導体ナノワイヤ(本体)の融点以下の温度で熱アニールする。

(もっと読む)

半導体装置およびその製造方法

【課題】 エッチング処理を行わなくても、基底面内転位を有する半導体層から結晶成長された半導体層に基底面内転位が伝播することを防止することができる技術を提供する。

【解決手段】 本発明の方法は、半導体層2の表面2aにおける基底面内転位6の位置8を特定する特定工程と、特定工程で特定された位置8において結晶の再配列を行う結晶再配列工程と、結晶再配列工程の後に表面2aから半導体層を結晶成長させる結晶成長工程とを備えている。本発明によると、結晶成長された半導体層に基底面内転位6が伝播しない。基底面内転位6が結晶成長された半導体層に伝播していないために、リーク電流を抑えることができる。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】基板と当該基板に形成される化合物半導体とを電気的に絶縁しつつ、結晶性に優れた化合物半導体を備えた半導体基板を提供する。

【解決手段】ベース基板と、ベース基板上に設けられたシード結晶と、シード結晶の上方に設けられた化合物半導体と、シード結晶と化合物半導体との間に設けられ、シード結晶よりも大きな抵抗率を有する高抵抗層とを備え、シード結晶と化合物半導体とが格子整合または擬格子整合している半導体基板を提供する。

(もっと読む)

グラフェン層が成長された基板およびそれを用いた電子・光集積回路装置

【課題】グラフェン層成膜の大面積化や基板材質の選択自由度の拡大、製造の低コスト化を実現するグラフェン層が成長された基板およびそれを用いた電子・光集積回路装置を提供する。

【解決手段】本発明に係るグラフェン層が成長された基板は、単層または複数層からなるグラフェン層が成長された基板であって、前記グラフェン層は前記基板の表面に対して略平行に成長しており、前記グラフェン層に対向する前記基板の最表面には金属酸化物の原子層が存在し、前記グラフェン層の前記基板に隣接する層と前記金属酸化物の原子層との層間距離が0.34 nm以下であることを特徴とする。また、前記金属酸化物の原子層の算術平均表面粗さRaが1 nm以下であることが好ましい。

(もっと読む)

SOI基板の作製方法

【課題】撓みやすい基板をベース基板として用いる場合であっても、半導体層が設けられた基板(ベース基板)を歩留まりよく作製する。

【解決手段】半導体層が設けられた基板の作製方法において、基板上に設けられた半導体層にレーザ光を照射して当該半導体層の表面を平坦化する工程を有することを特徴とする。そして、前記半導体層の表面を平坦化する工程において、前記レーザ光の照射により前記半導体層が完全溶融するのに必要な最小の照射エネルギー密度を100%としたとき、前記半導体層に照射する前記レーザ光の照射エネルギー密度を72%以上98%以下とし、好ましくは85%以上96%以下とする。

(もっと読む)

半導体装置の作製方法

【課題】面方位が(100)の単結晶シリコン膜および面方位が(110)の単結晶シリコン膜を有するSOI基板を、高い歩留まりで作製する方法を提供する。

【解決手段】面方位が(100)の第1の単結晶シリコン基板1000内に第1のイオンをドープして、第1の脆化層を形成する。面方位が(110)の第2の単結晶シリコン基板1002内に第2のイオンをドープして選択的に第2の脆化層を形成する。第1の加熱処理では、第1の脆化層のみから第1の単結晶シリコン基板の一部をはく離し、第1の単結晶シリコン膜を形成する。第2の単結晶シリコン基板であって、第2の脆化層が形成されていない領域を除去し、第2の加熱処理では、第2の脆化層から第2の単結晶シリコン基板の一部をはく離し、第2の単結晶シリコン膜を形成する。

(もっと読む)

201 - 220 / 619

[ Back to top ]