Fターム[5F152NP02]の内容

再結晶化技術 (53,633) | 基板と活性層の間の層(バッファ層、マスク等)の材料 (2,042) | 半導体 (836) | 4族 (386)

Fターム[5F152NP02]の下位に属するFターム

Fターム[5F152NP02]に分類される特許

21 - 40 / 102

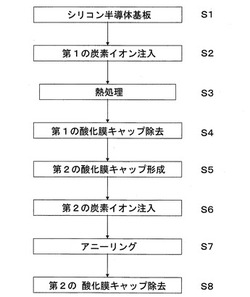

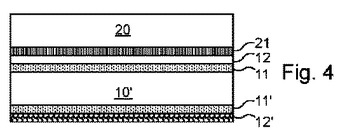

シリコン半導体基板の製造方法

【課題】単結晶炭化シリコン層からなる半導体基板を製造する技術に関し、特にシリコン基板の表層部がさらに応力緩和炭化シリコン層を有する半導体基板を製造する技術を提供する。

【解決手段】下記のステップ:(1)シリコン半導体基板を用意し(2)シリコン基板内に炭素イオンを注入してケイ素と炭素の混在した炭素含有層を形成するステップと(3)基板を熱処理して炭素含有層を応力緩和炭化シリコン膜層と酸化膜キャップを形成するステップと(4)酸化膜キャップを除去するステップと(5)第2の酸化膜キャップを形成するステップと(6)応力緩和炭化シリコン膜層と第2の酸化膜キャップとの間のシリコン層に炭素イオンを注入して、ケイ素と炭素の混在した炭素含有層を形成するステップと(7)基板を熱処理して炭素含有層を結晶成長炭化ケイ素膜層とするステップと(8)基板の表面に形成された酸化膜キャップを除去するステップを順次実施する。

(もっと読む)

半導体基板及び半導体基板の製造方法

【課題】半導体基板のアライメントマークを繰り返し使用する。

【解決手段】ベース基板にアライメントマークを形成する段階と、アライメントマークを形成する段階の後に、ベース基板上のアライメントマークを含む領域に、結晶成長を阻害する阻害層を形成する段階と、アライメントマークの位置を基準とする開口を形成すべき位置を示す情報に基づいて、阻害層におけるアライメントマークが設けられていない領域に、ベース基板を露出する開口を形成する段階と、開口内に半導体結晶を成長させる段階とを備える半導体基板の製造方法を提供する。

(もっと読む)

半導体基板、電子デバイスおよび半導体基板の製造方法

【課題】シリコン基板を用いてGaAs系の良質な半導体結晶膜を形成する。

【解決手段】第1領域と第2領域とを表面に有する基板と、前記第1領域の上方に形成された第1半導体と、を含み、前記基板は、表面がSixGe1−x(0≦x≦1)であり、前記第1領域は、前記第2領域により囲まれ、前記第1半導体は、砒素を含有する3−5族化合物半導体であり、単結晶であり、且つ前記SixGe1−xと格子整合または擬格子整合し、前記第2領域は、前記第1領域とは性状が異なる半導体基板を提供する。

(もっと読む)

半導体基板、電子デバイス、半導体基板の製造方法及び電子デバイスの製造方法

【課題】半導体基板、電子デバイス、半導体基板の製造方法及び電子デバイスの製造方法を提供する。

【解決手段】シリコンに不純物原子が導入された不純物領域104を有するベース基板102と、不純物領域104に接して設けられている複数のシード体112と、複数のシード体112の各々に接して設けられ、複数のシード体112の各々とそれぞれ格子整合または擬格子整合する複数の化合物半導体114とを備える半導体基板100。当該半導体基板100は、ベース基板102上に設けられ、不純物領域104の少なくとも一部を露出する複数の開口が設けられた阻害体をさらに備えてもよい。

(もっと読む)

炭化シリコン膜の製造方法

【課題】緻密で均一な膜厚であり、しかも所望の膜厚の炭化シリコン膜を得ることができ、かつ低コストや大口径化が可能な炭化シリコン膜の製造方法を提供する。

【解決手段】本発明の炭化シリコン膜13の製造方法は、基板11上にアモルファスシリコンとポリシリコンとの少なくとも一方を含むシリコン膜14を形成する工程と、シリコン膜14を炭化処理し、炭化された膜を含んだ炭化シリコン膜13を形成する工程と、を有することを特徴とする。

(もっと読む)

炭化シリコン膜の製造方法

【課題】エッチングが困難な炭化シリコン膜をエッチングすることなく、一つのチップに炭化シリコンのデバイスとシリコンのデバイスを容易に混載させ、かつ、炭化シリコンのデバイスとシリコンのデバイスが電気的に絶縁された構造とすることが可能な炭化シリコン膜の製造方法を提供する。

【解決手段】本発明の炭化シリコン膜13の製造方法は、基板11上に下地層12を形成する工程と、下地層12上にシリコン膜を形成する工程と、シリコン膜をパターニングするパターニング工程と、パターニング工程の後にシリコン膜を炭化処理し、炭化された膜を含んだ炭化シリコン膜13を形成する工程と、炭化シリコン膜13をマスクに用いて、マスクが形成されていない領域の下地層12をエッチングする工程と、を有することを特徴とする。

(もっと読む)

半導体薄膜素子の製造方法並びに半導体ウエハ、及び、半導体薄膜素子

【課題】Si結晶層上に半導体素子を備えたSi以外の半導体単結晶層を備えた半導体薄膜素子の製造方法並びに半導体ウエハ、及び、半導体薄膜素子を提供する。

【解決手段】Si(111)基板(第1の基板)101の表面にバッファ層102と半導体単結晶層103とを順次形成する第1の工程と、半導体単結晶層101aとバッファ層102aとSi(111)基板の所定の厚さ部分102bとを含む分離島150を形成する第2の工程と、分離島の表面を覆う被覆層200を形成する第3の工程と、被覆層をマスクに前記Si(111)基板をSi(111)面に沿ってエッチングして剥離する第4の工程と、分離島の剥離面を別の基板(第2の基板)201の表面に接合する第5の工程とを備える。

(もっと読む)

半導体基板、半導体基板の製造方法、電子デバイス、および電子デバイスの製造方法

【課題】結晶薄膜を有する半導体基板の設計および上記結晶薄膜の膜質および膜厚の制御を容易にできる半導体基板を提供する。

【解決手段】ベース基板と、ベース基板上に、一体にまたは分離して設けられ、化合物半導体の結晶成長を阻害する阻害層とを備え、阻害層は、ベース基板まで阻害層を貫通する複数の開口を有する複数の第1開口領域を有し、複数の第1開口領域のそれぞれは、内部に同一の配置で設けられた複数の第1開口を含み、複数の第1開口の一部は、電子素子が形成されるべき第1化合物半導体が設けられている第1素子形成開口であり、複数の第1開口の他の一部は、電子素子が形成されない第1ダミー開口である半導体基板を提供する。

(もっと読む)

半導体基板の製造方法及び半導体基板

【課題】良好な立方晶の炭化珪素膜を形成可能な半導体基板の製造方法及び半導体基板を提供すること。

【解決手段】シリコン基板11の上面に多孔質な多孔質シリコン層12を形成する工程と、水素ガス及び炭化水素系ガスの混合ガスまたは炭化水素系ガスを供給し、多孔質シリコン層12の表面を結晶化及び炭化して炭化珪素膜13を形成する工程と、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】大きな歪み量を発生可能な半導体装置およびその製造方法を提供する。

【解決手段】半導体装置の製造方法は、CとCの濃度の10倍以上のGeとを含んだSiGeC層を形成する工程(S3)と、SiGeC層内のCのうちで格子置換位置に位置しているものを格子間位置へと移動させることによって、前記SiGeC層内の全てのCに対する格子置換位置に位置するCの割合を形成された時点での割合から低下させて50%以下に低下させる工程(S4)と、を含む。

(もっと読む)

ダイヤモンド半導体及び作製方法

【課題】従来技術と比較して、室温で十分に高いキャリア濃度を有するダイヤモンド半導体及び作製方法を提供すること。

【解決手段】ダイヤモンド基板11(図5(a))上にマイクロ波プラズマCVD装置を用い、メタンを反応ガスとし、基板温度700℃でダイヤモンド薄膜12を1ミクロン積層する(図5(b))。ダイヤモンド薄膜12にイオン注入装置を用い、不純物1(VI族又はII族元素)を打ち込む(図5(c))。その後、不純物2(III族又はV族元素)を打ち込んだが(図5(d))、注入条件は、打ち込んだ不純物がそれぞれ表面から0.5ミクロンの厚さの範囲内で、1×1017cm-3となるようにシミュレーションにより決定した。その後、2種類のイオンが注入されたダイヤモンド薄膜13をアニールすることにより(図5(e))、イオン注入された不純物の活性化を行い、ダイヤモンド半導体薄膜15を得た(図5(f))。

(もっと読む)

電界効果トランジスタ

【課題】歪みチャネルを用いた場合のリーク電流を低減することができ、不良の発生を抑制して歩留まりの向上をはかる。

【解決手段】半導体基板10上に設けられた、基板10とは格子定数の異なる合金半導体からなる下地層20と、下地層20上に設けられた、下地層20とは格子定数が異なり、チャネル長方向及びチャネル幅方向の一方に引っ張り応力、他方に圧縮応力が付与されたチャネル半導体層30と、チャネル半導体層30を挟むように下地層20上に設けられたソース・ドレイン領域60,70と、チャネル半導体層30上にゲート絶縁膜40を介して設けられたゲート電極50とを備えた電界効果トランジスタであって、下地層20は、ソース・ドレイン領域60,70の下部に形成される空乏層61,71が下地層20内に収まる厚さよりも厚く形成され、且つ熱平衡臨界膜厚よりも薄く形成されている。

(もっと読む)

半導体基板の製造方法、および半導体基板

【課題】改善された光子/電子の変換効率を備える半導体基板を製造する方法を提供する。

【解決手段】本発明は、半導体基板の製造方法に関する。当該方法は、絶縁型基板上に第1の半導体層(7)を設けるステップと、拡散バリア層(9)を設けるステップと、第2の半導体層(11)を設けるステップとを備える。拡散バリア層を設けることにより、高ドープされた第1の半導体層から第2の半導体層への拡散を抑制することが可能になる。本発明はまた、これに相当する半導体基板、および当該基板を備えるオプトエレクトロニクスデバイスに関する。

(もっと読む)

ダイアモンド層を有する窒化ガリウム層の製造

一態様における方法は、第1熱伝導率を有する第1ダイアモンド層と、第1熱伝導率よりも高い第2熱伝導率を有する第2ダイアモンド層とを有する窒化ガリウム(GaN)層を製造するステップを含む。この製造するステップは、第2ダイアモンド層を第1ダイアモンド層上に堆積させるために、マイクロ波プラズマ化学蒸着(CVD)プロセスを用いるステップを含む。 (もっと読む)

マイクロエレクトロニクス分野において単結晶膜を形成する方法

所定の材料の薄膜を形成する方法は次の工程を含む:表面上に上記所定の材料のアモルファスおよび/または多結晶膜12を有する第1の基板10が準備される;この第1の基板に疎水性直接結合(分子付着)によって、第2の基板20が結合され、上記第2の基板は、その表面上に所定の結晶配向の単結晶参照膜21を有する;少なくとも、アモルファスおよび/または多結晶膜に熱処理が適用され、上記熱処理は、このアモルファスおよび/または多結晶膜12の少なくとも一部に参照膜21の結晶配向に沿って固相再結晶を受けさせるように設計され、この参照膜は再結晶種として機能を果たす;少なくとも部分的に再結晶された膜は、参照膜の少なくとも一部から分離される。  (もっと読む)

(もっと読む)

半導体基板及びその製造方法

【課題】歪みが緩和されたバッファ層を形成し、そのバッファ層上に窒化ガリウム層を形成することにより、低コストで、反りやクラックの抑制された窒化ガリウム層を有する半導体基板及びその製造方法を提供することを目的とする。

【解決手段】面方位が(111)のSOI層を有するSOI基板を準備する工程と、SOI基板のSOI層上にバッファ層を形成する工程と、形成されたバッファ層上に窒化ガリウム層を形成する工程とを含む半導体基板の製造方法であって、窒化ガリウム層を形成する工程より前に、SOI基板のSOI層中にイオン注入により歪み緩衝層を形成する工程を有する半導体基板の製造方法を提供する。

(もっと読む)

半導体基板、半導体基板の製造方法および電子デバイス

【課題】化合物半導体デバイスのスイッチング速度等の性能を向上する。

【解決手段】シリコン基板と、シリコン基板の上に形成された絶縁膜であってシリコン基板に達する開口部を有する絶縁膜と、開口部に形成されたGe結晶と、Ge結晶を核として成長された化合物半導体結晶であって絶縁膜の表面より凸に形成されたシード化合物半導体結晶と、シード化合物半導体結晶の特定面をシード面として、絶縁膜の上にラテラル成長されたラテラル成長化合物半導体層と、を備えた半導体基板を提供する。

(もっと読む)

窒素化合物半導体基板の製造方法および窒素化合物半導体基板

【課題】結晶性のよい窒素化合物半導体層が得られ、しかも低コストで生産性のよい窒素化合物半導体基板の製造方法を提供する。

【解決手段】所定厚さの表面Si層3と埋め込み絶縁層4とを有するSi基板1を準備する工程と、上記Si基板1を炭素系ガス雰囲気中で加熱して上記表面Si層3を単結晶SiC層6に変成させる際に、上記埋め込み絶縁層4との界面8近傍のSi層を残存Si層5として残す工程と、表面の単結晶SiCに対してさらに窒素化合物半導体層15をエピタキシャル成長させる工程とを行なう。

(もっと読む)

炭化珪素半導体基板およびその製造方法

【課題】炭化珪素エピタキシャル層中の基底面転位を減らすことができる炭化珪素半導体基板とその製造方法を提供する。

【解決手段】半導体装置の構成要素が作りこまれるための層であるドリフト層となる第1の半導体層と,炭化珪素単結晶ウエハからなる下地基板の間に,ドリフト層と同一伝導型の2層以上の半導体層によって構成されるバッファ層をエピタキシャル成長によって設ける。ドリフト層とこのバッファ層の界面,バッファ層を構成する半導体層間の界面,前記バッファ層と下地基板の界面においてドナー濃度の段差を設け,ドリフト層側の方が下地基板側よりもドナー濃度が低くなるようにするすることにより,ドリフト層が単層であるよりも,あるいは,1層からなるバッファ層を設けるよりも,多くの基底面転位を貫通刃状転位に変換することができる。

(もっと読む)

エピタキシャル成長のための基板の作成方法

【課題】本発明は、補助基板上に緩和エピタキシャルベース層を得ることを含む、エピタキシャル成長のための基板の作製方法に関する。本発明の目的は、望ましい格子パラメータを有する材料が、異なる格子パラメータを有する別の材料の上で、より効率的に、熱力学的及び結晶学的に高い安定性を有してエピタキシャル成長することを可能にする基板を作ることにある。

【解決手段】この目的は、上記のタイプの方法であって、エピタキシャルベース層の少なくとも一部をキャリア基板上に移してベース基板を形成することと;エピタキシャルベース層の材料をキャリア基板上でさらに成長させることとをさらに含む方法により達成される。

(もっと読む)

21 - 40 / 102

[ Back to top ]