Fターム[5F152NP03]の内容

再結晶化技術 (53,633) | 基板と活性層の間の層(バッファ層、マスク等)の材料 (2,042) | 半導体 (836) | 4族 (386) | Si (99)

Fターム[5F152NP03]に分類される特許

1 - 20 / 99

III族窒化物半導体デバイスの製造方法

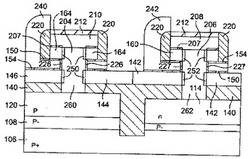

CMOS垂直置換ゲート(VRG)トランジスタ

【課題】本発明は、CMOS垂直置換ゲート(VRG)トランジスタを提供する。

【解決手段】集積回路構造は平面に沿って形成された主表面を有する半導体領域及び表面中に形成された第1及び第2のソース/ドレインドープ領域を含む。絶縁トレンチが第1及び第2のソース/ドレイン領域間に形成される。第1のソース/ドレイン領域とは異なる伝導形のチャネルを形成する第3のドープ領域が、第1のソース/ドレイン領域上に配置される。第4のドープ領域が第2のソース/ドレイン領域上に形成され、第2のソース/ドレイン領域とは相対する伝導形をもち、チャネル領域を形成する。第5及び第6のソース/ドレイン領域が、それぞれ第3及び第4のドープ領域上に形成される。

(もっと読む)

窒化物半導体結晶層の製造方法及び窒化物半導体結晶層

【課題】より良質な窒化物半導体結晶層を製造する方法及び窒化物半導体結晶層を提供する。

【解決手段】実施形態によれば、表面にシリコン酸化膜が形成された基体の上に設けられた20μm以下の厚さのシリコン結晶層の上に、1μm以上の厚さの窒化物半導体結晶層を形成する。シリコン結晶層の上に、窒化物半導体結晶層のうちの第1の部分を形成した後、第1の部分よりも高い温度で第2の部分を形成する。シリコン結晶層は、シリコン結晶層の層面に対して平行な面内において、0.5mm以上、10mm以下の特性長さを持つ島状に区分されている。区分されたシリコン結晶層のそれぞれの上に選択的に互いに離間した複数の窒化物半導体結晶層を形成する。シリコン結晶層の少なくとも一部を窒化物半導体結晶層に取り込ませ、シリコン結晶層の厚さを減少させる。

(もっと読む)

半導体基板及びその製造方法

【課題】単純な単結晶シリコン基板を出発基板として窒化ガリウム膜を形成することができ、反りやクラックが抑制された半導体基板及びその製造方法を提供する。

【解決手段】半導体基板10は、単結晶シリコン基板11と、単結晶シリコン基板11の表面に形成された炭素含有シリコン層12と、炭素含有シリコン層12の表面に形成されたバッファ層13と、バッファ層13の表面に形成された窒化ガリウム膜14とを備えている。炭素含有シリコン層12に含まれる炭素の濃度は1E+18atoms/cm3以上1E+21atoms/cm3以下であり、例えば単結晶シリコン基板11をプロパンガス雰囲気下で熱処理することにより形成される。

(もっと読む)

半導体装置

【課題】本発明は、曲面を有する基材に被剥離層を貼りつけた半導体装置およびその作製方法を提供することを課題とする。特に、曲面を有するディスプレイ、具体的には曲面を有する基材に貼りつけられたOLEDを有する発光装置、曲面を有する基材に貼りつけられた液晶表示装置の提供を課題とする。

【解決手段】本発明は、基板上に素子を含む被剥離層を形成する際、素子のチャネルとして機能する領域のチャネル長方向を全て同一方向に配置し、該チャネル長方向と同一方向に走査するレーザー光の照射を行い、素子を完成させた後、さらに、前記チャネル長方向と異なっている方向、即ちチャネル幅方向に湾曲した曲面を有する基材に貼り付けて曲面を有するディスプレイを実現するものである。

(もっと読む)

基板製造方法及び該方法によって得られた基板

【課題】活性材料要素をしじたいに移し替えるコストを低減する。

【解決手段】第1の材料から成る活性要素の表面上における支持体2への接合対象部位に非晶質材料6を蒸着する工程を備え、第2の材料が第1の材料よりも希少ではないことを特徴とする。更に、特に光学、電子工学又は光電子工学用の基板を製造する際に第1の材料から成る活性要素8を第2の材料から成る支持体2の表面に接合する操作を行う基板製造方法にも関する。この方法は、活性要素8又は支持体2が少なくともその表面上の接合対象部位に多結晶材料を含み、接合に先立ち、この多結晶材料を含む表面上に非晶質材料6の層を形成することを特徴とする。

(もっと読む)

エピタキシャルウェーハおよびその製造方法

【課題】デバイス活性層へのオートドーピングやミスフィット転位が発生し難く、且つ、デバイス形成後に薄厚化されても不純物金属によるデバイス活性層の汚染を有効に抑制することができるエピタキシャルウェーハおよびその製造方法を提供する。

【解決手段】シリコン基板の表面から内部に向かってV族原子を拡散させて形成した、濃度:2×1013atoms/cm3以上1×1018atoms/cm3以下のV族原子を含有してシリコン基板の表層に位置するバリア層と、バリア層上に形成したシリコンエピタキシャル膜よりなるデバイス活性層とを備えることを特徴とするエピタキシャルウェーハである。また、バリア層形成工程と、デバイス活性層形成工程とを含むエピタキシャルウェーハの製造方法である。

(もっと読む)

半導体積層体とこれを含むHFETおよびそれらの製造方法

【課題】半導体積層体に含まれるチャネル層下の化合物半導体層を不純物ドーピングでp型化することなく、その半導体積層体を含むHFETのリーク電流の低減や耐電圧の向上などを可能とする。

【解決手段】半導体積層体は、基板(11)上において順次堆積された第1、第2および第3の化合物半導体層(13、14、15)を少なくとも含み、その第1化合物半導体層(13)の少なくとも部分的層(16)は非晶質に改質されており、第2化合物半導体層(14)は第1化合物半導体層(13)に比べて小さなバンドギャップを有して光吸収層として作用し得る。

(もっと読む)

微結晶シリコン膜の作製方法および薄膜トランジスタの作製方法

【課題】絶縁膜と微結晶シリコン膜との密着性を向上させた微結晶シリコン膜の作製方法を提供する。

【解決手段】絶縁膜55上に、後のプラズマ酸化等により完全に酸化される高さ(例えば0nmより大きく5nm以下)の微結晶シリコン粒、または後のプラズマ酸化等により完全に酸化される膜厚(例えば0nmより大きく5nm以下)の微結晶シリコン膜もしくはアモルファスシリコン膜を形成し、前記微結晶シリコン粒または前記微結晶シリコン膜もしくはアモルファスシリコン膜に酸素を含むプラズマ処理またはプラズマ酸化を施すことにより、前記絶縁膜上に酸化シリコン粒57aまたは酸化シリコン膜を形成し、前記酸化シリコン粒または前記酸化シリコン膜の上に微結晶シリコン膜59を形成する微結晶シリコン膜の作製方法である。

(もっと読む)

炭化珪素基板、半導体装置、炭化珪素基板の製造方法

【課題】炭化珪素基板を用いた半導体装置の製造コストの低減を実現可能な炭化珪素基板、半導体装置および炭化珪素基板の製造方法を提供する。

【解決手段】炭化珪素基板1は、炭化珪素からなるベース層10と、単結晶炭化珪素からなり、ベース層10上に配置され、ベース層10よりも不可避不純物の濃度が低いSiC層20と、炭化珪素からなり、ベース層10の、SiC層20とは反対側の主面10D上に形成され、ベース層10よりも不可避不純物の濃度が低い被覆層90とを備えている。

(もっと読む)

半導体装置の製造方法

【課題】解像度限界より小さい寸法のパターンを規則的に形成する半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、構造体としての第1及び第2のパターン13a、13b間に露出する種結晶としての半導体基板10からエピタキシャル結晶としての単結晶膜14を形成し、単結晶膜14を単結晶膜14の融点以下の温度で加熱することにより単結晶膜14を流動させ、流動した単結晶膜14が凝集することにより複数の凝集体15を第1及び第2のパターン13a、13b間に形成することを含む。

(もっと読む)

半導体複合体構造を形成する方法

【課題】 パターン付けされたシリコン・オン・インシュレータ(SOI)/シリコン・オン・ナッシング(SON)複合構造体を多孔性Si技術によって形成すること。

【解決手段】 パターン付けされたSOI/SON複合構造体及びその形成方法を提供する。SOI/SON複合構造体においては、パターン付けされたSOI/SON構造体が、Siオーバーレイヤと半導体基板の間に挟まれる。パターン付けされたSOI/SON複合構造体を形成する方法は、SOI及びSON構造が共に形成される共有加工処理ステップを含む。本発明はまた、埋没導電/SON構造体を含む複合構造体の形成方法、及び、埋没ボイド平面だけを有する複合構造体の形成方法を提供する。

(もっと読む)

半導体基板の製造方法および半導体デバイスの製造方法

【課題】シリコンデバイス等耐熱性の低い部位がSi基板に設けられた場合でも、Ge結晶に熱アニールを施し、十分な結晶品質のGe結晶薄膜を得る。

【解決手段】表面がSiであるベース基板と、前記ベース基板の上に形成され、組成がCxSiyGezSn1−x−y―z(0≦x<1、0≦y<1、0<z≦1、かつ、0<x+y+z≦1)である第1結晶層と、前記第1結晶層が形成された部分以外の前記ベース基板の上に形成された第1半導体素子と、を有する半導体基板の製造方法であって、前記第1半導体素子には電磁波を照射することがなく、前記第1結晶層の一部または全部に電磁波を照射する工程を有する半導体基板の製造方法を提供する。

(もっと読む)

ボンディング層が消滅する間接ボンディング

【課題】支持基板に直接に接着することができない半導体材料によるSeOI構造を形成する方法を提供する。

【解決手段】下部層1及び上部層2を備える半導体ドナー基板が使用され、上部層2の材料の元素の拡散を受け入れる材料のボンディング層3を上部層2上に形成する工程と、そのボンディング接着を確実に行うためにボンディング層3を洗浄する工程と、あらかじめ上部層2上に形成され、そして、洗浄されたボンディング層3の側から、支持基板20に対してドナー基板を接着する工程と、この上部層2から元素をボンディング層3中に拡散して、このボンディング層及び上部層中の上記元素の濃度を均一化し、均一な薄層を支持基板20の表面上に形成する工程とを備える。

(もっと読む)

結晶シリコンの少なくとも一つの極薄層を含む多層膜を製造する方法及び前記方法により得られたデバイス

【課題】 結晶シリコンの少なくとも一つの極薄層を含む多層膜を製作する、単純で負担がより少ない方法を提案すること。

【解決手段】 本発明は結晶シリコンの少なくとも一つの極薄層を有する多層膜を製作する方法に関し、前記膜は、結晶構造を有し、予め洗浄された表面を含む基板から製作される。本発明によれば、前記方法は前記洗浄された表面をSiF4、水素、及びアルゴンのガス混合物内で生成されたRFプラズマに当て、それにより前記基板に接触して微小空洞を含有する界面副層を備える結晶シリコンの極薄層を形成するステップa)と、結晶シリコンの前記極薄層上に少なくとも1層の材料を堆積させ、それにより少なくとも一つの機械的に強い層を含む多層膜を形成するステップb)と、前記多層膜で覆われた前記基板を400℃より高い温度でアニールし、それにより前記多層膜を前記基板から分離させるステップc)とを含む。

(もっと読む)

Ge膜付きSOI基板の製造方法及びGe膜付きSOI基板

【課題】引っ張り応力を高めたGe膜を有する基板を提供する。

【解決手段】絶縁性基板である石英基板又はガラス基板上に、シリコン薄膜を備えるSOI基板を用意する工程と、ゲルマニウムを上記SOI基板のシリコン薄膜の上にエピタキシャル成長させてゲルマニウム膜を形成する工程とを少なくとも含んでなるGe膜付きSOI基板の製造方法を提供する。また、絶縁性基板である石英基板又はガラス基板上のシリコン薄膜を備えるSOI基板と、上記SOQ基板のシリコン薄膜の上にエピタキシャル成長させたゲルマニウム膜を備える半導体用Ge膜付きSOI基板を提供する。

(もっと読む)

半導体薄膜素子の製造方法並びに半導体ウエハ、及び、半導体薄膜素子

【課題】Si結晶層上に半導体素子を備えたSi以外の半導体単結晶層を備えた半導体薄膜素子の製造方法並びに半導体ウエハ、及び、半導体薄膜素子を提供する。

【解決手段】Si(111)基板(第1の基板)101の表面にバッファ層102と半導体単結晶層103とを順次形成する第1の工程と、半導体単結晶層101aとバッファ層102aとSi(111)基板の所定の厚さ部分102bとを含む分離島150を形成する第2の工程と、分離島の表面を覆う被覆層200を形成する第3の工程と、被覆層をマスクに前記Si(111)基板をSi(111)面に沿ってエッチングして剥離する第4の工程と、分離島の剥離面を別の基板(第2の基板)201の表面に接合する第5の工程とを備える。

(もっと読む)

半導体基板の製造方法及び半導体基板

【課題】良好な立方晶の炭化珪素膜を形成可能な半導体基板の製造方法及び半導体基板を提供すること。

【解決手段】シリコン基板11の上面に多孔質な多孔質シリコン層12を形成する工程と、水素ガス及び炭化水素系ガスの混合ガスまたは炭化水素系ガスを供給し、多孔質シリコン層12の表面を結晶化及び炭化して炭化珪素膜13を形成する工程と、を備える。

(もっと読む)

3次元集積回路装置及びその製造方法

【課題】ガラス基板上に薄膜半導体層を形成した3次元集積回路装置を提供する。

【解決手段】ガラス基板11上に、単結晶もしくは準単結晶の2層の薄膜半導体層13,16が層間絶縁層14を介して積層され、2層の薄膜半導体層13,16は、下層の第1層の薄膜半導体層13と上層の第2層の薄膜半導体層16とが異なる材料であり、2層の薄膜半導体層13,16が、層間絶縁層14に形成された開口内を埋めて形成された、エピタキシャル層15によって接続され、エピタキシャル層15の表面部は、第2層の薄膜半導体層16と同じ材料の層であり、第1層の薄膜半導体層13及び第2層の薄膜半導体層16のうち、1層以上に能動素子Tr21,Tr22が形成されている3次元集積回路装置10を構成する。

(もっと読む)

半導体製造方法

【課題】ガラス上に高効率な薄膜多結晶シリコン(Si)太陽電池を実現することを目的とした半導体製造方法。

【解決手段】半導体励起(ダイオード励起)された固体連続波レーザーを利用して(110)と(111)に配向制御した大粒径多結晶シリコン(Si)薄膜をガラス上に形成し、このSi膜を種(シード)結晶として多結晶Si層を直接成長する。

その後、本薄膜に対してSi層が溶融しない条件でエネルギービームを照射してSiの固相成長を行うことを特徴とした太陽電池用半導体製造方法。

(もっと読む)

1 - 20 / 99

[ Back to top ]