Fターム[5F152NP02]の内容

再結晶化技術 (53,633) | 基板と活性層の間の層(バッファ層、マスク等)の材料 (2,042) | 半導体 (836) | 4族 (386)

Fターム[5F152NP02]の下位に属するFターム

Fターム[5F152NP02]に分類される特許

61 - 80 / 102

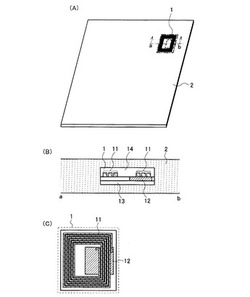

半導体装置を内包する用紙およびその作製方法

【課題】無線で通信可能な半導体装置を抄き込んだ用紙であり、半導体装置を内包する部分の凹凸が目立たなく、しかも厚さ130μm以下の薄い紙を実現する。

【解決手段】半導体装置1は回路部12とアンテナ11を具備し、回路部12は薄膜トランジスタで構成される。回路部12とアンテナ11は製造時に使用した基板から分離され、可撓性基材13と封止層14とで挟まれ保護されている。半導体装置1は撓ませることが可能であり、半導体装置1自体の厚みは30μm以下である。半導体装置1は紙2の抄紙工程で抄き込まれる。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の不具合を抑制しながらキャリアの移動度を高くすることができる半導体装置及びその製造方法を提供する。

【解決手段】溝8内にp型のSiGe混晶層49aがエピタキシャル成長法により形成され、その上にp型のSiGe混晶層49bがエピタキシャル成長法により形成されている。更に、SiGe混晶層49b上にp型のSiGe混晶層49cがエピタキシャル成長法により形成されている。なお、SiGe混晶層49aの最表面の溝8の底からの高さa4は、シリコン基板1の表面を基準としたときの溝8の深さよりも低い。また、SiGe混晶層49bの最表面の溝8の底からの高さb4は、シリコン基板1の表面を基準としたときの溝8の深さよりも高い。更に、SiGe混晶層49a及び49c中のGe濃度は、SiGe混晶層49b中のGe濃度より低い。

(もっと読む)

半絶縁エピタキシー上の炭化ケイ素および関連ワイドバンドギャップトランジスタ

半絶縁エピタキシャル層を製造する方法は、基板の表面上あるいは第1のエピタキシャル層の表面上にホウ素注入領域を形成するために、基板あるいは基板上に形成された第1のエピタキシャル層にホウ素イオンを注入すること、および半絶縁エピタキシャル層を形成するために基板のホウ素注入領域上あるいは第1のエピタキシャル層のホウ素注入領域上に第2のエピタキシャル層を成長させることを含む。

(もっと読む)

(もっと読む)

半導体基板、半導体基板の製造方法、固体撮像素子及び固体撮像素子の製造方法

【課題】リーク電流が少なく酸化膜耐圧が高い半導体装置を高い歩留で形成することができる半導体基板、そのような半導体基板の製造方法、暗電流や白キズ個数が少ない固体撮像素子及びその製造方法を提供する。

【解決手段】シリコン基板101と、シリコン基板101上に配されたゲッタリング層102と、ゲッタリング層102上に配された、素子形成領域を有する素子形成層103とを備え、ゲッタリング層102は、シリコン、ゲルマニウム及び炭素を主成分とする混晶102aと混晶102a中に点在する炭化シリコン微結晶102bとからなり、混晶102a及び素子形成層103は、シリコン基板101に格子整合している。

(もっと読む)

埋め込みカーボン・ドーパントを用いた半導体デバイス

【課題】 電荷移動度の低下とデバイス性能の低下とをもたらすミスフィット転位の形成を減少させる。

【解決手段】 半導体構造体、及び、半導体デバイス、より具体的にはN型FETデバイスを製造する方法である。本デバイスは、構造体におけるミスフィット転位の発生及び伝播を減少させる層間の界面の材料を介して応力誘発層の上に設けられる応力受容層を含む。応力受容層はシリコン(Si)であり、応力誘発層はシリコン・ゲルマニウム(SiGe)であり、材料は、デバイスを形成する間に両層をドープすることによって与えられるカーボンである。カーボンは、SiGe層全体にわたってドープすることもできる。

(もっと読む)

立方晶系単結晶炭化シリコン基板の製造方法

【課題】炭化シリコンのみからなる自立型で、欠陥が少なく結晶性に優れた立方晶系単結晶炭化シリコン基板を作製する。

【解決手段】シリコン基板2と埋め込み絶縁膜3と表面シリコン膜4とからなるSOI基板1を製造開始時に準備された材料として、表面シリコン膜4を炭化処理して単結晶炭化シリコン膜5に変成し、単結晶炭化シリコン膜5の上にエピタキシャル成長法により単結晶炭化シリコン膜6を形成し、単結晶炭化シリコン膜6の上に気相成長法により非晶質炭化シリコン膜7を形成し、シリコン基板2と埋め込み絶縁膜3を除去し、基板を加熱して非晶質炭化シリコン膜7を単結晶化し、単結晶炭化シリコン膜5,6と非晶質炭化シリコン膜7を単結晶化して生成した単結晶炭化シリコン膜とからなる積層構造を立方晶系単結晶炭化シリコン基板とする。

(もっと読む)

SiC半導体およびその製造方法

【課題】Si単結晶基板上に、格子不整合による欠陥発生が抑制され、結晶性に優れた高品質な3C−SiC単結晶層を備えたSiC半導体、および、このような3C−SiC単結晶層を簡便に形成することができるSiC半導体の製造方法を提供する。

【解決手段】少なくとも表面に、ホウ素が1020atoms/cm3以上固溶しているSi単結晶基板上に、670℃以上850℃以下で3C−SiC低温成長層をエピタキシャル成長させた後、昇温し、前記3C−SiC低温成長層の上に、3C−SiC単結晶層をエピタキシャル成長させることにより、Si単結晶基板上に3C−SiC単結晶層を備えたSiC半導体を得る。

(もっと読む)

半導体基板及びその製造方法

【課題】 量産性の高い、欠陥の充分少ない高品質なSSOI基板を提供する。

【解決手段】 半導体基板の製造方法は、支持基板とは格子定数の異なるヘテロエピタキシャル層、絶縁層、Si層が順に積層された構造を少なくとも含む支持基板に、前記Si層の歪みを変化させるために、前記ヘテロエピタキシャル層の応力を変化させる工程を行なう。

(もっと読む)

半導体基板及びその製造方法

【課題】 欠陥の充分少ない高品質な歪みSi基板を提供する。

【解決手段】 半導体基板の製造方法は、支持基板とは格子定数の異なるヘテロエピタキシャル層、多孔質層、Si層が順に積層された構造を少なくとも含む支持基板に、前記Si層の歪みを変化させるために、前記ヘテロエピタキシャル層の応力を変化させる工程を行なう。

(もっと読む)

半導体層構造及び半導体層構造の製造方法

【課題】半導体材料の応力及び亀裂のない堆積のための基板と、かかる基板の製造方法を提供する。

【解決手段】半導体層構造の製造方法にあたり、a)半導体材料からなる基板を準備し、b)前記基板上に第二の半導体材料からなる層を施与して、半導体構造を作製し、c)該半導体層構造中に軽ガスイオンを注入して、半導体層構造内に空洞を含む層を作製し、d)前記空洞を規定種の不純物原子によって安定化し、e)該半導体層構造上に少なくとも1層のエピタキシャル層を施与する。

(もっと読む)

半導体積層体の形成方法

【課題】本願の目的は、Si基板上に結晶性と表面モフォロジーの良い単結晶SiC層を形成することにある。

【解決手段】本願の骨子は、Si層上にSiやSiCよりも融点の低いSiGe層と非晶質SiCを形成し、これら積層構造をSiGeの融点以上に加熱することにより、SiCとSi基板の間の歪みを緩和し、同時に非晶質SiCからの結晶化を行うことで、結晶性と表面諸フォジーが良好な単結晶SiC層を形成する。

(もっと読む)

半導体基板の製造方法及び半導体装置の製造方法

【課題】半導体基板に汚染物質が付着することを抑えトランジスタの特性を劣化させることなく製造することができる半導体基板の製造方法及び半導体装置の製造方法を提供する。

【解決手段】半導体基板41の製造方法は、シリコン基板11上におけるSOI素子形成領域13のみに、シリコンバッファ層18及びシリコンゲルマニウム層15が成長する条件でエピタキシャル成長させる。次に、シリコン基板11上の全面にシリコン層16を成長させる。そのあと、シリコンゲルマニウム層15に代えて埋め込み絶縁層31を埋め込む。これにより、引き続く工程において、シリコン基板11上に汚染の原因であるシリコンゲルマニウム層15が残ることを少なくすることができ、処理を行う炉の中にゲルマニウムが広がることを抑えることが可能となる。

(もっと読む)

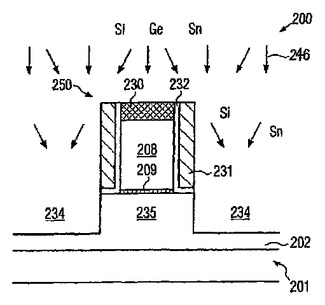

高共有半径の原子を含む埋め込まれた半導体層を利用したシリコンベースのトランジスタに歪みを生成する技術

共有半径が大きくされた原子種、例えば少なくとも一部が置換されたゲルマニウム、を導入することにより、ゲルマニウムの集塊化ならびに格子の欠陥による応力緩和のリスクを低減することができる、非常に実効的な歪みのメカニズムが提供される。錫などの、半径が増加した原子種は、水素化錫に基づくエピタキシャル成長技術により、容易に導入することができる。  (もっと読む)

(もっと読む)

半導体素子および半導体素子製造方法

【課題】 単結晶基板上のSiC緩衝層を用いてその上に結晶欠陥の少ない結晶性に優れるIII族窒化物半導体層を形成することができ、発光特性や高周波特性を向上させることができるようにする。

【解決手段】 本発明は、単結晶からなる基板101と、その単結晶基板101の表面に設けられた炭化珪素層102と、その炭化珪素層102の表面に設けられたIII族窒化物半導体からなる介在層103とを備えた半導体素子10において、炭化珪素層102は、化学量論的に珪素を富裕に含む立方晶からなり、表面が(3×3)構造の再配列構造を有するものである。

(もっと読む)

電力用途へのウェハーボンディングを介して得られた多層基板

多層半導体装置は、ウェハーボンディングを介して移行させた単結晶膜の電気的特性を有する多結晶基板の良好な熱的及び電気的特性を利用している。装置構造は、研磨された多結晶、例えば炭化シリコン基板を含む。シリコンの平坦化層が表面に形成され、続いて化学的機械研磨される。次いで、基板は、バルクリシコンウェハー又はsilicon-on-insulator(SOI)ウェハーに結合される。シリコン(SOI)ウェハーは所望厚さに薄肉化される。 (もっと読む)

機能性膜含有構造体、及び、機能性膜の製造方法

【課題】 成膜基板上に形成された機能性膜を、成膜基板から容易に剥離することができる剥離方法を含む機能性膜の製造方法を提供する。

【解決手段】 基板上に分離層を形成する工程(a)と、分離層上に、機能性材料を用いて形成される機能性膜を含む被剥離層を形成する工程(b)と、分離層に外力を与えて分離層の層内又は界面に割れを生じさせることにより、被剥離層を基板から剥離し、又は、被剥離層と基板との接合強度を低下させる工程(c)とを含む。

(もっと読む)

半導体装置の作製方法

【課題】低コストで信頼性の高い半導体装置の作製方法を提供する。

【解決手段】基板上に金属膜を形成し、前記金属膜に酸素を含む雰囲気中でプラズマ処理を行うことにより、前記金属膜の表面に金属酸化膜を形成し、前記金属酸化膜上に下地膜を形成し、前記下地膜上に薄膜トランジスタを有する素子層を形成し、前記素子層上に保護層を形成し、前記金属膜、前記金属酸化膜、前記下地膜、前記素子層、及び前記保護層を選択的に除去して、開口部を形成し、前記基板から前記下地膜、前記素子層、及び前記保護層を分離し、可撓性を有する第1及び第2のフィルムを用いて前記下地膜、前記素子層、及び前記保護層を封止し、前記基板付近でのプラズマの電子密度は1×1011cm−3以上1×1013cm−3以下であり、電子温度は0.5eV以上1.5eV以下である。

(もっと読む)

積層層構造およびその形成方法

【課題】基板と、少なくとも2つの化合物AおよびBを含む材料の複数の層のスタックとから成る積層層構造の製造方法を提供する。

【解決手段】化合物Aが基板3上でホモエピタキシャル成長又はヘテロエピタキシャル成長が十分にできるような結晶構造を有し、スタック5の層の少なくとも一部は、xが0≦x≦1の範囲を有する組成パラメータであり、且つ、組成パラメータ(1−xg)が対応する層の厚みの上に徐々に、特に線形に増大する勾配組成AxB(1−xg)を有する。表面粗さと転位密度に関して積層層構造1の品質を改善するため、スタック5内の勾配組成を有する層と後続層との界面で、組成パラメータが、勾配組成を有する層側の組成パラメータ(1−xg)よりも小さくなるように選択される。本発明は、また、このような積層層構造1を製造する方法にも関する。

(もっと読む)

基板上に歪層を製造する方法と層構造

【課題】

ウエーハ接着及び/又はウエーハ研磨なしに基板上に高い品質の歪層を製造する簡単な方法を提供すること。

【解決手段】

この発明は、歪をもたせる層に隣接した層に欠陥領域を形成する工程と、歪をもたせる層に少なくとも隣接した層を緩和させる工程とにより、基板上に歪層を製造する方法に関する。その歪層は別のエピタキシャル層に配置されることができる。そのように形成された層構造は種々の構成要素に好ましく適している。  (もっと読む)

(もっと読む)

基板上に歪層を製造する方法及び層構造

この発明は、基板上に歪層を有する層構造を製造する方法に関し、この方法は、歪を持たせる層に隣接する層内に、欠陥領域を形成する工程と、歪を持たせる層に隣接する少なくとも一つの層を緩和させる工程とを有する。この欠陥領域は、特に基板内に形成される。別のエピタキシャル層を配置することができる。このようにして形成した層構造は、有利には様々な種類の部品に適している。  (もっと読む)

(もっと読む)

61 - 80 / 102

[ Back to top ]