Fターム[5F152NQ02]の内容

再結晶化技術 (53,633) | 動作層、活性層、素子構成層の材料 (2,604) | 半導体 (2,300) | 4族 (1,228)

Fターム[5F152NQ02]の下位に属するFターム

Fターム[5F152NQ02]に分類される特許

41 - 60 / 236

複合基板およびその製造方法

【課題】複数の炭化珪素単結晶を有する複合基板およびその製造方法を提供する。

【解決手段】炭化珪素と異なる材料から作られた支持層31と、支持層31上に形成された炭化珪素層32とを有するベース部30が準備され、前記ベース部30の炭化珪素層32上に第1および第2の炭化珪素単結晶11、12の各々が接合される。前記接合する工程は、前記炭化珪素層32に前記第1および第2の炭化珪素単結晶11,12の各々を対向させる工程と、前記炭化珪素層11,12のうち前記第1および第2の炭化珪素単結晶11,12に対向する部分のそれぞれを、前記第1および第2の炭化珪素単結晶11,12上に昇華および再結晶させることによって、前記第1および第2の炭化珪素単結晶11,12の各々に前記炭化珪素層32を接合する工程とを含む複合基板の製造方法。

(もっと読む)

炭化珪素基板の製造方法

【課題】炭化珪素基板中を貫通して流体が漏出することを防止することができる炭化珪素基板の製造方法を提供する。

【解決手段】炭化珪素から作られた第1および第2の被支持部11、12の各々と、炭化珪素から作られた支持部30とが互いに対向し、かつ第1および第2の被支持部11、12の間に隙間GPが設けられるように、第1および第2の被支持部11、12、および支持部30が配置される。支持部30の炭化珪素を昇華および再結晶させることで、第1および第2の単結晶基板11、12の各々に支持部30が接合される。この際、隙間GPにつながるように支持部30に貫通孔THが形成されることで、隙間GPおよび貫通孔THを通って流体が通過し得る経路PTが形成される。この経路PTを塞ぐことで、炭化珪素基板中を貫通して流体が漏出することを防ぐことが可能となる。

(もっと読む)

炭化珪素基板、半導体装置、炭化珪素基板の製造方法

【課題】炭化珪素基板を用いた半導体装置の製造コストの低減を実現可能な炭化珪素基板、半導体装置および炭化珪素基板の製造方法を提供する。

【解決手段】炭化珪素基板1は、炭化珪素からなるベース層10と、単結晶炭化珪素からなり、ベース層10上に配置され、ベース層10よりも不可避不純物の濃度が低いSiC層20と、炭化珪素からなり、ベース層10の、SiC層20とは反対側の主面10D上に形成され、ベース層10よりも不可避不純物の濃度が低い被覆層90とを備えている。

(もっと読む)

炭化珪素基板の製造方法、半導体装置の製造方法、炭化珪素基板および半導体装置

【課題】炭化珪素基板を用いた半導体装置の製造コストの低減を実現可能な炭化珪素基板の製造方法、半導体装置の製造方法、炭化珪素基板および半導体装置を提供する。

【解決手段】炭化珪素基板1の製造方法は、単結晶炭化珪素からなるSiC基板20を準備する工程と、坩堝70内においてSiC基板20の一方の主面20Bに面するようにベース基板10を配置する工程と、坩堝70内において、ベース基板10を、ベース基板10を構成する炭化珪素の昇華温度以上の温度域に加熱することによりSiC基板20の一方の主面20Bに接触するように炭化珪素からなるベース層10を形成する工程とを備えている。そして、ベース層10を形成する工程では、坩堝70内に、SiC基板20およびベース基板10とは別の、珪素を含む物質からなる珪素発生源91が配置される。

(もっと読む)

炭化珪素基板の製造方法、半導体装置の製造方法、炭化珪素基板および半導体装置

【課題】炭化珪素基板を用いた半導体装置の製造コストの低減を実現可能な炭化珪素基板の製造方法、半導体装置の製造方法、炭化珪素基板および半導体装置を提供する。

【解決手段】炭化珪素基板1の製造方法は、炭化珪素からなるベース基板10および単結晶炭化珪素からなるSiC基板20を準備する工程と、ベース基板10の主面10A上に接触するようにSiC基板20を載置して、積層基板を作製する工程と、積層基板を、SiC基板20よりもベース基板10の温度が高くなるように加熱することにより、ベース基板10とSiC基板20とを接合する工程と、SiC基板20が接合されたベース基板10の、SiC基板20とは反対側の主面10B上にエピタキシャル成長層30を形成する工程とを備えている。

(もっと読む)

炭化珪素基板の製造方法、半導体装置の製造方法、炭化珪素基板および半導体装置

【課題】炭化珪素基板を用いた半導体装置の製造コストの低減を実現可能な炭化珪素基板の製造方法、半導体装置の製造方法、炭化珪素基板および半導体装置を提供する。

【解決手段】炭化珪素基板1の製造方法は、単結晶炭化珪素からなるSiC基板20を準備する工程と、坩堝80内においてSiC基板20の一方の主面20Bに面するようにベース基板10を配置する工程と、坩堝80内において、ベース基板10を、ベース基板10を構成する炭化珪素の昇華温度よりも高い温度域に加熱することにより、SiC基板20の一方の主面20Bに接触するように炭化珪素からなるベース層10を形成する工程とを備えている。そして、ベース層10を形成する工程では、坩堝80内に珪素を含有するガスが導入される。

(もっと読む)

炭化珪素基板およびその製造方法

【課題】複数の単結晶層を有する炭化珪素基板中にボイドが形成されることを防止することができる炭化珪素基板およびその製造方法を提供する。

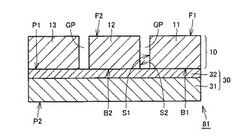

【解決手段】材料基板22の主面の第1の領域上に炭素層31が形成される。第1の単結晶層11の第1の裏面B1と、第2の単結晶層12の第2の裏面B2との各々が材料基板22の主面の第2の領域R2に面する部分を有するように、かつ第1の単結晶層11の第1の側面S1と第2の単結晶層12の第2の側面S2とによって挟まれた空隙GPが炭素層31上に配置されるように、第1および第2の単結晶層11、12が材料基板22上に並べられる。材料基板22と第1および第2の単結晶層11、12とを加熱することによって、第1および第2の裏面11、12の各々と接合したベース基板が形成される。

(もっと読む)

炭化珪素基板およびその製造方法

【課題】複数の単結晶層を有する炭化珪素基板中にボイドが形成されることを防止することができる炭化珪素基板およびその製造方法を提供する。

【解決手段】材料基板22の主面M2の第1の領域R1を覆う昇華防止層31が形成される。第1および第2の側面S1、S2によって挟まれた空隙GPが昇華防止層31上に配置されるように、材料基板22上に第1および第2の単結晶層11、12が並べられる。材料基板22と第1および第2の単結晶層11、12とを加熱することによって、主面M2の第2の領域R2から昇華した炭化珪素を、第1の単結晶層11の第1の裏面B1および第2の単結晶層12の第2の裏面B2の各々の上に再結晶させることで、第1および第2の裏面B1、B2の各々と接合したベース基板30が形成される。

(もっと読む)

SOI基板の作製方法

【課題】半導体層が効率良く平坦化されたSOI基板を提供することを課題の一とする。また、当該SOI基板を用いた半導体装置を提供することを課題の一とする。

【解決手段】ボンド基板に加速されたイオンを照射して該ボンド基板に脆化領域を形成し、ボンド基板またはベース基板の表面に絶縁層を形成し、絶縁層を介してボンド基板とベース基板を貼り合わせ、熱処理により、脆化領域においてボンド基板を分離して、ベース基板上に半導体層を形成し、半導体層の表面と、該半導体層と同じ半導体材料でなる半導体ターゲットとが対向するように配置し、半導体層の表面と半導体ターゲットとに、交互に希ガスイオンを照射することで、半導体層の表面の平坦化を図るSOI基板の作製方法である。

(もっと読む)

単結晶3C−SiC基板の製造方法およびそれによって得られた単結晶3C−SiC基板

【課題】エピタキシャル成長過程において発生する表面欠陥を大幅に減少させることができ、後工程を簡略化しながら半導体デバイスとしての品質を確保できる単結晶3C−SiC基板の製造方法を提供する。

【解決手段】ベース基板上にエピタキシャル成長によって単結晶3C−SiC層を形成させる単結晶3C−SiC基板の製造方法であって、

上記単結晶3C−SiC層を、平坦性の高い表面とその中に点在する表面ピットからなる表面状態となるよう形成する第1の成長段階と、

上記第1の成長段階で得られた単結晶3C−SiC層を、脱離律速の領域において表面の上記表面ピットを埋めるようさらにエピタキシャル成長させる第2の成長段階とを行う。

(もっと読む)

半導体基板、半導体基板の製造方法、および電磁波発生装置

【課題】複数の異なる周波数を出力する半導体基板を提供する。

【解決手段】p型半導体またはn型半導体を含む第1の不純物半導体と、第1の不純物半導体に接する複数の空乏領域を有する空乏化半導体とを備え、複数の空乏領域のそれぞれは、第1の不純物半導体との第1界面と、第1界面と対向する表面とを有し、複数の空乏領域のそれぞれは、第1界面に垂直な方向における第1界面と表面との平均距離および組成の少なくとも一つが異なる半導体基板を提供する。

(もっと読む)

半導体基板

【課題】単結晶構造を有するSiCから作られた領域と、炭化珪素から作られた支持部とを有し、かつ両者の界面の電気抵抗を低減することができる半導体基板を提供する。

【解決手段】支持部30は炭化珪素から作られている。少なくとも1つの層11の各々は第1および第2の面B1、F1を有する。第1の面B1は支持部30に支持されている。少なくとも1つの層11の各々は第1および第2の領域61、62を有する。第1の領域61は単結晶構造の炭化珪素から作られている。第2の領域62はグラファイトから作られている。第2の面F1は第1の領域61によって形成された面を有する。第1の面B1は、第1の領域61によって形成された面と、第2の領域62によって形成された面との各々を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル移動度のような電気的特性の優れた半導体装置およびその製造方法を提供する。

【解決手段】半導体装置1は、<01−10>方向における(0−33−8)面に対するオフ角が−3°以上+5°以下である主表面2Aを有し、炭化珪素からなる基板2と、基板2の主表面2A上にエピタキシャル成長により形成され、炭化珪素からなるp型層4と、p型層4の表面に接触するように形成された酸化膜8とを備えている。そして、p型層4と酸化膜8との界面から10nm以内の領域における窒素原子濃度の最大値は1×1021cm−3以上となっている。

(もっと読む)

半導体装置

【課題】Si混晶層における選択成長用マスクの開口率の違いによりエピタキシャル成長が不均一となることを防止すると共に、半導体素子のキャリア移動度を向上できるようにする。

【解決手段】半導体装置は、半導体基板100の上部に形成された素子分離膜101と、素子分離膜に囲まれてなる素子活性領域102と、該素子活性領域102に形成され正孔をキャリアとするチャンネル領域100aとを有するP型MIS−FET200Pと、素子分離膜における素子活性領域102の周辺部に形成された複数のダミー活性領域105とを備えている。複数のダミー活性領域105のうち、正孔の移動方向と対向する位置に形成されたダミー活性領域のみをシリコンとゲルマニウムとを含むSiGe付きダミー活性領域106としている。

(もっと読む)

半導体装置の製造方法

【課題】特性を十分に向上することができる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、SiC膜11を形成する工程と、このSiC膜11の表面にSiを供給した状態で、このSiC膜11を熱処理する熱処理工程と、熱処理工程によってSiC膜11の表面に得られたファセットをチャネル16とする工程とを備えている。このようにすれば、Siを供給した状態でSiC膜11を熱処理することにより、SiC膜11をエネルギ的に安定な表面状態に再構成させることができる。その結果、一周期が100nm以上のファセットが得られ、ファセットの平坦部分の長さを従来に比べて長くすることができる。したがって、界面準位の密度を減少することによりキャリアの移動度を向上することができ、半導体装置の特性を十分に向上することができる。

(もっと読む)

ダイヤモンド半導体素子およびその製造方法

【課題】ダイヤモンド薄膜内に存在する結晶欠陥、不純物等を減少させ、高品質なダイヤモンド薄膜を作製可能なダイヤモンド薄膜作製方法を提供すること。

【解決手段】ダイヤモンドが安定な高圧力下でアニールを行う。これにより、結晶中に含まれる格子欠陥等が回復、除去され、ダイヤモンド結晶薄膜を高品質化する事ができる。「(ダイヤモンドが)安定な、安定に」とは、ダイヤモンドがグラファイト化せずにダイヤモンドの状態を保つ状態を指す。ダイヤモンドが安定にアニール出来る領域内でアニールを行う温度(アニール温度、とも呼ぶ)Tおよびアニールを行う圧力(アニール圧力、とも呼ぶ)Pが決定される。この領域は、図21に示される、P>0.71+0.0027TまたはP=0.71+0.0027Tを満たし、なおかつP≧1.5GPaの領域である。このような領域は、図21中の斜線部分である。

(もっと読む)

ダイヤモンド半導体素子およびその製造方法

【課題】最大発振周波数fmaxを高くしてダイヤモンド電界効果トランジスタの特性を大きく向上させ、かつ電圧降下を小さく抑えることにより実用レベルに到達させること。

【解決手段】「ソース・ゲート電極間隔dSG、ゲート・ドレイン電極間隔dGDを狭くすること」と「ソース電極の厚さtS、ドレイン電極の厚さtDを厚くすること」とを両立させるために、ソース電極およびドレイン電極を、エッチング溶液を用いてエッチングする層とレジストを用いてリフトオフする層とに分けて形成する。これにより電極の逆メサ部を小さくすることができるため、ソース電極とゲート電極との間隔を小さくして最大発振周波数fmaxを上げ、かつソース電極およびドレイン電極の厚みを厚くして電圧降下を小さく抑えることができる。

(もっと読む)

炭化珪素基板の製造方法

【課題】製造工程を簡略化すると共に、表層部にらせん転位が存在することを抑制することができるSiC基板の製造方法を提供する。

【解決手段】炭化珪素からなり、主表面および当該主表面の反対面である裏面を備え、らせん転位1を表層部2aに含む欠陥含有基板2を用意する工程と、欠陥含有基板2のうち主表面に外力を印加することにより表層部2aの結晶性を低下させる第1外力印加工程と、外力印加工程の後、欠陥含有基板2を熱処理することにより表層部2aの結晶性を回復させる第1熱処理工程と、を含む製造方法とする。

(もっと読む)

半導体基板、電子デバイス及び半導体基板の製造方法

【課題】シリコン基板上の一部の領域に形成する3族窒化物半導体の結晶性を高める製造方法を提供する。

【解決手段】表面がシリコン結晶であるベース基板102と、シリコン結晶上の一部の領域に形成されたSixGe1−xC(0≦x<1)エピタキシャル結晶104と、SixGe1−xC(0≦x<1)エピタキシャル結晶104上に形成された3族窒化物半導体結晶106とを含む半導体基板100を提供する。一例として、当該半導体基板100は、シリコン結晶上に形成され、かつ、シリコン結晶を露出する開口110を有し、結晶の成長を阻害する阻害体108をさらに含み、SixGe1−xC(0≦x<1)エピタキシャル結晶104は、開口110の内部に形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル領域に応力を印加しつつ、基板やソース/ドレイン領域においてリーク電流の発生が効果的に抑制された半導体装置を提供する。

【解決手段】半導体装置は、第1導電型の不純物を含み、素子形成領域170を有する半導体基板101と、素子形成領域170上にゲート絶縁膜132を挟んで形成されたゲート電極125と、ゲート電極125の両側方に形成され、第2導電型の不純物を含むソース/ドレイン領域150とを備える。素子形成領域170のうちゲート電極の両側方に位置する領域には、半導体基板101の主面に対して傾いた半導体単結晶のファセット面を露出させる側壁を有し、コーナー部が丸められたリセス130が形成されており、ソース/ドレイン領域150は、リセス130に埋め込まれたシリコン混晶で構成されている。

(もっと読む)

41 - 60 / 236

[ Back to top ]