Fターム[5F152NQ02]の内容

再結晶化技術 (53,633) | 動作層、活性層、素子構成層の材料 (2,604) | 半導体 (2,300) | 4族 (1,228)

Fターム[5F152NQ02]の下位に属するFターム

Fターム[5F152NQ02]に分類される特許

81 - 100 / 236

炭化シリコン膜の製造方法

【課題】エッチングが困難な炭化シリコン膜をエッチングすることなく、一つのチップに炭化シリコンのデバイスとシリコンのデバイスを容易に混載させ、かつ、炭化シリコンのデバイスとシリコンのデバイスが電気的に絶縁された構造とすることが可能な炭化シリコン膜の製造方法を提供する。

【解決手段】本発明の炭化シリコン膜13の製造方法は、基板11上に下地層12を形成する工程と、下地層12上にシリコン膜を形成する工程と、シリコン膜をパターニングするパターニング工程と、パターニング工程の後にシリコン膜を炭化処理し、炭化された膜を含んだ炭化シリコン膜13を形成する工程と、炭化シリコン膜13をマスクに用いて、マスクが形成されていない領域の下地層12をエッチングする工程と、を有することを特徴とする。

(もっと読む)

炭化シリコン膜の製造方法

【課題】緻密で均一な膜厚であり、しかも所望の膜厚の炭化シリコン膜を得ることができ、かつ低コストや大口径化が可能な炭化シリコン膜の製造方法を提供する。

【解決手段】本発明の炭化シリコン膜13の製造方法は、基板11上にアモルファスシリコンとポリシリコンとの少なくとも一方を含むシリコン膜14を形成する工程と、シリコン膜14を炭化処理し、炭化された膜を含んだ炭化シリコン膜13を形成する工程と、を有することを特徴とする。

(もっと読む)

積層構造物

【課題】過度に複雑な、成長後の加工処理(post growth processing)が最小限に抑えられ、第2のいっそう厚い層と比べて非常に異なる特性を有する薄いダイヤモンド層を有する構造体を合成することが可能となる方法を提供する。

【解決手段】互いに接触している少なくとも2つの層(20,22)であって、各々の層は広いバンドギャップの材料でできており、各々の層は少なくとも1つの性質が他の層と相違している前記少なくとも2つの層(20,22)を有する生成物を製造する方法。

(もっと読む)

SOI基板の作製方法

【課題】繰り返しの使用によってボンド基板に生じる不具合を抑制することを目的の一とする。

【解決手段】ボンド基板に加速されたイオンを照射してボンド基板中に脆化領域を形成する第1の工程と、絶縁層を介してボンド基板とベース基板とを貼り合わせる第2の工程と、脆化領域においてボンド基板を分離して、ベース基板上に絶縁層を介して半導体層を形成する第3の工程と、脆化領域で分離されたボンド基板に対して、アルゴン雰囲気において第1の熱処理を施した後に、酸素及び窒素の混合雰囲気において第2の熱処理を施すことにより再生ボンド基板を形成する第4の工程と、を有し、再生ボンド基板を第1の工程におけるボンド基板として再び使用する。

(もっと読む)

半導体薄膜素子の製造方法並びに半導体ウエハ、及び、半導体薄膜素子

【課題】Si結晶層上に半導体素子を備えたSi以外の半導体単結晶層を備えた半導体薄膜素子の製造方法並びに半導体ウエハ、及び、半導体薄膜素子を提供する。

【解決手段】Si(111)基板(第1の基板)101の表面にバッファ層102と半導体単結晶層103とを順次形成する第1の工程と、半導体単結晶層101aとバッファ層102aとSi(111)基板の所定の厚さ部分102bとを含む分離島150を形成する第2の工程と、分離島の表面を覆う被覆層200を形成する第3の工程と、被覆層をマスクに前記Si(111)基板をSi(111)面に沿ってエッチングして剥離する第4の工程と、分離島の剥離面を別の基板(第2の基板)201の表面に接合する第5の工程とを備える。

(もっと読む)

半導体装置の作製方法

【課題】大面積な半導体装置を低コストに提供することを目的の一とする。または、nチャネル型トランジスタ及びpチャネル型トランジスタに最適な結晶面をチャネル形成領域とすることにより、性能向上を図ることを目的の一とする。

【解決手段】絶縁表面上に(211)面から±10°以内の面を上面とする島状の単結晶半導体層を形成し、単結晶半導体層の上面及び側面に接して形成し、且つ絶縁表面上に非単結晶半導体層を形成し、非単結晶半導体層にレーザー光を照射して非単結晶半導体層を溶融し、且つ、単結晶半導体層を種結晶として絶縁表面上に形成された非単結晶半導体層を結晶化して結晶性半導体層を形成し、結晶性半導体層を用いて、nチャネル型トランジスタ及びpチャネル型トランジスタを形成する。

(もっと読む)

立方晶炭化ケイ素単結晶薄膜の製造方法及び半導体装置

【課題】低コストの立方晶炭化ケイ素(3C−SiC)単結晶薄膜を得るための立方晶炭化ケイ素単結晶薄膜の製造方法及び半導体装置を提供する。

【解決手段】立方晶炭化ケイ素単結晶薄膜の製造方法において、基板101の表面に犠牲層102を形成する第1の工程と、犠牲層の表面に少なくとも表面層が立方晶構造である立方晶半導体層103を形成する第2の工程と、立方晶半導体層の表面に立方晶炭化ケイ素単結晶層104を形成する第3の工程と、犠牲層をエッチング除去して、立方晶半導体層と立方晶炭化ケイ素単結晶層との積層体を剥離する第4の工程とを備える。

(もっと読む)

半導体基板、半導体装置及び半導体基板の製造方法

【課題】所望の電気的特性を得やすい半導体基板、半導体装置及び半導体基板の製造方法を提供すること。

【解決手段】半導体基板の製造方法は、第1エピタキシャル層を形成する第1エピタキシャル層形成工程S1と、第1エピタキシャル層にトレンチを形成するトレンチ形成工程S2と、第1エピタキシャル層及びトレンチ内にエピタキシャル層を、異なる成長速度を含む複数の成長条件を用いて、トレンチ内を埋めるように形成し、複数の成長条件のそれぞれにおいてエピタキシャル層に取り込まれるドーパント濃度を一定にするエピタキシャル層形成工程S3、S4、S5と備える。

(もっと読む)

部分SOIウェーハの製造方法

【課題】活性層からバルク層に達した孔部で堆積中のアモルファスもしくは多結晶シリコンを単結晶化させる際に埋め込み酸化膜の領域での欠陥発生を抑制させる部分SOIウェーハの製造方法を提供する。

【解決手段】活性層を被う保護膜の一部に形成された窓部を通して、活性層と埋め込み酸化膜との各一部をエッチングして孔部を形成後、孔部にアモルファスシリコンを堆積させる。孔部内のアモルファスシリコンを、単結晶化させる場合に高エネルギ光の照射を行うことでエピタキシャル成長速度を速め、埋め込み酸化膜の領域を通過する際に発生する欠陥密度を抑制できる。

(もっと読む)

半導体基板の作製方法

【課題】炭化シリコンを含む半導体基板の新たな作製方法を提供することを目的の一とする。

【解決手段】シリコン基板表面に炭化処理を施して炭化シリコン層を形成し、シリコン基板にイオンを添加することにより、シリコン基板中に脆化領域を形成し、シリコン基板とベース基板とを絶縁層を介して貼り合わせ、シリコン基板を加熱して、脆化領域においてシリコン基板を分離することにより、ベース基板上に絶縁層を介して炭化シリコン層とシリコン層の積層構造を形成し、シリコン層を除去して炭化シリコン層の表面を露出させることにより半導体基板を作製する。

(もっと読む)

半導体基板の製造方法

【課題】良好な立方晶の炭化珪素膜を形成可能な半導体基板の製造方法を提供すること。

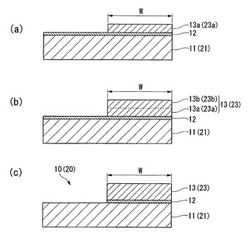

【解決手段】シリコン基板11上にバッファ層12を形成する第1の工程と、バッファ層12上にシリコン膜15を形成する第2の工程と、シリコン膜15を炭化して炭化珪素膜13を形成する第3の工程と、を含み、バッファ層12は、シリコンの格子定数と炭化珪素膜13の格子定数との間の格子定数を有する金属酸化物で構成され、第3の工程は、炭化水素系ガスの雰囲気下で行われる。

(もっと読む)

半導体基板の製造方法及び半導体基板

【課題】良好な立方晶の炭化珪素膜を形成可能な半導体基板の製造方法及び半導体基板を提供すること。

【解決手段】シリコン基板11の上面に多孔質な多孔質シリコン層12を形成する工程と、水素ガス及び炭化水素系ガスの混合ガスまたは炭化水素系ガスを供給し、多孔質シリコン層12の表面を結晶化及び炭化して炭化珪素膜13を形成する工程と、を備える。

(もっと読む)

ダイヤモンド薄膜及びその製造方法

【課題】積層欠陥及び貫通転位の密度が十分に低いダイヤモンド薄膜構造とその製造方法を提供する。

【解決手段】基板101と、基板101の主方位面の一部を覆うマスク材102と、基板101の主方位面の表面からエピタキシャル成長するダイヤモンド薄膜103とで構成されるダイヤモンド薄膜構造であって、ダイヤモンド薄膜103は、マスク材102の上に形成され、ダイヤモンド薄膜103の結晶方位は基板101の結晶方位とそろっている。ダイヤモンド基板101に存在する貫通転位104aは、マスク材102で覆われていない部分のダイヤモンド基板101の主方位面を介してダイヤモンド薄膜103まで貫通するが、貫通転位104bは、マスク材102によってダイヤモンド薄膜103への伝播が遮られるため、ダイヤモンド薄膜103の貫通転位密度は低下し、結晶性が向上する。

(もっと読む)

半導体装置およびその製造方法

【課題】大きな歪み量を発生可能な半導体装置およびその製造方法を提供する。

【解決手段】半導体装置の製造方法は、CとCの濃度の10倍以上のGeとを含んだSiGeC層を形成する工程(S3)と、SiGeC層内のCのうちで格子置換位置に位置しているものを格子間位置へと移動させることによって、前記SiGeC層内の全てのCに対する格子置換位置に位置するCの割合を形成された時点での割合から低下させて50%以下に低下させる工程(S4)と、を含む。

(もっと読む)

所望の基板への単結晶材料からなる薄層の移動方法

【課題】第1の単結晶の基板から第2の基板へ、単結晶の薄層を移動する方法であって、層分割に必要とされる水素の注入量が低減された移動方法が実現される。

【解決手段】第1の単結晶の基板から第2の基板へ、単結晶の薄層を移動する方法は、水素のトラップを誘導するイオンを水素イオンと共注入すること、高温で水素を注入すること、またはこれらの組み合わせを実施し、次に、第1の基板の注入された層と残りの基板との結合を弱めるために熱処理を施し、さらに、注入された第1の基板と第2の基板との強力な接着を形成し、最後に、水素が充填された微小亀裂を形成、成長させることで単結晶の薄層が第1の基板の残りから分割するように別の熱処理を施すことを含む。

(もっと読む)

混合層の部分的再結晶化によるハイブリッド基板生成方法

【課題】下地基板と、複数の群の異なる隣接エリアから形成された混合層とを含むハイブリッド基板を簡単かつ確実に生成する方法を提案する。

【解決手段】ハイブリッド基板生成方法が

単結晶の第1の基板が、2つの表面部分11および12を得るように分離されるステップと、

表面部分11に沿って延び、第1のエリア13で形成され、かつアモルファス材料の異なる第2のエリアに隣接する混合層を含む仮基板が準備され、これらの第2のエリアが、この第1の基板の自由表面の少なくとも一部を形成するステップと、

少なくともこれらのアモルファスエリア全体の分子接合によって、第1の表面部分と同じ結晶配向の他の表面部分12がこの第1の基板に接合されるステップと、

2つの表面部分の結晶配向にしたがったアモルファスエリアの少なくとも一部の固相再結晶化が第1のエリアに対して選択的に生じ、2つの表面部分が有利には分離されるステップとを含む。

(もっと読む)

貼り合わせウェーハの製造方法

【課題】貼り合わせ基板の活性層用ウェーハの表面に、結晶面が異なる領域を簡単に形成可能な貼り合わせウェーハの製造方法を提供する。

【解決手段】高エネルギ光を、活性層用ウェーハの素材は溶融しないが、吸光係数が高いアモルファスシリコンは溶融する条件で貼り合わせ基板の活性層用ウェーハ側の面に照射し、この窓部内のシリコンを溶融させて固化させる。このとき、アモルファスシリコンを単結晶シリコンに液相エピタキシーにより変質させれば、貼り合わせ基板の活性層用ウェーハの表面に、結晶面が異なる領域を簡単に形成できる。

(もっと読む)

ダイヤモンド半導体及び作製方法

【課題】従来技術と比較して、室温で十分に高いキャリア濃度を有するダイヤモンド半導体及び作製方法を提供すること。

【解決手段】ダイヤモンド基板11(図5(a))上にマイクロ波プラズマCVD装置を用い、メタンを反応ガスとし、基板温度700℃でダイヤモンド薄膜12を1ミクロン積層する(図5(b))。ダイヤモンド薄膜12にイオン注入装置を用い、不純物1(VI族又はII族元素)を打ち込む(図5(c))。その後、不純物2(III族又はV族元素)を打ち込んだが(図5(d))、注入条件は、打ち込んだ不純物がそれぞれ表面から0.5ミクロンの厚さの範囲内で、1×1017cm-3となるようにシミュレーションにより決定した。その後、2種類のイオンが注入されたダイヤモンド薄膜13をアニールすることにより(図5(e))、イオン注入された不純物の活性化を行い、ダイヤモンド半導体薄膜15を得た(図5(f))。

(もっと読む)

炭化珪素単結晶基板および炭化珪素単結晶エピタキシャルウェハ

【課題】デバイス特性の劣化や、歩留まりの低下を抑制するため、貫通転位の転位線の方向を規定する方法を提供する。

【解決手段】貫通転位3の転位線の方向が揃えられ、貫通転位3の転位線の方向と[0001]c軸との為す角度θが22.5°以下となるようにする。[0001]c軸方向に転位線を持つ貫通転位3は、基底面転位の転位線の方向と垂直であるため、C面内の拡張転位とはならず、積層欠陥を発生させることがない。このため、貫通転位3の転位線の方向が[0001]c軸であるSiC単結晶基板1に対して電子デバイスを形成すれば、デバイス特性は良好となり、劣化が無く、歩留まりも向上したSiC半導体装置。

(もっと読む)

歪誘起合金及び段階的なドーパントプロファイルを含むその場で形成されるドレイン及びソース領域

【解決手段】

トランジスタのドーパントプロファイルは、その場で(in situ)ドープされた歪誘起半導体合金に基いて得ることができ、段階的なドーパント濃度が高さ方向に沿って確立され得る。その結果、半導体合金をチャネル領域にごく近接して位置させることができ、それにより全体的な歪誘起効果を高めることができる一方で、最終的に得られるドーパントプロファイルについて過度に妥協しなくてよい。更に、半導体合金を選択的に成長させるのに先立ち追加的な注入種が組み込まれてよく、それにより内部歪の注入誘起緩和を回避することができる。

(もっと読む)

81 - 100 / 236

[ Back to top ]