Fターム[5F152NQ03]の内容

再結晶化技術 (53,633) | 動作層、活性層、素子構成層の材料 (2,604) | 半導体 (2,300) | 4族 (1,228) | Si (609)

Fターム[5F152NQ03]に分類される特許

1 - 20 / 609

エピタキシャルウェーハとその製造方法

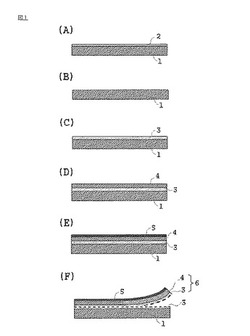

シリコン単結晶膜およびその製造方法

【課題】薄層化された自立性のシリコン単結晶膜を提供し、また、剥離時の熱処理温度を格段に低減することができる新たなシリコン単結晶膜の形成方法を提供する。

【解決手段】シリコン単結晶膜6は、Siの含有率が、90原子%以上であり、厚みが、50μm以下であり、自立性がある。

(もっと読む)

半導体装置の製造方法

【課題】縦型トランジスタにおける上部拡散層の深さ方向のばらつきを低減することのできる半導体装置の製造方法を提供する。

【解決手段】本発明は表面が平坦なシリコン層からなる上部拡散層11を形成しようとするものであり、具体的には、ファセットを有するシリコン層を選択的に過剰成長させた後、層間絶縁膜7表面に形成されたシリコン層をCMPで擦り切ってシリコン層の表面を平坦化する。シリコン層の成長は、シリコン層を単結晶シリコンで選択的にエピタキシャル成長させる。この場合、ファセットが生じるので、最も成長が遅いファセットが層間絶縁膜表面より上方に位置するまで充分過剰に成長させる。

(もっと読む)

半導体ウェハ

【課題】高い結晶品質を有する、多様な材料からなる、完全に緩和した、又は歪んだ半導体層を積層するために絶縁体層の格子寸法を調整するための高い柔軟性を許容する、SOI構造の作製のための基板を提供する。

【解決手段】実質的にシリコンからなる単結晶基板ウェハ1、電気絶縁性材料を含み、かつ2nm〜100nmの厚さを有する第一非晶質中間層2、立方晶系Ia−3結晶構造と、(Me12O3)-1-x(Me22O3)xの組成と、基板ウェハの材料の格子定数と0%〜5%異なる格子定数とを有する単結晶第一酸化物層3を示される順序で含むことを特徴とする半導体ウェハ。

(もっと読む)

CMOS垂直置換ゲート(VRG)トランジスタ

【課題】本発明は、CMOS垂直置換ゲート(VRG)トランジスタを提供する。

【解決手段】集積回路構造は平面に沿って形成された主表面を有する半導体領域及び表面中に形成された第1及び第2のソース/ドレインドープ領域を含む。絶縁トレンチが第1及び第2のソース/ドレイン領域間に形成される。第1のソース/ドレイン領域とは異なる伝導形のチャネルを形成する第3のドープ領域が、第1のソース/ドレイン領域上に配置される。第4のドープ領域が第2のソース/ドレイン領域上に形成され、第2のソース/ドレイン領域とは相対する伝導形をもち、チャネル領域を形成する。第5及び第6のソース/ドレイン領域が、それぞれ第3及び第4のドープ領域上に形成される。

(もっと読む)

エピタキシャルウエーハ及びその製造方法

【課題】 本発明は、シリコンウエーハ中の酸素等不純物の悪影響がエピタキシャル層の撮像素子形成部分まで及ばないエピタキシャルウエーハ及びその製造方法を提供することを目的とする。

【解決手段】 撮像素子製造用のエピタキシャルウエーハを製造する方法であって、前記エピタキシャル層の成長前に、前記撮像素子の製造後において前記エピタキシャル層中の酸素濃度が4×1017atoms/cm3以上となる領域の厚さXを計算し、前記エピタキシャル層の成長において、前記エピタキシャル層を、前記厚さXに加えて、更に前記撮像素子の製造後におけるエピタキシャル層中の酸素濃度が4×1017atoms/cm3未満となる領域の厚さが6μm以上となる厚さで成長することを特徴とするエピタキシャルウエーハの製造方法。

(もっと読む)

貼り合わせSOIウェーハの製造方法

【課題】 本発明は、SOI層の膜厚の面内均一性の良好なSOIウェーハを製造する方法を提供することを目的とする。

【解決手段】 イオン注入層が形成されたボンドウェーハのイオン注入された側の表面とベースウェーハの表面とを絶縁膜を介して貼り合わせた後、前記ボンドウェーハの一部を前記イオン注入層で剥離して、貼り合わせSOIウェーハを作製し、その後、平坦化処理を行う貼り合わせSOIウェーハの製造方法であって、

前記剥離後の貼り合わせSOIウェーハに対し、前記SOI層表面の周辺部の自然酸化膜が除去され、中央部の自然酸化膜が残存するように、水素ガスを含む雰囲気でRTA処理を行い、前記中央部に自然酸化膜が残存した貼り合わせSOIウェーハに対し、前記SOI層の面内膜厚レンジが1.5nm以下となるように前記平坦化処理を行うことを特徴とする貼り合わせSOIウェーハの製造方法。

(もっと読む)

装置の作製方法

【課題】剥離前の形状及び特性を保った良好な状態で転置工程を行えるような、剥離工程

を用いて半導体装置及び表示装置を作製できる技術を提供する。よって、より高信頼性の

半導体装置及び表示装置を装置や工程を複雑化することなく、歩留まりよく作製できる技

術を提供することも目的とする。

【解決手段】透光性を有する第1の基板上に光触媒物質を有する有機化合物層を形成し、

光触媒物質を有する有機化合物層上に素子層を形成し、光を第1の基板を通過させて、光

触媒物質を有する有機化合物層に照射し、素子層を前記第1の基板より剥離する。

(もっと読む)

エピタキシャルウェーハとその製造方法

【課題】歪み層形成に供されるウェーハで転位発生に対して耐性が高いエピタキシャルウェーハを提供する。

【解決手段】シリコンエピタキシャル層表面の酸素濃度が1.0×1017〜12×1017atoms/cm3とされてなるエピタキシャルウェーハの製造方法であって、酸素濃度設定熱処理の処理温度Xと処理時間Yとが、処理温度Xが800℃〜1400℃の範囲、処理時間Yが180min以下で、かつ、

Y ≧ 1.21×1010 exp(−0.0176X)

の関係を満たすように設定される。

(もっと読む)

半導体装置及びその製造方法

【課題】SOI構造のフラッシュメモリーの提供

【解決手段】

半導体基板1上にシリコン窒化膜2及びシリコン酸化膜3が選択的に設けられ、シリコン酸化膜3上には、選択的に横(水平)方向エピタキシャルSi層5が設けられ、Si層5の両側面には、それぞれ側面を接して横(水平)方向エピタキシャルSi層6が設けられた構造からなる半導体層が素子分離領域のシリコン窒化膜4により絶縁分離されている。Si層6の残りの周囲には第1のゲート酸化膜10を介して包囲型フローティングゲート電極11が設けられ、包囲型フローティングゲート電極11の周囲には第2のゲート酸化膜12を介して包囲型コントロールゲート電極13(ワード線)が設けられ、Si層5には概略ソースドレイン領域9が設けられている2重包囲型ゲート電極を有するMIS電界効果トランジスタより構成したフラッシュメモリー。

(もっと読む)

半導体装置の作製方法

【課題】複数のトランジスタが高集積化された素子の少なくとも一のトランジスタに、作製工程数を増加させることなくバックゲートを設ける半導体装置を提供する。

【解決手段】複数のトランジスタが上下に積層されて設けられた素子において、少なくとも上部のトランジスタ102は、半導体特性を示す金属酸化物により設けられ、下部のトランジスタ100が有するゲート電極層を上部のトランジスタのチャネル形成領域と重畳するように配して、ゲート電極層と同一の層の一部を上部のトランジスタ102のバックゲートBGとして機能させる。下部のトランジスタ100は、絶縁層で覆われた状態で平坦化処理が施され、ゲート電極が露出され、上部のトランジスタ102のソース電極及びドレイン電極となる層に接続されている。

(もっと読む)

薄膜製造方法、それを用いた半導体デバイスの製造方法およびそれらに用いられる半導体薄膜部品

【課題】高品質な半導体薄膜を製造する薄膜製造方法を提供する。

【解決手段】薄膜製造方法は、a−Si膜等の半導体薄膜を第1の基板上に堆積する工程S1と、第1の基板をエッチングして第1の基板と半導体薄膜との間に中空部を形成する工程S2と、半導体薄膜に第2の基板を接触させる工程S3と、半導体薄膜に第2の基板を押し付け、または半導体薄膜が溶融する強度を有するレーザ光を半導体薄膜に照射する工程S4と、第1の基板を半導体薄膜から引き離す工程S5とを備える。

(もっと読む)

単結晶の半導体層を支持基板上に転写する方法

【課題】単結晶の半導体層を支持基板上に転写し、転写された層がもはや脆化注入によって生成される可能性のある結晶欠陥を含まない方法を提供する。

【解決手段】単結晶の半導体層3を支持基板上に転写する方法に関し、(a)ドナー基板31に注入種を注入するステップと、(b)ドナー基板31を支持基板に接合するステップと、(c)層3を支持基板上に転写するためにドナー基板31を破壊するステップと、前記単結晶の層3の第2の部分35の結晶格子の秩序を乱すことなしに、転写されるべき単結晶の層3の部分34が非晶質にされるステップであり、部分34、35が、それぞれ、単結晶の層3の表面部分および埋め込み部分であるステップと、非晶質の部分34が500℃未満の温度で再結晶化されるステップであり、第2の部分35の結晶格子が再結晶化のための種結晶として働くステップとを含む。

(もっと読む)

半導体基板の再生方法、再生半導体基板の作製方法、及びSOI基板の作製方法

【課題】半導体基板の再生に適した方法を提供する。

【解決手段】損傷半導体領域と絶縁層とを含む凸部が周縁部に存在する半導体基板に対し、絶縁層を除去するエッチング処理と、硝酸、硝酸によって酸化された半導体基板を構成する半導体材料を溶解する物質、半導体材料の酸化速度及び酸化された半導体材料の溶解速度を制御する物質、及び亜硝酸を含み、亜硝酸の濃度が10mg/l以上1000mg/l以下である混合液を用いて、未損傷の半導体領域に対して損傷半導体領域を選択的に除去するエッチング処理と、を行うことで半導体基板を再生する。

(もっと読む)

半導体装置

【課題】プラスチック支持体を用いた半導体装置を提供する。

【解決手段】プラスチック支持体上に形成されたカラーフィルタと、前記カラーフィルタ

上に形成された接着層と、前記接着層上に形成された絶縁膜と、前記絶縁膜上に形成され

た薄膜トランジスタと、前記薄膜トランジスタ上に形成された発光素子とを有する。また

は、プラスチック支持体と、前記プラスチック支持体に対向する対向基板と、前記プラス

チック支持体と前記対向基板との間に保持された液晶とを有し、前記プラスチック支持体

上に形成されたカラーフィルタと、前記カラーフィルタ上に形成された接着層と、前記接

着層上に形成された絶縁膜と、前記絶縁膜上に形成された薄膜トランジスタとを有する。

(もっと読む)

半導体基板を処理する方法

【課題】クリーンかつダメージのない表面を半導体基板上に形成するための装置および方法を提供する。

【解決手段】エピタキシャル層を形成する前にプラズマ洗浄プロセスに基板の表面を暴露するように適合された洗浄チャンバを含有するシステム。洗浄プロセスを基板に実施する前に、該洗浄チャンバの内部表面にゲッタリング材料を堆積することによって、該洗浄チャンバで処理された基板の汚染物を減少するための方法が用いられる。酸化およびエッチングステップが洗浄チャンバにおいて基板に繰り返し実施されて、エピタキシャルを配置可能な基板にクリーンな表面を暴露および生成する。一実施形態において、低エネルギプラズマが該洗浄ステップ時に使用される。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ162、トランジスタ162と異なる半導体材料を用いた読み出し用トランジスタ160及び容量素子164を含む不揮発性のメモリセルにおいて、メモリセルへの書き込みは、書き込み用トランジスタ162をオン状態とすることにより、書き込み用トランジスタ162のソース電極(またはドレイン電極)と、容量素子164の電極の一方と、読み出し用トランジスタ160のゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタ162をオフ状態とすることにより、ノードに所定量の電荷を保持させることで行う。また、読み出し用トランジスタ160として、pチャネル型トランジスタを用いて、読み出し電位を正の電位とする。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルからの読み出しのために基準電位より低い電位を出力する機能を有する電位切り替え回路を備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

半導体装置

【課題】従来の半導体装置においては、シリコンエピタキシャル層に結晶欠陥が生じ易いという問題がある。

【解決手段】半導体装置1は、シリコン基板10、歪み付与層20、シリコン層30、FET40、および素子分離領域50を備えている。シリコン基板10上には、歪み付与層20が設けられている。歪み付与層20上には、シリコン層30が設けられている。歪み付与層20は、シリコン層30中のFET40のチャネル部に格子歪みを生じさせる。シリコン層30中には、FET40が設けられている。FET40は、ソース・ドレイン領域42、SD extension領域43、ゲート電極44およびサイドウォール46を含んでいる。ソース・ドレイン領域42と上述の歪み付与層20とは、互いに離間している。FET40の周囲には、素子分離領域50が設けられている。素子分離領域50は、シリコン層30を貫通して歪み付与層20まで達している。

(もっと読む)

シリコン−オン−インシュレーター構造及びバルク基板に対するSiGeの堆積

【課題】欠陥を最小限としながら、SiGe−オン−インシュレーター構造を製造するため及びシリコン上に歪み緩和SiGe層を製造するための方法を提供する。

【解決手段】アモルファスSiGe層600が、トリシラン及びGeH4からCVDによって、ドーパントの1以下のモノレイヤー上に堆積される。これらのアモルファスSiGe層600は、融解または固相エピタキシー(SPE)プロセスによってシリコン上に再結晶される。融解プロセスは、好ましくは、全体のゲルマニウム含量を希釈するようなゲルマニウムの拡散も引き起こし、そして絶縁体の上層のシリコン500を実質的に消費する。SPEプロセスは、下地のシリコン500中へのゲルマニウムの拡散を用いてまたは用いずに実際され得、従って、SOI及び従来の半導体基板に適用可能である。

(もっと読む)

1 - 20 / 609

[ Back to top ]