Fターム[5H730FD01]の内容

DC−DCコンバータ (106,849) | 信号検出 (10,889) | 出力電圧の (5,426)

Fターム[5H730FD01]の下位に属するFターム

微分値 (18)

積分値、平均値 (329)

非抵抗素子を用いるもの (20)

ツェナーダイオードによる対域値増分の検出 (28)

Fターム[5H730FD01]に分類される特許

161 - 180 / 5,031

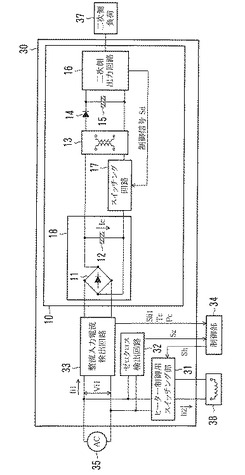

電力制御方法、電力制御装置および画像形成装置

【課題】コンデンサインプット形の整流回路を用いているにもかかわらず、入力電流のピーク値を抑えることのできる電力制御を低コストで実現すること。

【解決手段】交流電源35からの交流電力をコンデンサインプット形のレギュレーター10により整流して二次側負荷に供給し、かつ、交流電源35からの交流電力をヒーター38に供給するための電力制御方法である。この電力制御方法は、ヒーター38に流れ込むヒーター入力電流Ii2を各半サイクルの全期間においてオンとする第1モード、および、ヒーター入力電流Ii2の各半サイクルにおいて、レギュレーター10においてコンデンサの充電電流Icに起因する入力充電電流Ii3が流れている期間はヒーター入力電流Ii2をオフとしそれ以外の期間はヒーター入力電流Ii2をオンとする第2モード、が設けられ、第1モードまたは第2モードを選択して用いることにより制御を行う。

(もっと読む)

電圧変換装置

【課題】入力電圧を昇圧又は降圧させて所望の電圧を出力し、小型化、低コスト化が可能な電圧変換器を提供する。

【解決手段】第1スイッチング素子Tr1は、第1ダイオードDi1のアノードと電源Pdの低電圧側In2との間に配置されており、第2スイッチング素子Tr2は第2ダイオードDi2のアノードと電源Pdの低電圧側In2との間に配置されている。

(もっと読む)

電流制限回路

【課題】ノイズ耐性が高く、且つ、製造プロセス、電源、及び電源電圧が変動するような場合においても精度が高い、出力トランジスタに対する電流制限回路を提供する。

【解決手段】電流制限回路が、基準トランジスタと、基準トランジスタに所定の電流を流す電流源と、出力トランジスタがオンした時の両端の第1の電位差と基準トランジスタの両端の第2の電位差を比較する比較器であって、第1の電位差が第2の電位差よりも大きくなった場合に、出力トランジスタをオフするように制御する電流制限信号を出力する、比較器とを備える。基準トランジスタは、出力トランジスタとは素子サイズの異なる同型のトランジスタであり、基準トランジスタがオンした時のオン抵抗は、出力トランジスタがオンした時のオン抵抗の1/Nの大きさ(Nは1より大きい数)であり、更に、基準トランジスタがオンするように基準トランジスタのゲートにバイアスがかけられている。

(もっと読む)

モータ制御システム

【課題】矩形波制御実行中にコンバータによる昇圧動作の開始を適時に行ってシステム損失の増加を抑制することができるモータ制御システムを提供する。

【解決手段】モータ制御システムは、電源、コンバータ、インバータおよび交流モータと、コンバータおよびインバータの作動を制御することにより、正弦波PWM制御、過変調制御および矩形波制御のいずれかの制御方式でモータを駆動させる制御部とを備える。制御部は、電源から供給される直流電圧をコンバータで昇圧せずにインバータに供給し、モータについて、モータ電流のd軸q軸平面上における電流ベクトルの電流位相が最適電流進角またはその近傍で矩形波制御が実行されるように制御する。この場合において、制御部は、電流ベクトルが昇圧開始前後でシステム損失が等しくなるモータトルクT2に相当する電流位相になったときにコンバータによる昇圧動作を開始させる。

(もっと読む)

電源装置

【課題】力率を改善するため、オン抵抗が小さく、スイッチング速度が速いスイッチング素子を用いた電源装置において、スイッチング素子のソース−ドレイン間に寄生容量があると、スイッチング損失が発生する。スイッチング損失がない、効率を改善した電源装置を提供する。

【解決手段】電源装置は、整流回路に接続されるインダクタと正極端子との間に接続される第1整流素子と、前記第1整流素子の入力端子と負極端子との間に接続される第1スイッチング素子と、前記第1スイッチング素子に並列に接続される第2スイッチング素子及びトランスと、前記第2スイッチング素子と前記トランスの接続部と、前記正極端子との間に接続され、前記接続部から前記正極端子に向かう整流方向を有する第2整流素子と、前記トランスと前記正極端子との間に接続され、前記トランスから前記正極端子に向かう整流方向を有する第3整流素子を有する。

(もっと読む)

充電装置

【課題】絶縁トランスの2次側の変換部の出力電圧を安定化できる充電装置を提供する。

【解決手段】この充電装置10は、DCバス21に接続可能な接続部11と、蓄電池31と接続可能な接続部12a,12bと、接続部11から供給される直流電流を交流電流に変換して絶縁トランス14に出力する変換部13aと、絶縁トランス14と、絶縁トランス14から出力される交流電流を直流電流に変換する変換部13bと、変換部13bの出力電圧を変圧して接続部12aに出力する変圧部Hと、変換部13bと変圧部Hの間に接続された蓄電池17とを備える。

(もっと読む)

DC/DCコンバータならびにそれを用いた電源装置および電子機器

【課題】スタンバイモードの消費電力を低減する。

【解決手段】第1フィードバック回路20は、通常モードにおいて動作状態、スタンバイモードにおいて非動作状態となり、出力電圧VOUTに応じた第1フィードバック信号VFB1を生成し、トランスT1の2次側から1次側へ伝送する。第2フィードバック回路40は、通常モードにおいて非動作状態、スタンバイモードにおいて動作状態となり、第2出力キャパシタCo2に生ずる電圧VCCに応じた第2フィードバック信号VFB2を生成する。制御回路10は、通常モードにおいて第1フィードバック信号VFB1にもとづいて出力電圧VOUTが第1レベルと一致するように、スタンバイモードにおいて第2フィードバック信号VFB2にもとづいて出力電圧VOUTが第1レベルより低い第2レベルと一致するように、スイッチングトランジスタM1のオン、オフを制御する。

(もっと読む)

半導体装置

【課題】インダクタンスを低減できる半導体装置を提供する。

【解決手段】整流用MOSFET20と転流用MOSFET21、及びこれらを駆動する駆動用IC22を一つのパッケージに実装した半導体装置において、整流用MOSFET20、金属板25、転流用MOSFET21を積層し、主回路の電流はパッケージの裏面から表面に向かって流れ、金属板25はパッケージ内の配線を経由して出力端子に繋がり、駆動用IC22と整流用MOSFET20、及び転流用MOSFET21を繋ぐ配線にワイヤボンディング23を用い、全ての端子が同一面に配置されている。これにより、インダクタンスが小さくなり、電源損失及びスパイク電圧が低減される。

(もっと読む)

DC/DCコンバータの制御回路及びDC−DCコンバータ

【課題】出力電流の変動を抑圧するようにDC/DCコンバータを制御する。

【解決手段】帰還電流生成回路14及び合成回路16は、インダクタ電流ILの直流成分を表す第1の帰還電圧VFB1を生成する。リップル信号生成回路15は、入力電圧及び出力電圧に基づいて、インダクタ電流ILの交流成分を表す第2の帰還電圧VFB2を生成する。合成回路15は、第1及び第2の帰還電圧を合成して第3の帰還電圧VFB3を生成する。コンパレータ12は、基準電圧VREFと第3の帰還電圧VFB3とを比較し、ハイレベル又はローレベルの制御信号HYSOを出力する。ドライバ回路13は、スイッチング素子M1,M2を制御する。リップル信号生成回路15は、制御信号HYSOがローレベルであるとき、入力電圧と出力電圧との差に基づいて第2の帰還電圧を生成し、制御信号HYSOがハイレベルであるとき、出力電圧に基づいて第2の帰還電圧を生成する。

(もっと読む)

駆動回路及びスイッチング電源装置

【課題】レベルシフト回路を低消費電力させ、回路の遅れ時間を短くして高周波化できる駆動回路及びスイッチング電源装置。

【解決手段】直流電源の両端に接続され且つ直列に接続されたローサイドスイッチング素子Q1とハイサイドスイッチング素子Q2とをオンオフ駆動させる駆動回路であって、所定の周波数信号を発生する発振回路11と、ローサイドスイッチング素子とハイサイドスイッチング素子との接続点の基準電位VSが第1電位から第2電位まで変化する場合に基準電位が第1電位以上第2電位未満の期間中に発振回路からの周波数信号に応答してセット信号とリセット信号を出力するパルス作成回路20aと、パルス作成回路からのセット信号とリセット信号とに基づいて周波数信号をレベルシフトした出力信号を出力するレベルシフト部FF1とを備える。

(もっと読む)

DC/DCコンバータの制御回路及びDC−DCコンバータ

【課題】出力電圧の変動を抑圧するようにDC/DCコンバータを制御する。

【解決手段】帰還電圧生成回路14及び合成回路16は、インダクタ電流ILの直流成分を表す第1の帰還電圧VFB1を生成する。リップル信号生成回路15は、入力電圧及び出力電圧に基づいて、インダクタ電流ILの交流成分を表す第2の帰還電圧VFB2を生成する。合成回路15は、第1及び第2の帰還電圧を合成して第3の帰還電圧VFB3を生成する。コンパレータ12は、基準電圧VREFと第3の帰還電圧VFB3とを比較し、ハイレベル又はローレベルの制御信号HYSOを出力する。ドライバ回路13は、スイッチング素子M1,M2を制御する。リップル信号生成回路15は、制御信号HYSOがローレベルであるとき、入力電圧と出力電圧との差に基づいて第2の帰還電圧を生成し、制御信号HYSOがハイレベルであるとき、出力電圧に基づいて第2の帰還電圧を生成する。

(もっと読む)

電源装置

【課題】 DSPを備えるデジタル制御回路を用いた電源装置において、急激な負荷変動に対しても適切に応答することが可能な技術を開示する。

【解決手段】 本明細書が開示する電源装置は、ヒステリシスコンパレータを備えるアナログ制御回路と、デジタル信号処理装置(DSP)を備えるデジタル制御回路と、アナログ制御回路またはデジタル制御回路からの指令信号に従い動作するスイッチング電源回路を備えている。その電源装置は、スイッチング電源回路の出力電圧が急変する場合は、アナログ制御回路によってスイッチング電源回路をヒステリシス制御する。その電源装置は、スイッチング電源回路の出力電圧が急変しない場合は、デジタル制御回路によってスイッチング電源回路をPWM制御する。

(もっと読む)

スイッチング電源装置の制御回路およびスイッチング電源装置

【課題】スイッチング電源装置において、交流入力電圧の大きさに応じて個々に防振対策をする必要性をなくすようにする。

【解決手段】入力電圧検出部30は、交流入力電圧が100V系であるか200V系であるかを検出し、その検出結果に応じて、周波数低減ゲイン設定部40が周波数低減ゲイン特性を切り替える。周波数低減ゲイン設定部40は、負荷率に応じた値のフィードバック信号を受け、切り替えられた周波数低減ゲイン特性に沿った周波数に変換し、その周波数のオン・オフ信号で駆動回路60がスイッチング素子を駆動する。交流入力電圧の大きさに応じて周波数低減ゲイン特性を切り替えたことで、100V系より200V系の方がフィードバック信号の低減が早まるという特性がキャンセルされ、周波数低減時に電源動作周波数が可聴領域に到達する負荷率を揃えることができ、一括した防振対策を可能にする。

(もっと読む)

電源装置及び画像形成装置

【課題】負荷電流の変動による導通損失を減らし、変換効率を向上させる。

【解決手段】電源の出力側に接続されたコンデンサC62を一端とするチョークコイルL61と、電源の入力側とチョークコイルL61の間に接続され、チョークコイルL61を介して出力電圧を制御する主スイッチング素子Q61と、回生ダイオードD61と、出力電圧に比例した電圧と基準電圧を比較して主スイッチング素子Q61をオン又はオフするコンパレータI61と、主スイッチング素子Q61のオン状態が所定の時間、継続されるように、コンパレータI61に入力される出力電圧に比例した電圧を所定の時間、変更するワンショットマルチバイブレータと、を具備する。

(もっと読む)

電力変換装置

【課題】構成部品の特性のばらつきに伴って発生する変圧器の偏磁を抑えることができる電力変換装置を提供する。

【解決手段】FET110〜113の特性にばらつきがあった場合、1次巻線100に流れる電流に、正又は負の直流成分が含まれるようになる。しかし、制御回路13は、出力側回路12の出力電圧と、2回前のパルス電圧を印加したときに1次巻線100に流れる電流に基づいてパルス電圧を決定する。つまり、1次巻線100に流れる正の電流に基づいて正のパルス電圧を決定し、正の電流を制御する。また、負の電流に基づいて負のパルス電圧を決定し、負の電流を制御する。そのため、最終的に直流成分を抑えることができる。従って、FET110〜113の特性のばらつきに伴って発生するトランスの偏磁を抑えることができる。

(もっと読む)

DC/DCコンバータの制御回路及びDC−DCコンバータ

【課題】出力電流の変動を抑圧するようにDC/DCコンバータを制御する。

【解決手段】帰還電流生成回路14及び合成回路16は、インダクタ電流ILの直流成分を表す第1の帰還電圧VFB1を生成する。リップル信号生成回路15は、入力及び出力電圧に基づいて、インダクタ電流ILの交流成分を表す第2の帰還電圧VFB2を生成する。合成回路15は、第1及び第2の帰還電圧を合成して第3の帰還電圧VFB3を生成する。オン時間調整回路17は、基準電圧VREFと第3の帰還電圧VFB3の比較結果に応じてハイレベル又はローレベルの制御信号HYSOを出力する。ドライバ回路13は、スイッチング素子M1,M2を制御する。リップル信号生成回路15は、制御信号HYSOがローレベルであるとき、入力電圧と出力電圧との差に基づいて第2の帰還電圧を生成し、制御信号HYSOがハイレベルであるとき、出力電圧に基づいて第2の帰還電圧を生成する。

(もっと読む)

ブースト回路とそれを備えるDC−DCコンバータ、電源装置及びブースト回路の動作方法

【課題】入力電圧の瞬断や低下等があった場合でも、入力平滑コンデンサに残存する電圧に拘わらず、ブースト回路の補償動作を迅速に開始させるブースト回路等を実現することを目的とする。

【解決手段】出力電圧が出力設定値より低下したことを検出してDC−DCコンバータに供給する電圧を補償するブースト回路において、入力電圧または入力電流を検出する入力検出部を備え、入力検出部が入力電圧または入力電流が定格値よりも低下したことを検出した場合に、ブースト回路の補償動作を開始するブースト回路とする。

(もっと読む)

電圧制御装置、画像形成装置及び電圧制御方法

【課題】消費電力を抑えつつ、電圧切り替え速度を向上させるとともに、画像形成への悪影響を抑える。

【解決手段】電圧制御装置100は、直流電圧を出力する電圧出力部110と、第1目標電圧よりも高い第1電圧の出力命令である第1電圧出力命令を出力して、前記電圧出力部に前記第1電圧を目指して昇圧させ、前記電圧出力部から出力されている前記直流電圧が前記第1目標電圧に到達する前に、前記第1目標電圧の出力命令である第1目標電圧出力命令を出力して、前記電圧出力部に前記第1目標電圧まで昇圧させるCPU160と、を備える。

(もっと読む)

DC/DCコンバータの制御回路及びDC−DCコンバータ

【課題】出力電圧の変動を抑圧するようにDC/DCコンバータを制御する。

【解決手段】帰還電圧生成回路14及び合成回路16は、インダクタ電流ILの直流成分を表す第1の帰還電圧VFB1を生成する。リップル信号生成回路15は、入力及び出力電圧に基づいて、インダクタ電流ILの交流成分を表す第2の帰還電圧VFB2を生成する。合成回路15は、第1及び第2の帰還電圧を合成して第3の帰還電圧VFB3を生成する。オン時間調整回路17は、基準電圧VREFと第3の帰還電圧VFB3の比較結果に応じてハイレベル又はローレベルの制御信号HYSOを出力する。ドライバ回路13は、スイッチング素子M1,M2を制御する。リップル信号生成回路15は、制御信号HYSOがローレベルであるとき、入力電圧と出力電圧との差に基づいて第2の帰還電圧を生成し、制御信号HYSOがハイレベルであるとき、出力電圧に基づいて第2の帰還電圧を生成する。

(もっと読む)

電源制御回路モジュール

【課題】高い放熱性を有する電源制御回路モジュールを実現する。

【解決手段】電源制御回路モジュール1を構成する積層体900の表面には、電源制御ICが実装されている。電源制御ICのスイッチングレギュレータ用素子101と、インダクタ素子21とを接続する第1の内層電極421、インダクタ素子21とキャパシタ素子31とを接続する第1の内層電極422、スイッチングレギュレータ用素子101とキャパシタ素子31とを接続する第1の内層電極441は、積層体900の上層領域に形成されており、電源制御ICの実装領域と、積層体900の外周壁との間で引き回されている。第1の内層電極421,422,441は、積層体900の中央領域に形成された、制御信号が伝送される第2の内層電極451よりも幅広に形成されている。

(もっと読む)

161 - 180 / 5,031

[ Back to top ]