Fターム[5H740BB01]の内容

電力変換一般 (12,896) | 主回路スイッチング素子の接続と負荷態様 (2,347) | 直列接続 (330)

Fターム[5H740BB01]に分類される特許

1 - 20 / 330

電力変換装置用部品

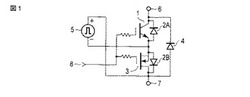

半導体スイッチおよび電力変換装置

【課題】主素子の出力静電容量の増大を防止し、接合容量充電電流に起因するターンオン損失を抑制する半導体スイッチを提供する。

【解決手段】逆導通性能を有し、高耐圧な電圧駆動型スイッチング素子である主素子1と、主素子1に比べ耐圧が低い逆流防止素子3と、主素子1の負極と逆流防止素子3の負極とを接続して主素子1の正極を正極端子とし、逆流防止素子3の正極を負極端子とし、正極端子と負極端子間に負極端子から正極端子に向かう方向が順方向となるように接続し、主素子1と同等の耐圧を有する高速還流ダイオード4と、主素子1の正極に正電圧が印加される方向に接続し、少なくとも主素子1の耐圧より低い電圧パルスを発生するとともに主素子1又は逆流防止素子3がオフする時期と略同期して電圧パルスを出力する予備電圧印加回路5と、を備えた半導体スイッチ。

(もっと読む)

制御回路及び電子機器

【課題】ノーマリーオフ化したGaN−HEMTを電源回路に用いた場合、長期間電源をオフしている間にノーマリーオンに戻るのを防止する制御回路を提供する。

【解決手段】制御回路は、ソース、ゲート及びドレインを有する第1のスイッチング素子と、第2のスイッチング素子を介して前記ゲートに電圧を供給するバッテリーと、第3のスイッチング素子を介して前記ゲートにPWM信号を供給するPWM信号発生回路と、電源がオフの状態で、前記第2のスイッチング素子をオンして前記ゲートに前記バッテリーの電圧を供給すると共に、前記第3のスイッチング素子をオフし、電源がオンの状態で、前記第3のスイッチング素子をオンして前記ゲートに前記PWM信号電圧を供給すると共に、前記第2のスイッチング素子をオフするゲート制御回路とを有する。

(もっと読む)

半導体スイッチング素子の駆動装置

【課題】電圧偏差量または電位量をフィードバックすることなく、複数直列接続された各半導体スイッチング素子の電圧分担を均等化させる。

【解決手段】電圧検出回路7により、直列接続された2つの半導体スイッチング素子A,Bの電圧を、そのうちの片方の半導体スイッチング素子Aの電位を基準にして検出し、比較器10において、半導体スイッチング素子A,Bの電圧を比較し、電圧偏差極性信号をフィードバックする。タイミング制御演算回路12により、1回のスイッチング毎に、前記電圧偏差極性信号に基づいて制御方向を決定し、次回のスイッチング時のゲート信号に対する制御量に対して、決定した制御方向に固定値の制御量を加算し、加算後の制御量を出力すると共に、その加算後の制御量を保持する。そして、タイミング制御回路13により、前記制御量に基づいて、ゲート信号の変化のタイミングを調整する。

(もっと読む)

スイッチング素子の駆動回路およびその製造方法

【課題】電圧制御形の駆動対象スイッチング素子を駆動して且つ集積回路を備える新たな駆動回路およびその製造方法を提供する。

【解決手段】電圧制御形の駆動対象スイッチング素子を駆動して且つ集積回路を備える駆動回路において、前記駆動対象スイッチング素子の開閉制御端子に電荷を充電するための充電経路を備え、前記集積回路には、電流量を規制する内側流通規制要素と、前記充電経路を介した電流の流通および遮断を制御する制御手段と、前記制御手段の出力端子を前記集積回路内の部材に接続することで前記内側流通規制要素を前記充電経路として用いるか前記集積回路の備える外部出力端子に接続するかを切り替える切替回路と、前記集積回路の外部入力端子からの信号に基づき前記切替回路を操作することで前記切り替えを行う操作手段とを備えることを特徴とするスイッチング素子の駆動回路。

(もっと読む)

ゲート駆動回路

【課題】双方向に導通可能なスイッチング素子に逆電流が流れた場合であってもスイッチング素子の損失を低減できるゲート駆動回路を提供する。

【解決手段】双方向に導通可能なスイッチング素子Q1のゲートに正電圧を印加してオンさせ、ゲートに負電圧を印加してオフさせる駆動部2と、スイッチング素子Q1に逆方向電流が流れる前にゲートへの負電圧の印加を解除する負電圧解除部3とを備える。

(もっと読む)

半導体装置

【課題】簡単な回路構成により誤動作を防止できる半導体装置を得る。

【解決手段】パワー素子Q1とパワー素子Q2がトーテムポール接続されている。駆動回路1が入力信号INに応じてパワー素子Q2を駆動し、駆動回路2が入力信号/INに応じてパワー素子Q1を駆動する。駆動回路1は、電源に接続された高圧端子と、低圧端子とを有する。抵抗R1の一端がパワー素子Q2のエミッタに接続され、抵抗R1の他端が駆動回路1の低圧端子に接続されている。スイッチング素子Q3が駆動回路1の高圧端子と抵抗R1の一端との間に接続されている。スイッチング素子Q3は入力信号INに応じてオン・オフする。入力信号INがオフ信号の場合に、駆動回路1は低圧端子の電圧VGNDをパワー素子Q2のゲートに供給してパワー素子Q2はオフする。入力信号INがオフ信号の場合に、スイッチング素子Q3はオンする。

(もっと読む)

半導体素子のゲート駆動方法

【課題】ターンオフスイッチング時に発生するノイズとスイッチング損失のトレードオフ特性を改善する。

【解決手段】半導体素子をターンオフさせるとき、半導体素子のコレクタ・エミッタ間電圧がコレクタ・エミッタ間に印加された直流電圧に達するまでは、前記コレクタ・エミッタ間電圧の変化率を大きくし、半導体素子のコレクタ・エミッタ間電圧が直流電圧に達した後は、前記コレクタ・エミッタ間電圧の変化率を小さくする。

(もっと読む)

加熱定着装置及び画像形成装置

【課題】商用交流電源に重畳するノイズや電圧波形歪みの影響を受けず、正確にゼロクロスタイミングを検知する。

【解決手段】交流電源401から電力供給されるセラミックヒータ109cと、交流電源からセラミックヒータへの給電制御を行うエンジンコントローラ126と、交流電源の電流値を検知し、電流検知信号を出力するフォトカプラ510と、交流電源の電圧のゼロクロスを検知し、ゼロクロス検知信号を出力するフォトカプラ518を備え、エンジンコントローラは、電流検知信号に基づいて、ゼロクロス検知信号のエッジの検出を行わないマスキング区間と前記ゼロクロス検知信号のエッジの検出を行う非マスキング区間を有するマスクパターンを生成し、マスクパターンの非マスキング区間におけるゼロクロス検知信号のエッジをゼロクロスタイミングとして、給電制御を行う。

(もっと読む)

電源スイッチ保護回路及び車載機器

【課題】過電流から電源スイッチ回路を適切に保護する技術を提供する。

【解決手段】電源スイッチ保護回路は、電源スイッチ回路と、第1回路素子及び第2回路素子の両方がオン状態を示す場合に電源スイッチ回路をオン状態とし、第1回路素子及び第2回路素子の少なくとも一方がオフ状態を示す場合に電源スイッチ回路をオフ状態とする電源スイッチ制御回路と、電源スイッチ回路の出力側の短絡を検出し、短絡が検出されているか否かを示しかつ第1回路素子のオフ状態及びオン状態を切り換えるための短絡検出信号を出力する短絡検出回路と、所定時間内における短絡検出信号の状態変化に応じて、短絡が発生しているか否かを判定し、短絡が発生していると判定すると、第2回路素子がオフ状態を維持するように電源スイッチ制御回路を制御する制御部と、を備える。

(もっと読む)

電流制限回路

【課題】ノイズ耐性が高く、且つ、製造プロセス、電源、及び電源電圧が変動するような場合においても精度が高い、出力トランジスタに対する電流制限回路を提供する。

【解決手段】電流制限回路が、基準トランジスタと、基準トランジスタに所定の電流を流す電流源と、出力トランジスタがオンした時の両端の第1の電位差と基準トランジスタの両端の第2の電位差を比較する比較器であって、第1の電位差が第2の電位差よりも大きくなった場合に、出力トランジスタをオフするように制御する電流制限信号を出力する、比較器とを備える。基準トランジスタは、出力トランジスタとは素子サイズの異なる同型のトランジスタであり、基準トランジスタがオンした時のオン抵抗は、出力トランジスタがオンした時のオン抵抗の1/Nの大きさ(Nは1より大きい数)であり、更に、基準トランジスタがオンするように基準トランジスタのゲートにバイアスがかけられている。

(もっと読む)

ゲート駆動回路

【課題】ターンオン時のスイッチング特性が変動せず、また、電流回生時の電力損失を発生せずにスイッチング素子を安定してターンオンさせることができるゲート駆動回路。

【解決手段】ドレインとソースとゲートとを有し且つワイドバンドギャップ半導体かなるノーマリオフ型スイッチグ素子Q1のゲートに制御回路からの制御信号を印加することによりスイッチング素子をオンオフ駆動させるゲート駆動回路であって、制御回路とスイッチング素子のゲートとの間に接続され、コンデンサC1と抵抗R1との直列回路と並列にノーマリオン型スイッチグ素子Q2が接続され、スイッチング素子Q2のゲートはGNDに接続され、スイッチング素子Q1のゲート電圧に応じたゲートバイアス電流を供給し、スイッチング素子Q1のオフ時にはゲート・ソース間を短絡する。

(もっと読む)

半導体装置

【課題】パワーデバイスの誤動作を防ぐ。

【解決手段】直列に接続された2つのパワーデバイスのうち高電位側のパワーデバイスを駆動制御する半導体装置であって、高電位側のパワーデバイスの導通を示す第1状態及び高電位側のパワーデバイスの非導通を示す第2状態を有する入力信号の第1,第2状態へのレベル遷移に対応して、それぞれ第1,第2のパルス信号を発生させるパルス発生回路と、第1,第2のパルス信号を高電位側へレベルシフトして、それぞれ第1,第2のレベルシフト済みパルス信号を得るレベルシフト回路と、第1,第2のレベルシフト済みパルス信号を少なくとも第1,第2のパルス信号のパルス幅分遅延させて、それぞれ第1,第2の遅延済みパルス信号を得る遅延回路と、第1の遅延済みパルス信号をセット入力から入力し、第2の遅延済みパルス信号をリセット入力から入力するSR型フリップフロップとを備える。

(もっと読む)

電源装置の駆動回路及び電源装置

【課題】遷移期間においてハイサイドトランジスタQ1がオンしないようにする。

【解決手段】高電位電源ラインと低電位電源ラインとの間に直列に接続されたハイサイドトランジスタとロウサイドトランジスタと,両トランジスタの接続ノードと出力端子との間に設けられたインダクタとを有する電源装置の前記両トランジスタを駆動する駆動回路であって,前記ハイサイドトランジスタのゲートを駆動する第1のゲートドライバと,前記ロウサイドトランジスタのゲートを駆動する第2のゲートドライバとを有し,前記ハイサイドトランジスタがオンでロウサイドトランジスタがオフの第1の状態から,前記ハイサイドトランジスタがオフでロウサイドトランジスタがオンの第2の状態に遷移する遷移期間で,前記第1のゲートドライバは前記ハイサイドトランジスタのゲートを前記低電位電源ラインの電位より低い第1の電圧に駆動する電源装置の駆動回路。

(もっと読む)

電源回路

【課題】主スイッチング素子の面積を大きくすることなく、ゲートの容量に蓄積された電荷を引き抜く引き抜き期間を短くすることができる電源回路を提供する。

【解決手段】Nチャネル型の主スイッチング素子10と、主スイッチング素子10を制御する駆動回路30と、主スイッチング素子10の第2電極端子に接続される負バイアス回路20とを備える。そして、負バイアス回路20を、接地された第1抵抗21と、当該第1抵抗21と第2電極端子との間に配置されて第2電極端子との接続点の電位を第1抵抗21との接続点の電位より低くする電位降下手段22、23とを有するものとする。また、駆動回路30を第1抵抗21と電位降下手段22、23との接続点に接続する。そして、主スイッチング素子10がオフされたとき、ゲートの容量に蓄積された電荷を駆動回路30および第1抵抗21と電位降下手段22、23との接続点を介して引き抜くようにする。

(もっと読む)

昇圧制御回路

【課題】電源に対して並列に接続された昇圧部およびスイッチ部から成る並列回路においてスイッチ部の故障の有無を的確に検知する。

【解決手段】制御ECU34は、直結スイッチ13のオン及び昇圧回路14の昇圧動作を指示する制御パルスを出力したときに、第1及び第2電圧センサ15,16により検出された入力側電圧および出力側電圧に基づき、出力側電圧が昇圧されている場合、直結スイッチ13はオープン故障であると判定するオープン故障検知モードを有する。制御ECU34は、直結スイッチ13のオフ及び昇圧回路14の昇圧動作を指示する制御パルスを出力したときに出力側電圧が昇圧されていない場合、直結スイッチ13はショート故障または昇圧回路14は故障であると判定するショート故障検知モードを有する。制御ECU34はショート故障検知モードをオープン故障検知モードの実行に先立って実行する。

(もっと読む)

スイッチング素子用ゲート駆動装置

【課題】同時オン防止回路を有し、かつ3レベル電力変換装置の構成部品を少なくし信頼性を向上した3レベル電力変換装置のゲート駆動装置を提供する。

【解決手段】3レベル電力変換装置は、一対の直流電源端子間に順次直列に接続された第一ないし第四の半導体スイッチング素子4〜7をそれぞれ、第一ないし第四のゲート駆動回路28〜31により駆動し、第一及び第二の半導体スイッチング素子4、5のみをオンしたときプラス出力、第二及び第三の半導体スイッチング素子5、6のみをオンしたとき零出力、そして、第三及び第四の半導体スイッチング素子6、7のみをオンしたときマイナス出力を出力する。その際、第一の駆動回路28と第三の駆動回路29、第二の駆動回路30と第四の駆動回路31をそれぞれ同一の基板に実装し、各基板上において、通信線を介して相互に論理回路に接続し、いずれか一方のゲート駆動回路がオンしている時に他方のゲート駆動回路をオフする。

(もっと読む)

出力回路

【課題】貫通電流の発生を防止することのできる出力回路を提供する。

【解決手段】実施形態の出力回路は、出力用NMOSトランジスタN100のドレイン端子に入力電圧VDINが印加され、ソース端子OUTにLC回路およびダイオードDが接続される。この出力回路は、NMOSトランジスタN1およびN2が、出力用NMOSトランジスタN100のソース端子OUTとゲート端子との間に直列に接続され、NMOSトランジスタN3が、NMOSトランジスタN1とNMOSトランジスタN2の接続点と接地電位端子GNDとの間に接続され、制御回路1が、出力用NMOSトランジスタN100が非導通のときに出力用NMOSトランジスタN100のソース端子OUTとゲート端子との間に短絡経路が形成されるようNMOSトランジスタN1〜N3の導通を制御する。

(もっと読む)

負荷駆動回路

【課題】簡単な構成で負荷オープン状態を検出することができる負荷駆動回路を提供する。

【解決手段】電源端子T1に入力される入力電圧Vinよりも低い基準電圧V1と出力端子T2の電圧Voutとを比較する第1のコンパレータ8と、スイッチング素子2がオフ状態で、且つ負荷オープン状態である場合に、出力端子T2の電圧Voutを基準電圧V1よりも高く、且つ入力電圧Vinよりも低いclamp電圧にクランプするクランプ回路7とを備えることにより、第1のコンパレータの出力によって、負荷オープン状態を検出する。また、入力電圧Vinよりも低く且つclamp電圧よりも高い基準電圧V2と出力端子T2の電圧Voutとを比較する第2のコンパレータ9を備えることにより、第1のコンパレータ及び第2のコンパレータ9の出力によって、負荷オープン状態と出力天絡状態とを検出する。

(もっと読む)

インバータ装置

【課題】デッドオフ時間中の還流電流の損失を小さくすると共に、寄生ダイオードの逆回復時間を短くすることが可能なインバータ装置を提供する。

【解決手段】4つの双方向スイッチ素子Q1〜Q4でブリッジ回路を構成し、互いに直列接続されていない2組のスイッチ素子Q1とQ4及びQ2とQ4を、デッドオフ時間ΔTを介して交互にオン及びオフさせる。デッドオフ時間中ΔT、そのデッドオフ時間の直前に非導通であったスイッチ素子の組を一時的に導通させて還流電流を流す。

(もっと読む)

1 - 20 / 330

[ Back to top ]