Fターム[5J022BA05]の内容

アナログ←→デジタル変換 (13,545) | 目的、効果 (2,366) | 高速化 (265)

Fターム[5J022BA05]に分類される特許

141 - 160 / 265

任意波形発生器および半導体テスト装置

【課題】D/A変換器の出力信号の直線性との乖離による誤差電圧を高精度に補正されたアナログ電圧を得ることができ、テスト時間を短縮できる任意波形発生器および半導体テスト装置を提供する。

【解決手段】同一特性を有し共通のクロックで駆動される粗調整出力系統と微調整出力系統のD/A変換器と、粗調整出力系統のD/A変換器に入力されるデジタルデータを1クロック分遅らせるタイミング調整手段と、粗調整出力系統のD/A変換器の出力誤差電圧を補正する校正データが粗調整出力系統のD/A変換器の理論値に対するデジタルデータをアドレスと見立てて微調整出力系統のD/A変換器に入力されるデジタルデータとなるように書き込まれたデータ補正部と、粗調整出力系統のD/A変換器の出力電圧と微調整出力系統のD/A変換器の出力電圧を加算出力する加算器とで構成する。

(もっと読む)

増幅回路、デジタルアナログ変換回路及び表示装置

【課題】電圧信号を出力する実質駆動期間が、サイクル動作によって短縮されないデジタルアナログ変換器と該デジタルアナログ変換器を備えたドライバを提供する。

【解決手段】1データ線の駆動に対して第1及び第2のシリアルDAC(110、210)と増幅回路(10)を備え、第1のデータ期間において、第1のシリアルDACが、第1のデータ期間に入力された第1のデジタル信号を第1の信号に変換し、第2のシリアルDACが、第1のデータ期間の1つ前のデータ期間に入力されたデジタル信号を変換した信号を保持し、増幅回路が第2のシリアルDACに保持される信号をデータ線に増幅出力する。第1のデータ期間の後に続く第2のデータ期間においては、第2のシリアルDACが、第2のデータ期間に入力された第2のデジタル信号を第2の信号に変換し、第1のシリアルDACが、第1のデータ期間に変換した前記第1の信号を保持し、増幅回路(10)は第1のシリアルDACに保持される第1の信号をデータ線に増幅出力する。

(もっと読む)

LSIテスタ

【課題】より多種類のDUTのテストに柔軟に対応でき、ソフトウェアによる信号処理に比べて格段の高速処理が行えるLSIテスタを実現すること。

【解決手段】アナログ信号波形を出力するLSIの良否をテストするLSIテスタにおいて、被測定対象LSI(DUT)の出力信号を処理する演算処理部の少なくとも一部がFPGAによる論理合成で構成されたことを特徴とするもの。

(もっと読む)

アナログ−デジタル変換

【課題】A−D変換を提供すること。

【解決手段】高い周波数信号のA−D変換に関する改善を開示する。複数のA−D変換器(ADC)と分布サンプリング・システム(分布SS)の使用によって達成される。この組合せによって従来デバイスの使用が可能になり、非常に高い周波数の正確なサンプリングも可能になる。分布SSは、複数のサンプリングに複数のADCを使用して複数のサンプリングを行い、各サンプリングは一定時間量だけ連続してずれている。各ADCはCPUを有する。デジタル出力値はすべて同じまたは異なる周波数でのサンプリング結果とすることができる。分布SSの型には、直列接続の複数の細長い配線パターン、直列接続の複数のインバータ対、特定誘電率材料デバイス、及びシーケンサ又はマルチプライヤがある。また、可変サイズ・アパーチャ・ウィンドウ(VSAW)を含み、サンプル・パルスの幅が可変クロック機構により制御される。

(もっと読む)

アナログ−デジタル変換器システム

【課題】アナログ−デジタル変換器システムを提供すること。

【解決手段】複数のアナログ−デジタル変換器が分布サンプリング・システムと共に使用される。複数の変換器と分布サンプリング・システムのこの組合せは、0.18ミクロンのシリコンの処理などの、従来デバイス処理を使用することを可能にし、また非常に高い周波数の入力信号の正確なサンプリングを可能にする。分布サンプリング・システムは、各サンプリングに異なるADCを使用して入力信号の複数サンプリングを可能にし、各サンプリングは、先行する最後のサンプリングから特定の時間量だけ連続的にずれている。多数のADCからの各サンプリングは、組み合わされ、単一の連続的なデジタル出力信号を形成する。分布サンプリング・システムのタイプは、直列に相互接続された多数の細長い配線パターン、特定の誘電率材料デバイス、およびシーケンサまたはマルチプライヤがある。

(もっと読む)

アナログデジタル変換システム

【課題】複数のAD変換器を搭載した場合、回路面積が増大してしまう。

【解決手段】AD変換システム100は、複数チャネルの入力アナログ信号を、上位ビットから下位ビットに向けて複数回の変換処理により、それぞれデジタル信号に変換する。第1AD変換部10は、初回の変換処理を行う。第2AD変換部20、第3AD変換部30および第4AD変換部40は、第1AD変換部10により変換されたビットより下位の残りのビットを、複数回に分けて変換する。第1AD変換部10は、第2AD変換部20、第3AD変換部30および第4AD変換部40により共有される。

(もっと読む)

増幅回路及び増幅回路装置

【課題】 サンプル時の増幅器の負荷容量を低減し、高速動作が可能な増幅回路及びそれを用いた増幅回路装置を提供する。

【解決手段】 差動入出力端子と中点電位入力端子とを備えた増幅器1と、差動入力端子におけるサンプル時のオフセット電圧を記憶しホールド時に出力する第1及び第2のオフセット電圧モニタ・出力ブロック15,16と、サンプル時に一対の信号入力端子に接続され、ホールド時に各オフセット電圧モニタ・出力ブロックから出力されるオフセット電圧に切り替えられる一端と、サンプル時に基準電圧に、ホールド時に差動入力端子に切り替えられる他端を有する第1及び第2の入力容量11,12と、差動入力端子に接続された一端と、サンプル時に一対の信号入力端子に、ホールド時に差動出力端子に切り替えられる他端を有する第1及び第2の帰還容量13,14と、サンプル時に増幅器のユニティンゲインを設定する設定部とを備えて増幅回路を構成する。

(もっと読む)

超高速AD変換におけるビットアラインメント補正機構

【課題】 AD変換器から出力された複数ビットの量子化データをデジタル処理する場合におけるビットアラインメントを、高度なタイミング制御技術や、デマルチプレクサ素子のリセット回路を用いることなく実現する。

【解決手段】 AD変換器の識別不能領域(不感帯)に一致する電位の直流を入力信号としてAD変換器に入力した場合における量子化データのビット分布が、ビットアラインメントが正しく達成されている場合のみ特定の値をとることを利用し、AD変換器から出力された複数ビットの量子化データについて、各ビット間の相対遅延を1サンプル時刻単位で変化させながら、そのビット分布を計測して、ビット分布が特定の値となる相対遅延量を検索することにより、ビットアラインメントが達成される。

(もっと読む)

アナログ‐デジタル変換器及びその動作方法、ランプ発生器及びその動作方法並びに撮像装置

【課題】ランプ発生器の精度を良好にする。

【解決手段】制御回路によりランプ発生器を制御してこのランプ発生器がランプ変調されたアナログランプ出力を発生するようにし、各アナログランプ出力に対応するデジタル符号を発生するようにする制御回路と、アナログ入力信号とアナログランプ出力とを受けるように接続された比較回路は、受けたアナログ入力信号がアナログランプ出力に等しくなった際に信号を発生するようにしたアナログ‐デジタル変換器であって、前記ランプ発生器が、ランプ符号を発生する曲線発生器と、このランプ符号から行及び列アドレスとロック信号とを発生させるアドレス回路と、各々が電圧出力を有する複数のユニットセルのアレイであって、行及び列アドレスとロック信号とに基づくアナログランプ出力を発生する当該アレイとを有するようにする。

(もっと読む)

D/A変換器

【課題】セトリング時間を短縮したD/A変換器を提供すること。

【解決手段】本発明の一態様に係るD/A変換器は、抵抗値RMの複数の上位ビット用抵抗が直列に接続され、当該複数の上位ビット用抵抗によって、上位ビット用基準電圧を分圧して、入力されたデジタル信号の上位ビットに対応するアナログ信号を出力する上位ビット用DACと、前記上位ビット用抵抗の抵抗値RMよりも小さい抵抗値RSの複数の下位ビット用抵抗が直列に接続され、当該複数の下位ビット用抵抗によって、下位ビット用基準電圧を分圧して、入力されたデジタル信号の下位ビットに対応するアナログ信号を出力する下位ビット用DACと、前記上位ビット用DACから出力されるアナログ信号と前記下位ビット用DACから出力されるアナログ信号とを加算する加算器とを備える。

(もっと読む)

トラックアンドホールド回路

【課題】 トラックアンドホールド回路の歪特性を改善し、高精度なトラックアンドホールド回路を提供する。

【解決手段】 クロック信号生成回路1からのクロック信号に応じてオン/オフ制御され、入力信号の電圧を伝達するトランジスタMSと、トランジスタMSにより伝達された入力電圧を保持する保持容量CHと、トラックモード時はトランジスタMSのボディ電位を入力電圧に応じて変化させるとともに、ホールドモード時はボディ電位を一定に保つよう制御するボディバイアス制御回路2とを備え、トラックモード時においてトランジスタMSのオン抵抗の抵抗値が変動するのを防止し入力電圧に依らず一定値を保つことができるようにする。

(もっと読む)

D/A変換器

【課題】出力応答時間の短縮を図ることができるD/A変換器を提供すること。

【解決手段】第1スイッチ回路11aのスイッチ素子SW0a〜SW15aは、第1端子が共通接続されるとともにその第1端子が高電位電源VRHに接続され、第2スイッチ回路11bのスイッチ素子SW0b〜SW15bは、第1端子が共通接続されるとともにその第1端子が低電位電源VRLに接続される。第1分圧回路12aの抵抗素子Raは、スイッチ素子SW0a〜SW15aの第2端子間に接続され、第2分圧回路12bの抵抗素子Rbは、スイッチ素子SW0b〜SW15bの第2端子間に接続される。制御回路13は、デジタル信号D0〜D3に基づいて、第1スイッチ回路11aのスイッチ素子SW0a〜SW15aのうちの1つをオンするとともに第2スイッチ回路11bのスイッチ素子SW0b〜SW15bのうちの1つをオンするようにした。

(もっと読む)

二重静的ラダーを備えた並列アナログ−デジタル変換器

本発明は、高速アナログデジタル変換器に関し、特に、「フラッシュ」タイプの少なくとも1つの変換段を有する高速アナログデジタル変換器に関する。本発明による変換器は、4つの入力部を備えたN個の差動増幅器を用いる。ランクjの増幅器は、変換される入力電圧Vep−Venを2つの第1の入力部で受信し、2つの他の入力部で基準電位差を受信する。基準電位差は、並列で動作する同一の、かつ高電圧源と低電流源との間で電力を供給される抵抗器ネットワークにおける2つのタップ間で得られる。増幅器用のタップは、それぞれ、第1のネットワークにおけるランクjのタップPjおよびおよび第2のネットワークにおけるランクN−j+1のタップP’N−j+1である。これは、差動増幅器が、抵抗器ネットワークから取り出された入力電流を消費するという事実による一次および二次非線形効果を低減する。非常に高解像度(12〜14ビット)の高速変換器に適用される。 (もっと読む)

A/D変換装置

【課題】位相余裕が大きく、安定なデータ取込みが可能なA/D変換装置を提供する。

【解決手段】A/D変換器22(1)〜22(4)からデータ信号Da〜Ddとともにそれぞれ出力されるデータクロックCa〜Cdに対して、サンプリング順が奇数番目のデータクロックCa、Ccに対してはそのままラッチ回路26(1)、26(3)でラッチし、そのラッチ出力を書込許可信号Ea、Ecとして記憶部28に出力し、偶数番目のデータクロックCb、Cdに対してはその反転出力をラッチ回路26(2)、26(4)でラッチし、そのラッチ出力を書込許可信号Eb、Edとして記憶部28に出力し、それぞれのデータに対する記憶処理を行うことで、データクロックの周期の(N/2+1)/Nの位相余裕を生じさせている。

(もっと読む)

アナログデジタル変換回路

【課題】低消費電力化を図り、従来技術(FSPI)のように、入出力端子間の極性を入れ替えることなくエラー電圧を低減するパイプライン型ADCの提供。

【解決手段】n番目のステージとn+1番目のステージのローカルA/Dを構成する回路ブロック4、5間で増幅器(op amp)を共有し、n番目のステージのサンプリング容量を複数に分割し、複数に分割したnステージのサンプリング容量の一部(Cf12)をn+1番目のステージのサンプリング容量とする。

(もっと読む)

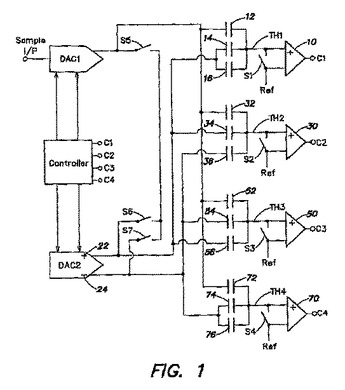

アナログ−デジタルコンバータ

第一および第二デジタル−アナログコンバータDAC1およびDAC2の出力が組み合わせ回路の中で結合され複数の識別しきい値を形成するアナログ−デジタルコンバータに関する。これは2もしくはそれ以上のビットが一度の判定で決定されることを可能にする。  (もっと読む)

(もっと読む)

アナログデジタル変換器

【課題】 演算時間の早いアナログデジタル変換器を提供する。

【解決手段】 外部入力端子1、参照電圧選択部2〜4、キャパシタ群7、第1のスイッチ群8、第2のスイッチ群9、演算増幅部5、冗長ビットを有するサブA/Dコンバータ6、およびデジタル符号化回路15を有するA/Dコンバータとして構成される。

アナログ信号は、キャパシタ群7にサンプリングされ、電荷として保持される。そして、各構成要素を用いて、MDAC演算とA/D変換を繰り返す。この結果、キャパシタ群7に保持された電荷を逃さずにA/D変換を行う。

このように、アナログ信号を最初にサンプリングした電荷を繰り返して用いること、および、演算の冗長性を有することから、正確な演算およびセトリングが必要とならないため、A/D変換に要する時間を高速化することが可能となる。

(もっと読む)

スイッチトキャパシタ型D/A変換器、液晶ディスプレイの駆動回路

【課題】 消費電力を増大させることなくD/A変換処理に要する時間の短縮化が図られるスイッチトキャパシタ型D/A変換器を提供する。

【解決手段】 デジタルデータに対応した入力電圧が与えられ、当該入力電圧に応じた電荷量を充電するキャパシタCx、Cyと、入力端子に入力される信号に基づいて生成される増幅信号を個々に独立して出力制御可能な第1増幅出力端子To1及び第2増幅出力端子To2を備える演算増幅器A21とを有し、変換処理中には第1増幅出力端子To1から増幅信号を出力し、変換処理完了後に第2増幅出力端子To2から増幅信号を出力スイッチSw6を介して出力させる。

(もっと読む)

電荷再分配型D/A変換器

【課題】 スイッチトキャパシタ回路のスイッチからオンオフ動作時に生じる電荷の注入抽出に起因して生じるD/A変換誤差を抑制可能な電荷再分配型のD/A変換器を提供する。

【解決手段】 一方端が基準電圧供給ノードN1と接続するキャパシタC1と、一方端が基準電圧供給ノードN2と接続するキャパシタC2と、一方端がキャパシタC1の他方端と接続し、他方端が出力ノードN0と接続するスイッチS1と、一方端がキャパシタC2の他方端と接続し、他方端が出力ノードN0と接続するスイッチS2と、一方端が出力ノードN0と接続するスイッチS3と、一方端がスイッチS3の他方端と接続し、他方端が基準電圧供給ノードN3と接続するインピーダンス整合用スイッチS4を備え、基準電圧供給ノードN1〜N3の何れか1つからディジタル入力信号をシリアル受信し、出力ノードN0からディジタル入力信号のデコード結果に対応するD/A変換値を出力する。

(もっと読む)

クロック信号生成装置及びアナログ−デジタル変換装置

【課題】互いに同じタイミングで反転した信号波形を有する2つのクロック信号を出力するクロック生成装置を提供する。

【解決手段】クロック信号生成装置は、第1、第2及び第3のDフリップフロップを備え、第1のD入力端子への入力信号を出力する第1の出力端子と、第1のD入力端子への入力信号を反転出力すると共に、出力を第1のD入力端子に入力する第1の反転出力端子とを備え、第2のDフリップフロップは、第1のDフリップフロップの第1出力端子からの出力を入力する第2のD入力端子と、第2のD入力端子への入力信号を第1出力として出力する第2の出力端子とを備え、第3のDフリップフロップは、第1のDフリップフロップの第1反転出力端子からの出力を入力する第3のD入力端子と、第3のD入力端子への入力信号を第2出力として出力する第3の出力端子とを備え、第1出力と第2出力とは互いに同じタイミングで反転した信号波形を有する。

(もっと読む)

141 - 160 / 265

[ Back to top ]