Fターム[5J022BA05]の内容

アナログ←→デジタル変換 (13,545) | 目的、効果 (2,366) | 高速化 (265)

Fターム[5J022BA05]に分類される特許

61 - 80 / 265

アナログ−デジタル変換器

【課題】簡単な構成で高速性、高精度および低消費電力を満たすSAR ADCの実現。

【解決手段】多ビットデジタル信号に応じて参照アナログ信号を出力するDAC14と、入力アナログ信号Vinを参照アナログ信号と比較する第1および第2のコンパレータ21,22と、第1と第2のコンパレータの一方の比較結果を選択する選択回路25と、選択した比較結果に基づいて、複数のステップで参照アナログ信号が入力アナログ信号に近づくように多ビットデジタル信号を順に変化させる制御回路23と、を備えるアナログ−デジタル変換器であって、制御回路は、複数のステップの途中の中間ステップまで第1のコンパレータの比較結果を選択し、中間ステップ以後は第2のコンパレータの比較結果を選択するように選択回路を制御し、多ビットデジタル信号のビット値を、非2進アルゴリズムに従って変化させる。

(もっと読む)

アナログ−デジタル変換器

【課題】高速動作可能な逐次比較型ADCの精度の向上。

【解決手段】サンプリング時にアナログ入力信号が印加される入力端子と、基準電位に接続される基準端子と、を有し、サンプリング時にアナログ入力信号の電圧に対応した電荷量を保持する入力信号容量Csと、サンプリング時に参照電圧の電圧に対応した電荷量を保持し、各参照容量の2つの端子は入力端子と基準端子に順接続状態または逆接続状態で接続可能な1個以上の参照容量23-1,23-10と、入力端子の電圧が基準電位より高いか低いかを判定するコンパレータ12と、判定結果に基づいて、入力端子の電圧が基準電位に近づくように、1個以上の参照容量の接続状態を選択しながら順次接続し、コンパレータの判定結果を合わせた結果からデジタル値を算出する制御回路と、を備えるAD変換器であって、入力信号容量および1個以上の参照容量の容量値は、非2進で設定されている。

(もっと読む)

ΔΣAD変換器

【課題】高分解能のAD変換結果を短時間で得ることを可能とするΔΣAD変換器を実現する。

【解決手段】アナログ入力信号とフィードバック回路のDA変換器の出力信号との差を積分する積分器と、この積分器の積分結果を入力するコンパレータと、このコンパレータの出力をカウントしたデジタル出力信号を前記DA変換器に入力するカウンタとを具備するΔΣAD変換器において、

前記フィードバック回路に設けた多ビットDA変換器と、この多ビットDA変換器の多ビット入力をコントロールし、逐次比較型AD変換器またはΔΣAD変換器として動作させる制御ロジックとを備え、

前記制御ロジックは、前記多ビット入力の上位所定ビットを逐次比較型AD変換動作で決定し、下位所定ビットをΔΣAD変換動作により決定することを特徴とするΔΣAD変換器。

を備える。

(もっと読む)

種々の電荷サンプリング回路

【課題】改善されたサンプリング回路とアナログ信号のサンプリング方法を提供する。

【解決手段】制御信号発生器4を備え、サンプリング段階で制御信号発生器4からのサンプリング信号に応じてスイッチ2により積分器3へのアナログ入力信号を制御して、積分器3で積分する電荷サンプリング(CS)回路1であり、アナログ入力信号の電流を積分して積分電荷を生成し、サンプリング段階の終わりに比例電圧または電流サンプルを信号出力に生成する。

(もっと読む)

ビルドイン負荷減衰器を備えた広帯域デジタルアナログ変換器

デジタルアナログ変換のための回路が説明される。その回路は、デジタルアナログ変換器(DAC)を備える。DACは、ダブルカスケード電流源と差動電流モードスイッチ(DCMS)とを備える。回路は、差動電流(DC)オフセットステージをさらに備える。回路は、また、負荷減衰器を備える。ダブルカスケード電流源は、DCMSとレール電圧との間にあるとしてもよい。 (もっと読む)

カウンタ回路、アナログデジタルコンバータ、カウンタ回路とアナログデジタルコンバータを備えた装置及びカウンティング方法とアナログデジタル変換方法

【課題】カウンタ回路、これを含む装置及びカウンティング方法を提供すること。

【解決手段】

カウンタ回路はバッファ部及びリップルカウンタを含む。バッファ部はカウンティング動作の終了時点から少なくとも1つの入力クロック信号をラッチして少なくとも1つの下位ビット信号を発生する。リッブルカウンタは下位ビット信号のうち1つに相応するラッチ出力信号に応答して順次にトグリング(toggling)する上位ビット信号を発生する。カウンタ回路は入力クロック信号のサイクル周期ごとに2回以上のカウンティングを遂行して向上した動作速度及び動作マージンを有し、ビット信号のトグリング回数を減らし消費電力を低減する。

(もっと読む)

アナログデジタル変換回路およびそれを搭載した撮像装置

【課題】シングルスロープ型A/D変換回路にて、回路規模の増大を抑制しながら、変換時間を短縮する。

【解決手段】傾き調整回路10は、固定の傾きで電圧レベルが上昇または下降するランプ波電圧を受け、そのランプ波電圧の傾きを調整して出力する。コンパレータCPは、デジタル値に変換すべきアナログ電圧と、傾き調整回路10から入力されるランプ波電圧とを比較する。デジタル処理回路20は、コンパレータCPの出力が反転したタイミングに応じて、アナログ電圧に対応するデジタル値を決定する。

(もっと読む)

A/Dコンバータ

【課題】A/D変換時間をより短くする。

【解決手段】A/Dコンバータ20は、A/D変換対象である第1の信号電圧の1つ前の第2の信号電圧を保持する保持回路23と、第1の信号電圧から第2の信号電圧を減算して得られる差分に基準電圧を加算する演算回路21と、第1の信号電圧が第2の信号電圧より高いか否かを判定する判定回路22と、第1の信号電圧が第2の信号電圧より高い場合に基準電圧を初期値として上昇し、第1の信号電圧が第2の信号電圧より低い場合に基準電圧を初期値として下降する比較電圧を生成する生成回路27と、演算回路21による演算値と比較電圧とを比較するコンパレータ24と、コンパレータ24による比較結果が一致するまでの期間をデジタル値に変換する変換回路31とを含む。

(もっと読む)

逐次比較型A/D変換器および撮像装置

【課題】逐次比較型A/D変換器において、オーバーサンプリングを行う場合の処理にかかる時間、ひいてはA/D変換の変換時間を短縮する。

【解決手段】オーバーサンプリングを行う際に、1回目のA/D変換処理では、N回のステップでアナログ信号についてNビットのデジタル値を求める。そして、2回目以降のA/D変換処理では、1回目のA/D変換処理で得たNビットのデジタル値の上位nビットについてはA/D変換処理を行わずにそのまま固定とし、(N−n)ビット以下の下位ビットから、即ちビットの途中からA/D変換を開始する。

(もっと読む)

信号量子化装置、方法、プログラム及びその記録媒体

【課題】信号量子化装置の量子化パラメータを短時間で最適化する技術を提供する。

【解決手段】複数の量子化部11,12,…,1Wの閾値は第一基準値M1を基準として第一間隔d1で広がっており、上記複数の量子化部11,12,…,1Wの第一基準値M1は第二基準値M2を基準として第二間隔d2で広がっているとして、第二基準値M2及び第二間隔d2の2つのパラメータを最適化することにより、量子化の性能を高くする。最適化の対象となるパラメータの数を減らして最適化のために探索する必要がある空間を小さくすることにより、最適化にかかる時間を短くすることができる。

(もっと読む)

電圧発生回路、デジタルアナログ変換器、ランプ波発生回路、アナログデジタル変換器、イメージセンサシステム及び電圧発生方法

【課題】抵抗ラダー型電圧発生回路において、抵抗とスイッチの数を増やすことなく、発生する電圧波形の分解能を上げてその電圧波形の傾斜を従来よりも大きくすると共に、ビット数が増大しても、アナログデジタル変換期間の増大を招かないようにする。

【解決手段】抵抗ラダー回路に接続される複数個のスイッチのうち、連続する(k+1)個のスイッチの中のk個を同時オン状態になるよう制御すると共に、前記kを時間的に切り替える。これにより、小さな傾斜の電圧波形から大きな傾斜の電圧波形まで傾斜の異なる電圧波形が任意が得られる。また、この電圧発生回路をランプ波発生回路として用いて、ランプ波の傾斜をダイナミックに切り替えれば、イメージセンサの高速化が実現される。

(もっと読む)

AD変換器

【課題】簡単な構成で特殊な電子部品を必要とせず、精度・安定性の高いA/D変換器を提供する。

【解決手段】入力信号源を切り替えるためのアナログマルチプレクサ2と、このアナログマルチプレクサ出力をサンプリングするスイッチ5と、サンプリングされた電圧信号を保持するコンデンサ6と、このコンデンサ6に充電された電荷を一定速度で放電させるための定電流回路7と、一定速度で放電する電荷を時間間隔信号に変換するコンパレータ回路8と、その時間間隔信号を計数しデジタル値を得るカウンタ9と、スイッチ5を制御するデジタルコントローラ10とを設け、入力信号値とその計測値とから演算により未知電圧のデジタル値を得られるようにする。

(もっと読む)

イメージセンサ用A/D変換装置

【課題】

高速・高分解能で、かつ固定パターン雑音なども除去するノイズリダクション機能を有したカラムA/D変換器を小さな回路規模で提供する。

【解決手段】

各カラムA/D変換器は、各々に共通に供給される参照電圧群の中から、それぞれのカラムA/D変換器に入力される各センサ信号電圧を挟み込む2つの参照電圧を選択して出力するデュアル出力型のD/A変換器と、その2つの参照電圧をフルスケールとする電荷再分配型のD/A変換器を併用することで、小さな回路規模で高速・高性能のカラムA/D変換器を実現する。さらにその高速変換性を生かし、A/D変換後のデジタル演算によってノイズリダクションを行う。

(もっと読む)

加速されたアナログ/デジタル変換のための方法およびシステム

アナログ/デジタル信号変換と関連付けられた加速処理のための技法を開示する。加速処理は、種々の実施形態におけるアナログ/デジタル変換器と併用される、サンプルアンドホールド回路およびトラックアンドホールド回路のために提供される。短縮サンプリング状態、短縮初期化状態、または両方が、種々の実施形態において採用される。信号を待機する必要性を回避し、所定の公差内に落ち着かせるように、処理を加速化することによって、異なるタイプのエラーが、発生する場合がある。そのようなエラーは、較正の間に判定され、将来の読み出しおよびエラー補償のために記憶される。オンライン較正およびオフライン較正のための技法を開示し、これにより、較正は、正常信号変換処理に影響を及ぼす場合があり、または及ぼさない場合がある。本明細書に開示される技法は、アナログ/デジタル変換における広範囲な可用性を見出し、種々の状況において、より高速な処理をもたらす。  (もっと読む)

(もっと読む)

線形性改善回路、ΣΔA/D変換器、および受信装置

【課題】バイナリコードで演算する加算器が不要で、高速、低消費電力で動作することが可能な線形性改善回路、ΣΔA/D変換器、および受信装置を提供する。

【解決手段】線形性改善回路10は、nビットのA/D変換器の前回の出力コードに応じた第1シフト量を生成する第1シフト量生成部12と、入力コードデータを、供給される第1シフト量をもってビットシフトして出力する第1シフタ回路13と、第1シフタ回路の出力を格納し、格納データを第1シフタ回路の入力コードデータとして出力して第1シフタ回路とループ回路を形成し、かつ、格納コードデータを第2シフト量として出力するレジスタと、A/D変換器の出力コードを供給される第2シフト量をもってビットシフトしてnビットのD/A変換器に出力する第2シフタ回路16と、を有する。

(もっと読む)

多重化信号調整器

【課題】信号調整回路がアンチエイリアシングフィルタおよびA/D変換器を時分割多重する。

【解決手段】複数の第1層のマルチプレクサは各々複数のセンサからの複数のACまたはベースバンド入力信号の間を複数のアンチエイリアシングフィルタのうちの1つに時分割多重する。第2層のマルチプレクサはその入力を第1層のマルチプレクサの出力から選択する。第2層のマルチプレクサの出力が高速A/D変換器に供給される。したがって、A/D変換器は第2層のマルチプレクサによって時分割多重される。このように、複数のセンサは単一のA/D変換器を共有することができる。マルチプレクサおよびアンチエイリアシングフィルタに整定時間を与えた後、入力信号の複数のサンプルが、例えば1周期の間に、取り込まれる。

(もっと読む)

固体撮像装置および駆動方法

【課題】AD変換期間を短縮し高速化と省電力化を実現させる。

【解決手段】未受光の画素回路11から出力されるリセット成分と参照信号RAMPとを比較器21で比較しながら、比較器21が所定の比較結果を示すまでカウンタ22でクロックCK0をダウンカウントし、ダウンカウント後のカウンタ22の値をラッチ24に保持する。ラッチ24に保持された値をカウンタ22にプリセットした後、受光後の画素回路11から出力される信号成分と参照信号RAMPとを比較器21で比較しながら、比較器21が所定の比較結果を示すまでカウンタ22でクロックCK0をアップカウントし、アップカウント後のカウンタ22の値を、画素回路11の受光量を表すデジタル値として出力する。

(もっと読む)

電圧制御遅延発生器セル、電圧制御遅延発生器およびアナログ・ディジタル変換器

【課題】入力のアナログ電圧範囲を一定のまま、広帯域化とサンプリングレートの高速化が可能なアナログ・ディジタル変換器を提供する。

【解決手段】入力したアナログ電圧と複数(例えば4個)の定電流源から電流スイッチを介して供給した電流によりキャパシタが生成したランプ電圧との比較結果をストップパルス信号stopとして出力する電圧制御遅延発生器セルVCDG_0〜3を、前記定電流源の個数と同数並列配置し、制御回路CTLの制御により、ランプ電圧の放電後、まず、各VCDG_0〜3で異なる個数の電流スイッチをオンし、さらにスタートパルス信号startの立上り時に各VCDG_0〜3の全電流スイッチをオンし、ランプ電圧を各キャパシタに生成する。各VCDG_0〜3のストップパルス信号stop0〜3の出力遅延時間を時間ディジタル変換器TDC_0〜3でディジタルデータに変換し、エンコーダENCにて所定のコードに変換する。

(もっと読む)

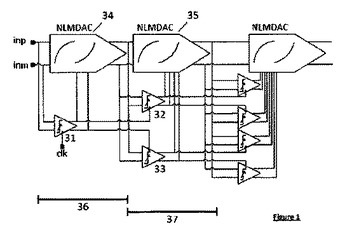

インターリーブ型パイプライン型バイナリーサーチA/D変換器

本発明は、入力信号を所定の複数の閾値のうちの少なくとも異なる2つと比較するための調整可能な上記複数の閾値を有する複数の比較手段と、複数の増幅回路とを備えたアナログ入力信号をデジタル信号に変換するためのパイプライン型アナログからデジタルへの変換器(ADC)であって、上記複数の比較手段は階層的ツリー構造を形成するように設けられ、上記階層的ツリー構造は複数の階層的レベルを有し、上記階層的レベルのうちの少なくとも1つが上記複数の増幅回路のうちの少なくとも1つの増幅回路と関連し、上記少なくとも1つの増幅回路は次の階層的レベルにおいて少なくとも1つの比較手段の入力を生成し、上記複数の階層的レベルは先行する階層的レベルの非線形歪みが除去されるように、前の階層的レベルの出力に従って上記調整可能な閾値を設定するための手段を備えたパイプライン型ADCに関する。  (もっと読む)

(もっと読む)

サンプリング/量子化変換器

特に、連続時間連続可変信号を、サンプリングされ量子化された信号に変換するシステム、方法及び技術が提供される。代表的な一実施形態によれば、装置は、各々が別個の処理ブランチにあり、かつ複数の入力と出力とを含む加算器を有する複数の量子化ノイズシェイピング連続時間フィルタを含み、入力信号は加算器の入力のうちの1つに結合され、加算器の出力は第1のフィルタを介して加算器の入力のうちの1つに結合され、同一の処理ブランチにおけるサンプリング/量子化回路の出力は、第1のフィルタとは異なる伝達関数を有する第2のフィルタを介して加算器の入力のうちの1つに結合される。  (もっと読む)

(もっと読む)

61 - 80 / 265

[ Back to top ]