Fターム[5J022BA05]の内容

アナログ←→デジタル変換 (13,545) | 目的、効果 (2,366) | 高速化 (265)

Fターム[5J022BA05]に分類される特許

21 - 40 / 265

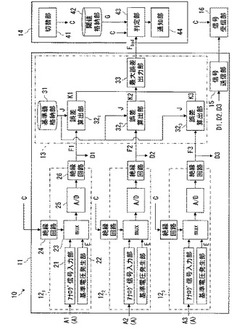

アナログ信号の入力装置及びその入力診断方法

【課題】多チャンネルのアナログ信号の診断処理を高速に実行するアナログ信号の入力装置及びその入力診断方法を提供する。

【解決手段】アナログ信号の入力装置10は、外部入力したアナログ信号A及び発生させた基準電圧Eのうちいずれかを出力するマルチプレクサ23と、マルチプレクサ23が出力した信号をデジタル変換するA/D変換部25と、マルチプレクサ23及びA/D変換部25が設けられている複数のチャンネル12と、各々のチャンネル12においてデジタル変換された複数の基準電圧Fから最悪値Fbadを抽出する信号抽出部13と、複数のチャンネル12及び信号抽出部13が設けられているセグメント11と、複数のセグメント11の各々から出力される複数の最悪値Fbadを閾値Gと対比して各々のセグメント11を単位にアナログ信号Aの入力診断をする診断部14と、を備えている。

(もっと読む)

データ収集装置、データ収集方法および計測装置

【課題】センサからの計測信号を高速かつ正確にA/D変換を行うことができるデータ収集装置およびデータ収集方法、およびデータ収集装置を組み込んだ計測装置を提供する。

【解決手段】データ収集装置は、計測センサにおいて第1クロック信号に基づいて計測条件が順次周期的に切り替わることで得られる、前記計測条件に対応する計測信号が連なった一連の計測信号の入力を受け、第2クロック信号のタイミングでA/D変換を行い順次レジスタに重ね書きして一時記憶するA/D変換ユニットと、前記第1クロック信号に基づいて生成されるサンプリングパルスのタイミングで、レジスタに一時記憶した計測信号を読み出し、前記サンプリングパルスのパルス発生回数に応じて定まる格納位置に記憶するメモリと、を有する。計測装置は、例えば、計測センサとして用いるレーダと、上記データ収集装置とを含むレーダ装置である。

(もっと読む)

A/Dコンバータの試験装置および試験方法

【課題】A/Dコンバータの試験時間の短縮にある。

【解決手段】Nビット(Nは自然数)のA/Dコンバータ1を試験する試験装置2が提供される。電圧生成部10は、A/Dコンバータ1に対して、2N階調のアナログ電圧VINを出力する。キャプチャユニット20は、各階調におけるA/Dコンバータ1の出力コードDOUTをキャプチャする。信号処理部30は、各階調においてキャプチャされた出力コードDOUTを対応する期待値コードEXPと比較し、比較結果に応じて各階調のアナログ電圧VINの値を補正し、電圧生成部10に補正後のアナログ電圧VINを出力させる。

(もっと読む)

アナログデジタル変換器

【課題】高速のAD変換器を提供する。

【解決手段】アナログ入力信号をデジタル出力信号に変換するAD変換器であって,アナログ入力信号と参照電圧とを比較して当該比較結果に応じたデジタル出力信号の各ビットを順次出力するN段の比較ユニットと,比較ユニットが出力するデジタル出力信号の各ビットに基づいて参照電圧に対応する参照電圧生成デジタル信号を順次生成する論理回路と,参照電圧生成デジタル信号に基づいて前記参照電圧を生成するDA変換器とを有する。そして,N段の比較ユニットは,それぞれ,前段からの状態制御信号の判定状態に応答してリセット状態から判定状態になる比較器と,比較器が判定状態で比較結果を出力したときに後段の比較ユニットへの状態制御信号を判定状態にする状態制御信号生成部とを有し,トリガクロックに応答して,N段の比較ユニットの比較器が上位のビットから下位のビットまで順次比較動作を行う。

(もっと読む)

高分解能デジタル・アナログ変換装置及び方法

【課題】安価でありながら、高分解能のアナログ信号を出力可能であるとともに、低精度変換処理と高精度変換処理との両変換処理が選択可能な高分解能デジタル・アナログ変換装置を実現する。

【解決手段】DAC306は上位ビット用のDACと下位ビット用のDACとを有し、予め定めたデジタルデータが供給され、このデジタルデータから得られるアナログデータの理論値と、実際のDAC306から出力されたアナログデータとが比較され、補正データが作成されてメモリ301に格納される。メモリ301に格納された補正データを用いてDAC306からの出力データが補正される。補正方法は、高精度であるがキャリブレーションに長時間必要な全ビット方式と、全ビット方式より精度は劣るが短時間でキャリブレーションが可能な直線近似方式とがあり、必要に応じていずれかの補正方式が選択可能である。

(もっと読む)

DA変換装置

【課題】複数のDA変換器のそれぞれの積分非直線性誤差の影響を抑えて高速動作できるとともに、SFDRを拡大させることができるDA変換装置を提供する。

【解決手段】デジタル信号源2で生成されたデジタルデータ及びクロック信号がDA変換装置1に入力される。DA変換装置1は、データ選択用スイッチ11と、複数のDA変換器としての第1のDA変換器12及び第2のDA変換器13と、切替手段としてのアナログ信号切替用スイッチ14と、分周器15とを有している。各DA変換器12,13の積分非直線性誤差特性の非線形歪特性は、互いに逆の特性である。第1,2のDA変換器12,13の積分非直線性誤差特性は、第1,2のDA変換器12,13の両方の積分非直線性誤差を平均すると、ゼロに近づくような特性である。

(もっと読む)

時間デジタル変換器

【課題】スタート信号とストップ信号の時間差を計測する、高分解能、省電力、省スペースの時間デジタルコンバータ(TDC:Time−to−Digital Converter)を実現することを目的とする。

【解決手段】本発明は、時間領域で二分探索を行うn個のモジュールM1ないしMnを直列に接続することにより、TDCを実現する。本発明では、スタート信号とストップ信号の立ち上がり時刻の時間差TDCoutを、M1ないしMnの出力(tdc1...tdcn)から直接得ることができる。

(もっと読む)

半導体装置

【課題】比較的高速処理の必要な入力信号の処理の遅延を従来よりも低減する。

【解決手段】半導体装置100において、変換部2は、第1のチャネルCH0〜CH2および第2のチャネルCH3〜CH5を有し、選択中のチャネルに入力された信号をA/D変換する。第1のチャネルに入力される信号は、第2のチャネルに入力される信号よりも高速の処理が必要とされる。変換部2は、中央処理装置1などからスキャン変換指令を受けた場合に、複数の入力チャネルCH0〜CH5を所定の選択順で順次選択して連続的にA/D変換を行なう。この場合、変換部2は、第1のチャネルCH0〜CH2に入力された信号のA/D変換が完了した後でありかつ全入力チャネルの入力信号のA/D変換が完了する前に、A/D変換の完了を周辺回路IP0に通知する。

(もっと読む)

フォールディング回路およびアナログ・ディジタル変換回路

【課題】光信号を復調する際に、サンプルレートと分解能との間のトレードオフの関係を緩和させ、高いサンプルレートと高い分解能とを両立させたアナログ・デジタル変換を実現する。

【解決手段】フォールディング回路100に、入力信号光を互いに等しい光強度を有するN個の信号光に分配する信号光分配部110と、入力参照光を互いに異なる光強度を有するN個の参照光に分配する参照光分配部120と、N個の信号光とN個の参照光との光強度から入力信号光の光強度を量子化したNビットの温度計コードを導出し、この温度計コードの論理を1ビットおきに反転させた反転温度計コードの各ビットの総和の出力を、入力信号光の光強度の変化に応じて折り返される折返し信号として出力する折返し信号出力部130とを備える。

(もっと読む)

D/A変換器

【課題】アナログ出力に変換すべき1ビットディジタルデータが切り替わるときの応答性を向上させ且つリップルの抑制を図る。

【解決手段】抵抗R11および容量C11から構成されるRCローパスフィルタF11を1段目とし、抵抗R11よりも抵抗値が十分大きい抵抗R21および容量C21から構成されるRCローパスフィルタF21を2段目とし、且つ抵抗R21の両端に短絡用のスイッチSW21を設ける。1ビットディジタルデータのDuty比が変化したとき、スイッチSW21を閉操作して抵抗R21、容量C21、C22からなる時定数τの小さなRCローパスフィルタを形成し、アナログ出力Voutが十分セトリングした状態であり且つ1ビットディジタルデータのハイレベル区間の中間時点でスイッチSW21を開操作し、2段のRCローパスフィルタを形成する。

(もっと読む)

逐次比較型A/D変換器、および、DC−DC変換器

【課題】入力信号の変換範囲をより適切に設定して、入力信号の変換回数を削減することが可能な逐次比較型A/D変換器を提供する。

【解決手段】逐次比較型A/D変換器のSAR制御回路は、比較結果信号に応じて、第1の変換範囲内でデジタル値を第1の変換回数だけ変化させて出力する。逐次比較型A/D変換器の範囲設定回路は、判定信号に応じて、サンプルホールド値が第1の変換範囲内にない場合は、前記第1の変換範囲と異なる第2の変換範囲を設定する。

(もっと読む)

半導体装置および固体撮像装置

【課題】画素情報の読出し速度を向上させることが可能な半導体装置および固体撮像装置を提供する。

【解決手段】カラムADCは、PGA22と、縦列接続された2つの巡回型ADCとを含む。PGA22は、画素の黒レベルおよび信号レベルの差分を増幅した信号にVrefを加算した電位をPGA画素情報として出力する。第1ADC24_1は、Vrefを参照電位としてサンプリングして保持するとともに、PGA画素情報を信号電位としてサンプリングして保持し、これらの差分信号であるi行の画素情報に応じてデジタル値の中の上位ビットを生成すると、(i+1)行の画素情報のサンプリングを開始する。第2ADC24_2は、第1ADC24_1が(i+1)行の画素情報をサンプリングして保持するのと並行して、第1ADC24_1によって生成された上位ビットに応じて該デジタル値の中の下位ビットを生成する。

(もっと読む)

アナログデジタル変換器

【課題】 逐次比較ADCにおいて、サンプリング容量の電圧依存性によりA/D変換結果に歪が生じるため、分解能が制限される。

【解決手段】 A/D変換器を、容量値の等しい容量(31、32)を逆向きに接続したサンプリング容量部(14)と、サンプリング電荷のA/D変換を行う逐次比較A/D変換部(15)と、逐次比較A/D変換部の内部DAC用容量の容量ばらつきを補正するデジタル補正部(16)と、サンプリング電荷の電圧依存性の3次以上の係数をデジタル補正するデジタル補正部(17)とを有する構成とする。

(もっと読む)

差動増幅回路および液晶表示装置

【課題】消費電流を増加させずにスルーレートを向上する差動増幅回路、表示用駆動回路を提供する。

【解決手段】差動増幅回路は、差動信号を入力する入力段と、入力段の出力に基づいて容量性負荷を駆動する出力段とを具備する。入力段は、差動信号を入力する差動信号入力部(MN1/MN2、MN11/MN12/MP21/MP22)と、差動入力部にバイアス電流を供給する電流源(MN3、MN10/MP20)と、電流源(MN3、MN10/MP20)に並列に挿入される可変容量(Cs)を含むスルーレート調整部(414、415)とを備える。

(もっと読む)

多チャネル量子化器および量子化の方法

【課題】多チャネル量子化器および量子化の方法を提供する。

【解決手段】1つの量子化器は、入力アナログ信号を受け取る複数のチャネル102と、各チャネル内の演算増幅器104と、演算増幅器に接続された比較器106とを有するアナログ−デジタル変換器(ADC)100を含む。ADCはさらに、比較器に接続され、比較器から受け取った比較器信号に基づいて出力を発生するように構成された、各チャネル内の論理回路108を含む。ADCはまた、複数のチャネルに接続され、時間的に変化する基準信号を供給するように構成されたランプ発生器116を含む。

(もっと読む)

信号処理装置、及び電源装置

【課題】本発明は、信号処理結果の精度を維持しつつ、信号処理の応答性を改善する。

【解決手段】信号処理装置100は、複数の入力信号に基づいて生成される情報を、複数の入力信号からなる組と入力信号の取得順序(0〜(N−1))とに対応させて記憶するデータレジスタ部30と、複数の入力信号に基づいた情報を生成するAD変換部20と、複数の入力信号からなる入力信号の組を示す識別情報(0〜(M−1))と、組を成す複数の入力信号の取得順序を示す順序情報(0〜(N−1))とに対応させて、入力信号に基づいて生成された情報をデータレジスタ部30に記憶させる制御部90と、複数の入力信号の組を成す入力信号に対応する記憶された情報に対するフィルタ処理を行うフィルタ処理部40とを備える。

(もっと読む)

A/D変換器

【課題】アナログ回路の特性ばらつきに影響されない高精度かつ高スループットのA/D変換器を実現する。

【解決手段】A/D変換器は、サンプリングクロック信号に同期して、入力されたアナログ電圧を二つの信号の時間差に変換する電圧時間変換器(1)と、二つの信号の時間差をデジタル値に変換する複数の時間デジタル変換器(2)とを備え、複数の時間デジタル変換器(2)がインタリーブ動作する。

(もっと読む)

A/D変換ステージおよびA/D変換ステージにおける変換誤差を示す信号を生成する方法

【課題】一サンプリング当たりにA/D変換時間を短縮すること可能なアナログディジタル変換器を提供することを目的とする。

【解決手段】A/D変換ステージ101でのサンプル値Rに変換操作Bを施して変換結果D3を生成しこの変換結果D3にA/D変換ステージ103でサンプリング操作Aを施す。A/D変換ステージ105でのサンプル値に変換操作Bを施して変換結果D4を生成しこの変換結果D4にA/D変換ステージ107でサンプリング操作Aを施す。A/D変換ステージ107でのサンプル値に変換操作Bを施して変換結果D5を生成しこの変換結果D5にA/D変換ステージ101でサンプリング操作Aを施す。A/D変換ステージ103でのサンプル値に変換操作Bを施して変換結果D6を生成しこの変換結果D6にA/D変換ステージ105でサンプリング操作Aを施す。

(もっと読む)

アナログ信号に対応したディジタル信号を生成する方法

【課題】一サンプリング当たりにA/D変換時間を短縮すること可能なアナログディジタル変換器を提供することを目的とする。

【解決手段】A/D変換ステージ101でのサンプル値Rに変換操作Bを施して変換結果D3を生成しこの変換結果D3にA/D変換ステージ103でサンプリング操作Aを施す。A/D変換ステージ105でのサンプル値に変換操作Bを施して変換結果D4を生成しこの変換結果D4にA/D変換ステージ107でサンプリング操作Aを施す。A/D変換ステージ107でのサンプル値に変換操作Bを施して変換結果D5を生成しこの変換結果D5にA/D変換ステージ101でサンプリング操作Aを施す。A/D変換ステージ103でのサンプル値に変換操作Bを施して変換結果D6を生成しこの変換結果D6にA/D変換ステージ105でサンプリング操作Aを施す。

(もっと読む)

アナログディジタル変換器およびアナログ信号に対応したディジタル信号を生成する方法

【課題】一サンプリング当たりにA/D変換時間を短縮すること可能なアナログディジタル変換器を提供することを目的とする。

【解決手段】A/D変換ステージ101でのサンプル値Rに変換操作Bを施して変換結果D3を生成しこの変換結果D3にA/D変換ステージ103でサンプリング操作Aを施す。A/D変換ステージ105でのサンプル値に変換操作Bを施して変換結果D4を生成しこの変換結果D4にA/D変換ステージ107でサンプリング操作Aを施す。A/D変換ステージ107でのサンプル値に変換操作Bを施して変換結果D5を生成しこの変換結果D5にA/D変換ステージ101でサンプリング操作Aを施す。A/D変換ステージ103でのサンプル値に変換操作Bを施して変換結果D6を生成しこの変換結果D6にA/D変換ステージ105でサンプリング操作Aを施す。

(もっと読む)

21 - 40 / 265

[ Back to top ]