Fターム[5J043BB04]の内容

Fターム[5J043BB04]に分類される特許

1 - 20 / 38

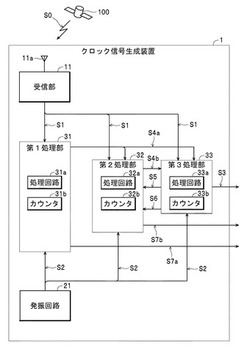

クロック信号生成装置およびクロック信号生成方法

【課題】クロック信号の精度を向上させる。

【解決手段】パルス信号S2を決められた数だけカウントする毎にクロック信号S3を生成する際に、2回の1秒信号S1の出力時点間におけるパルス信号S2の第1カウント数とパルス信号S2の周波数との差分値である第1の誤差を決められた数から増減する補正処理を実行する処理部31〜33を備え、処理部は、1秒信号S1の出力時点から1秒間に生成すべき数のクロック信号S3を生成する毎に出力する1秒完了信号S6の出力時点までの間におけるパルス信号S2の第2カウント数が第1規定値以下のときに第2カウント数を第2の誤差として特定し、第2カウント数が第1規定値よりも大きくかつ周波数の値および第1の誤差を合計した値と第2カウント数との差分値の絶対値が第1規定値以下のときにその差分値を第3の誤差として特定し、補正処理において第1〜第3の誤差の合計値を決められた数から増減する。

(もっと読む)

半導体装置

【課題】広範囲、光分解能に周波数を可変することのできるクロック信号を生成する。

【解決手段】オペアンプAMP1は、正入力部と負入力部が等しい電圧となるようフィードバックがかかり、回路ノードfbckは、参照電圧VREFIに等しい電圧となる。デコーダDECは、制御信号CNT7,CNT6をデコードし、トランジスタT2〜T5のいずれか1つをオンさせる。この構成によって、回路ノードfbckが、参照電圧VREFIと同電位となるようフィードバック制御がかかるため、トランジスタT2〜T5のON抵抗を大幅に低減することができ、周波数精度の悪化を防止することができる。

(もっと読む)

半導体集積回路

【課題】複数の無線通信チャンネルについて、PLL回路全体の動作特性に基づいて電圧制御発振器の精密なキャリブレーションを行う。

【解決手段】半導体集積回路は、高周波信号を生成する電圧制御発振器を含むPLL回路と、電圧制御発振器のトランジスタに選択的に負荷される複数のキャパシタと、複数の無線通信チャンネルについて電圧制御発振器の発振周波数を補正するためのキャパシタに関する情報を格納する格納部と、キャリブレーションモードにおいて、複数の無線通信チャンネルについてPLL回路のループ特性を測定することにより補正用キャパシタに関する情報を格納部に格納し、通常動作モードにおいて、選択された無線通信チャンネルに従って、格納部に格納されている情報を読み出すことにより補正用キャパシタを決定するキャリブレーション回路とを具備する。

(もっと読む)

パルス生成回路およびパルス生成方法

【課題】電源電圧の変動しやすい容量の小さい電源である環境下でも、安定したパルス信号を生成できるようにする。

【解決手段】タイミング制御回路1−1,1−2と論理回路2−1とを設ける。タイミング制御回路1−1,1−2は、放電制御端子S11,S21と充電制御端子S12,S22,と信号出力端子T1,T2を有し、内部に時定数素子を備えている。先ず、充電制御端子S12,S22へ充電の開始を指示し、端子T1,T2から出力される電圧VT1,VT2を「H」レベルとする。次に、放電制御端子S11へ放電の開始を指示し、遅延時間τ1経過後に電圧VT1を「L」レベルとし、タイミング制御回路1−2での放電を開始させ、遅延時間τ2経過後に電圧VT2を「L」レベルとする。このタイミング制御回路1−1,1−2からの電圧VT1,VT2を論理回路2−1へ与え、論理回路2−1よりタイミング制御回路1−2での遅延時間τ2をパルス幅とするパルス信号PS1を得る。

(もっと読む)

半導体集積回路装置

【課題】プロセスモニタに必要な回路面積を増加させることなく、高精度なプロセスキャリブレーションを短時間で行う。

【解決手段】ディジタル制御発振器38が任意の発振バンドを選択した後、制御部25はTDC41の信号がプロセスモニタ制御部40に入力されるようにスイッチ44を切り換える。TDC41は、信号VREFの立ち上がりエッジと最も近い信号VPREの立ち上がりエッジの期間をディジタル値に、信号VREFの立ち上がりエッジと2番目に近い信号VPREの立ち上がりエッジの期間をディジタル値に変換し、その差を算出する。プロセスモニタ制御部40は、ルックアップテーブルを参照し、算出した値と予め設定されている期待値とを比較し、プロセス値を決定する。そのプロセス値は、プロセス信号として調整制御部26にそれぞれ出力され、プロセスキャリブレーションが行われる。

(もっと読む)

予め定められたデューティサイクル信号発生器

予め定められたデューティサイクルを有する信号を発生させる技術である。例示的な実施形態では、第1のカウンタは、発振器信号のサイクルの第1の数をカウントするように構成されており、第2のカウンタは、発振器信号のサイクルの第2の数をカウントするように構成されており、第2の数は第1の数よりも大きい。第2のカウンタの出力は、第1および第2のカウンタをリセットするために使用されるが、第1および第2のカウンタの出力は、さらに、予め定められたデューティサイクルを有する信号を発生させるトグルラッチを駆動する。さらなる態様は、第2の数に対する奇数値と偶数値とを対応する技術を含む。 (もっと読む)

電圧−周波数変換回路およびそれを備えた血圧測定装置

【課題】簡易な方式により精度の高い電圧−周波数変換回路を提供する。

【解決手段】抵抗素子16は、入力端子とノードN0との間に設けられる。スイッチ素子15は、ノードN0と接地電圧GNDとの間に設けられ、ノードNCの電圧レベルに応じて導通する。抵抗素子13は、ノードN0とノードNAとの間に設けられる。抵抗素子12は、ノードNAとNOR回路11Aの入力ノードの一方側との間に設けられる。コンデンサ14は、ノードNAとノードNCとの間に接続される。NOR回路11Aの入力ノードは、抵抗素子12を介してノードNAと、接地電圧GNDと接続される。NOR回路11Bの入力ノードは、NOR回路11Aの出力ノードと、接地電圧GNDと接続される。NOR回路11Cの入力ノードは、ノードNCと、接地電圧GNDと接続される。

(もっと読む)

パルス発生装置

【課題】良好な信号レベルのパルス信号を効率よく発生するのに好適なパルス発生装置を提供する。

【解決手段】パルス発生装置100を、起動開始信号D0の入力に応じて単位パルス信号を発生する、各々の信号出力部が独立した単位パルス発生回路20_1〜20_Nと、単位パルス発生回路20_1〜20_Nのうち単位パルス信号を出力する予定の一部の回路の信号出力端子を順次選択して、該選択した信号出力端子を共通の信号出力線Pu_Coutに電気的に接続し、残りの単位パルス発生回路の信号出力端子を共通の信号出力線Pu_Coutから電気的に切断するスイッチ制御回路30及び選択スイッチ40とを含む構成とした。

(もっと読む)

クロック発生装置およびクロック発生装置におけるジッタ低減方法

【課題】よりジッタの少ないクロック信号を発生させること。

【解決手段】周期信号を発生するDDS回路と、入力信号と基準信号とを比較して2値化信号を出力するコンパレータと、を有し、前記DDS回路において発生される前記周期信号に対し、前記基準信号との交差点における変化率を増加させる補正を行う変化率補正手段を備えることを特徴としている。

(もっと読む)

波形生成回路

【課題】セット信号、リセット信号の立ち上がり間と同様のパルス幅が出力できる波形生成回路を実現することを目的にする。

【解決手段】本発明は、セット信号、リセット信号により波形を生成する波形生成回路に改良を加えたものである。本回路は、セット信号、リセット信号が入力される第1のSRフリップフリップと、この第1のSRフリップフロップのコンプリメンタリ出力を入力し、コンプリメンタリ出力の一方を非反転で出力し、他方を反転させて出力する反転部と、セット信号、リセット信号に基づいたセレクト信号により、反転部の非反転出力、反転出力を選択して、出力する選択部とを備えたことを特徴とするものである。

(もっと読む)

クロック信号生成装置

【課題】本発明は、温度特性、電源電圧特性、個体バラツキを吸収し、最適なノンオーバーラップ時間を有する2相クロック信号を確実に生成できる信頼性の高いクロック信号生成装置を提供することを目的とする。

【解決手段】本発明のクロック信号生成装置は、ノンオーバーラップクロック信号を使用する負荷回路において使用される2相クロック信号の遅延時間を可変する可変遅延器と、2相クロック信号におけるHレベル区間のノンオーバーラップ時間を検出し、ノンオーバーラップ時間に応じた検出信号を出力するノンオーバーラップ検出器と、ノンオーバーラップ検出器からの検出信号に基づいて可変遅延器を制御する制御信号を生成する制御信号生成部と、を備えている。

(もっと読む)

パルス発生回路及び通信装置

【課題】簡単な回路でかつ低消費電力で帯域制限された正確な短パルスの発生回路を具現し、フィルタを使用せずに目的のパルスを得る。

【解決手段】起動信号に基づき所定形状のパルスを出力端子から出力するパルス発生回路において、起動信号の位相が変化した時点から所定量の時間差で位相が順次変化するn+1個の信号(nは2以上の整数)を発生するタイミング発生回路と、所定の電位を供給する第1の電源及び第2の電源と、n個のインピーダンス素子と、n+1個の信号に基づく論理関数値によって所定順序で出力端子と第1の電源または第2の電源とをインピーダンス素子を介して交互に切り替えて接続するスイッチ回路と、を含むパルス発生回路。

(もっと読む)

1/4周期遅延クロック発生器

【課題】リセット信号を別途に不要とし、特定の初期値がなくても正常に動作できる1/4周期遅延クロック発生器を提供する。

【解決手段】本発明の1/4周期遅延クロック発生器は、基準クロック信号を発生させる基準クロック発生部と、前記基準クロック信号の立ち上がりエッジで第1入力信号をキャッチして前記基準クロック信号の次の立ち上がりエッジまで第1出力信号として前記第1入力信号を出力し、反転された前記第1出力信号の入力を前記第1入力信号として受ける第1回路部と、第2入力信号をキャッチして第2出力信号として出力し、前記第2入力信号として前記第1回路部から前記第1出力信号の入力を受ける第2回路部とを備える。

(もっと読む)

クロック生成回路

【課題】電源電圧の変動等による出力クロックへの影響を低減する。

【解決手段】基準クロックを生成する自走発振器10と、この基準クロックに同期してカウントするカウンタを有し、外部より入力される入力クロックの周期毎のカウンタのカウント値を保持して並列出力するクロックカウンタ40と、クロックカウンタ40の出力値に応じたクロック周波数のシリアル信号を基準クロックに同期させて出力するクロック分周器70を備え、クロックカウンタ40とクロック分周器70との間に、クロックカウンタ40の出力値の瞬時的な変動を抑制するフィルタ60を備える。

(もっと読む)

パルス発生回路およびUWB通信装置

【課題】立ち上がり、立ち下りのエッジで起動されたパルス間で振幅が異なり、正負の対称性がずれる。

【解決手段】起動信号を所定量の遅延を伴って論理反転する縦続接続された複数のインバータからなるインバータ遅延回路と、出力端子を、インバータ遅延回路の出力Di,XDi−1の論理積が真のとき第一の電位に接続し、出力Di,XDi+1の論理和が偽のとき第二の電位に接続する第一のスイッチ回路と、出力端子を、出力Di,XDi+1の論理積が真のとき第一の電位に接続し、出力XDi+1,Di+2の論理和が偽のとき第二の電位に接続する第二のスイッチ回路と、第一のスイッチ回路が活性化されるとき起動信号をインバータ遅延回路の1段あたりの遅延量と同一の時間遅延させ、第二のスイッチ回路が活性化されるとき遅延させないで起動信号をインバータ遅延回路に入力する起動信号制御回路とを備える。

(もっと読む)

パルス発生回路およびUWB通信装置

【課題】素子性能限界に近い超広帯域超高周波でスカート特性の良いバンドパスフィルタが必要であった。

【解決手段】起動信号に呼応して所定形状のパルスを出力端子に出力するパルス発生回路において、該起動信号から該起動信号と所定量の時間差を伴った複数の信号{Di}を発生する回路と、所定の電気量の電気エネルギーを供給する複数の電源{Ej}と前記信号{Di}の少なくとも一部の信号の論理関数値によって所定順序で前記出力端子に前記電源{Ej}を順次切り替えて接続するスイッチ回路と、を含んでパルス発生回路を構成する。

(もっと読む)

テンプレートパルス発生回路、通信装置、および通信方法

【課題】パルス通信における省電力化に適したテンプレートパルス発生回路、通信装置、および、この通信方法を提供する。

【解決手段】システムコントローラ830からの制御信号CTLによって、受信パルスの検波に際して同期捕捉(823)を行う同期捕捉モード時にはテンプレートパルス発生回路820がテンプレートパルスを連続的に出力し、同期捕捉が略確立して以降の同期追従モード時にはテンプレートパルスを断続的に出力するようにテンプレートパルスの発生態様を切換えて、パルス通信の開始当初に連続的なテンプレートパルスを利用して短時間で同期捕捉を確立させ、これ以降はテンプレートパルスを断続的に出力するようにして省電力化を図る。

(もっと読む)

同期回路

【課題】広い範囲で遅延調整を可能にしてACタイミングを確保し易くする。

【解決手段】フリップフロップ回路FF1と組合せ論理回路LOGIC1との間にフリップフロップ回路FF1aを挿入し、セレクタMUX1によりいずれか一方のフリップフロップ回路の出力データ信号を選択可能にする。フリップフロップ回路FF1に入力するクロック信号をフリップフロップ回路FF1aに入力するクロック信号よりも遅らせる。

(もっと読む)

パルス発生回路およびこの回路を用いた電子装置、携帯電話機、パーソナルコンピュータ、ならびに、この回路を用いる情報伝送方法

【課題】パルスの休止期間における貫通連流の値をも極小にして極限まで低消費電力化を

図ったパルス発生回路を提供する。

【解決手段】パルス発生回路を、所定段数縦続接続されたインバータ回路101〜109

と、これらインバータ回路101〜109の各段の手段によって論理反転動作を行う論理

回路110〜125を備え、論理回路110〜125の出力に応じて出力端を第1の電位

レベルV1か又は第2の電位レベルV2かに選択的に接続して出力端131に出力パルス

Poutを得るようにし、該出力パルスPoutの中間の基準レベルとしてV1〜V2を分圧回

路11によって分圧した第3のレベルV3に設定するが、パルスの休止期間では、オンオ

フ制御信号生成回路1500の制御下で開閉手段150をオフにして分圧回路11への給

電を断ち貫通電流が流れないようにする。

(もっと読む)

クロック信号発生装置

【課題】クロック信号伝送において信号波形歪みや信号遅延による位相ひずみの生じにくいクロック信号を発生するクロック信号発生装置を提供する。

【解決手段】本発明のクロック信号発生装置は、単一の周波数成分からなる第1クロック信号を出力する信号発生部と、上記第1クロック信号の振幅値内に設定された複数の閾値と上記第1クロック信号の瞬時値とをウインドコンパレータによって比較して第1クロック信号の位相を判別し、この位相角度に対応して信号の立ち上がり又は立ち下がりを決定して第2クロック信号を形成する位相角度検出部と、を備える。

(もっと読む)

1 - 20 / 38

[ Back to top ]