Fターム[5J055EY01]の内容

Fターム[5J055EY01]の下位に属するFターム

Fターム[5J055EY01]に分類される特許

201 - 220 / 1,471

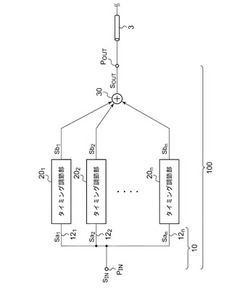

ドライバ回路およびそれを用いた試験装置

【課題】ポジティブエッジの波形、ネガティブエッジの波形の少なくとも一方を調節可能なドライバ回路を提供する。

【解決手段】分岐回路10は、送信すべき入力信号SINを複数の経路12に分岐する。各タイミング調節回路20は、それぞれが対応する経路に分岐された送信すべき信号Saのポジティブエッジおよびネガティブエッジの少なくとも一方に遅延を与える。合成出力回路30は、複数のタイミング調節回路20の出力信号Sbを合成し、合成された信号SOUTを伝送線路3に出力する。

(もっと読む)

内燃機関制御装置

【課題】電磁負荷を駆動する内燃機関制御装置において、電磁負荷の駆動周期が短い場合でも、該電磁負荷の故障診断精度を向上させ、ノイズに影響されない高速制御を安定して行う。

【解決手段】電磁負荷制御装置において、前記電圧異常を検出する手段をマスクするためのマスク手段を備え、前記マスク手段は、前記電圧異常の検出タイミングを、電磁負荷遮断と電磁負荷の通電とが繰り返される電磁負荷の通電開始タイミングに合わせて設定してあり、電磁負荷の通電遮断時より一定時間を内部タイマによってカウントすることにより、前記一定時間内に検出された電圧異常の誤検出をマスクするように構成する。

(もっと読む)

負荷駆動装置

【課題】パワー素子にクランプ回路を接続してパワー素子の駆動端子に印加される電圧を所定電圧にクランプするに際し、スイッチング素子を駆動するための定電流の消費電流を削減できる負荷駆動装置を提供する。

【解決手段】クランプ回路50は駆動端子41に接続されており、ドライバ回路30が駆動端子41に定電流を流すことにより駆動端子41に印加される電圧が所定電圧に達すると、駆動端子41に印加される電圧を所定電圧にクランプする。また、ドライバ回路30は、パワー素子40の駆動端子41に定電流を流すことでパワー素子40をオン駆動する。さらに、ドライバ回路30は、駆動端子41に印加される電圧が所定電圧に達した後、駆動端子41に流す定電流の電流量を、駆動端子41に印加される電圧が所定電圧に達するまでに駆動端子41に流す定電流の電流量よりも低減する可変定電流回路32を備えている。

(もっと読む)

スイッチ装置および試験装置

【課題】入力電圧範囲の大きな半導体スイッチ装置を提供する。

【解決手段】外部から入力される制御電圧に応じて第1端子および第2端子間を電気的に接続または切断するスイッチ装置であって、第1端子および第2端子の間にソースおよびドレインが接続され、当該スイッチ装置に入力される入力電圧とゲート電圧との差に応じてオンまたはオフとなるメインスイッチと、制御電圧および入力電圧に応じて第1基準電圧を電圧シフトさせた駆動電圧をメインスイッチのゲートに供給する制御部と、を備えるスイッチ装置を提供する。

(もっと読む)

高周波スイッチ

【課題】高周波信号の伝達経路における高調波特性を良好に維持しつつ、回路規模が縮小された高周波スイッチを提供する。

【解決手段】1つの送信ポート10と、1つの受信ポート20と、共通ポート30と、送信側シリーズスイッチ40と、送信側シャントスイッチ50と、受信側シリーズスイッチ60と、受信側シャントスイッチ70とを有する。送信ポートは、送信信号を入力し、受信ポートは、受信信号を出力し、共通ポートは、送信信号を送信するか、または受信信号を受信する。送信側シリーズスイッチは、送信ポートと共通ポートとの間に接続され、送信側シャントスイッチは、送信ポートとグランドとの間に接続され、受信側シリーズスイッチは、受信ポートと共通ポートとの間に接続され、夫々のスイッチはボディコンタクト型FETである。受信側シャントスイッチは、受信ポートとグランドとの間に接続され、フローティングボディ型FETである。

(もっと読む)

電子リレー

【課題】制御部及びゲート駆動部によって消費される電力を抑制しつつ、負荷の起動時に突入電流を流しきることが可能な電子リレーを提供する。

【解決手段】商用電源6と負荷7に直列接続され、トランジスタ構造を有するスイッチ素子を用いた開閉部11と、負荷の起動及び停止を制御する制御部12と、制御部12とは絶縁され、スイッチ素子のゲート電極にゲート駆動信号を出力するゲート駆動部13と、制御部12及びゲート駆動部13を動作させるための電力を確保する電源部14を備え、制御部12は、負荷7の起動時に、ゲート駆動部13に、所定時間だけスイッチ素子のゲート電極に対して、定常安定動作時よりも多くの駆動電力を供給させる。

(もっと読む)

負荷駆動装置

【課題】 負荷への通電を妨げることなく、昇圧した電圧が低下することを防止することができる負荷駆動装置を提供する。

【解決手段】 複数相の駆動回路のうちの少なくとも2相間において昇圧用コンデンサ47,67と第3の電源45,65との接続部に設けられ、昇圧された電圧が出力される昇圧電源端子10,13同士の電気的な接続または遮断を選択する少なくとも1つのスイッチ回路102と、少なくとも1つのスイッチ回路102を制御する少なくとも1つのスイッチ制御回路110とを備えている。

(もっと読む)

ゲート駆動回路及び半導体装置

【課題】応答性を損なうことなく能動クランプ素子の損失電力を低減できる能動クランプ回路を用いたゲート駆動回路及び半導体装置を提供する。

【解決手段】スイッチ素子Tr7のゲートを駆動するゲート駆動回路であって、制御信号に基づいてスイッチ素子Tr7を駆動する駆動部(トランジスタTr1,Tr2,Tr4,Tr5)と、スイッチ素子Tr7の第1主端子(ドレイン)と第2主端子(ソース)との間に印加される電圧が所定電圧以上の場合に、駆動部によるスイッチ素子Tr7に対する駆動動作を強制的に遮断して、スイッチ素子Tr7の第1主端子と第2主端子との間の電圧がクランプされるようにスイッチ素子Tr7を駆動するアクティブクランプ回路(ダイオードD1、ツェナーダイオードZD1、抵抗R1、トランジスタTr3,Tr6)とを備える。

(もっと読む)

半導体装置及び電子機器

【課題】トランジスタを用いたスイッチ回路を有するデジタル回路において、電源電圧、入力信号の振幅、トランジスタのしきい値電圧の関係に応じて適切に入力信号を補正し、好適な回路動作を可能とする。

【解決手段】電源電位(VDD、VSS)が供給される第1のトランジスタ(32、33)を有するスイッチ回路(31)と、入力信号が印加される入力端(IN)と第1のトランジスタの制御端子(ゲート)との間に接続された補正回路(34、36)とを有し、前記制御端子と入力端との間に接続された容量(C2、C3)と、該容量と前記制御端子との間のノード(N5、N6)と電源電位との間に設けられた、第1のトランジスタと概ね同じしきい値を有するダイオード接続された第2のトランジスタ(35、37)と、第2のトランジスタに直列に接続されたスイッチ(SW2、SW3)とを有するデジタル回路(30)を提供する。

(もっと読む)

半導体装置

【課題】ドライブ能力およびスルーレートを調節可能な出力ドライバを備え、従来よりも微細化することができる半導体装置を提供する。

【解決手段】半導体装置は、コア回路から転送されるデジタルデータを出力するために複数のサブドライバを含む出力ドライバODと、サブドライバを選択するセレクタとを備える。各サブドライバは、デジタルデータに従って出力データを立ち上げまたは立ち下げるために、第1の電源PS1と出力配線WOUTとの間に接続された出力トランジスタTP30と、出力トランジスタTP30のゲートと第2の電源VSSとの間に直列に接続されたスイッチングトランジスタTN33およびスルーレート調整トランジスタTN34とを備える。各スルーレート調整トランジスタTN34は、出力データの立ち上がりまたは立ち下がりのスルーレートを決定するために調整されたゲート電位をセレクタによって選択的に与えられる。

(もっと読む)

反転電圧出力回路

【課題】入力信号の変化に応じて直流電源の非接地電圧と接地電圧の間で反転する電圧を出力する回路であり、非接地端子に接続されている電源線に生じる電圧変動を抑制する。

【解決手段】電流制限素子14とスイッチング回路16が直列に接続されており、電流制限素子とスイッチング回路の中間点22の電圧を出力する。スイッチング回路の導通時にスイッチング回路を流れる電流が電流制限素子によって制限される。直流電源の非接地端子に接続されている電源線12に生じる電圧変動が抑制され、電源線12に接続されているアナログ回路等の動作が安定する。

(もっと読む)

半導体装置およびその検査方法

【課題】本発明の実施形態は、高周波スイッチ回路の高周波特性の良否を簡便に判定することができる半導体装置およびその検査方法を提供する。

【解決手段】実施形態に係る半導体装置は、複数の高周波端子と、共通高周波端子と、の間の信号経路を、前記高周波端子と前記共通高周波端子との間に直列に設けられた複数のFETにより切り替える高周波スイッチ回路を有する半導体装置であって、前記共通高周波端子に接続された複数のFETを含む半導体スイッチと、前記半導体スイッチを介して前記共通高周波端子に接続された発振回路と、前記発振回路の出力を入力とする検波回路と、前記検波回路の出力端子と、を備える。

(もっと読む)

通信ドライバ回路

【課題】外乱ノイズが侵入した場合でも、通信線の信号レベルの変動をより確実に防止できる通信ドライバ回路を提供する。

【解決手段】通信ドライバ部11は、信号バス17にノイズが印加されると、信号レベル変化阻止回路14が、出力段がオープンコレクタタイプで構成される反転増幅回路13の出力信号がローレベル側に変化することを阻止するように動作する。

(もっと読む)

駆動回路

【課題】電源部品を減らし、安価な構成の駆動回路。

【解決手段】一次巻線Npと第1の二次巻線S1と第1の二次巻線の極性とは逆極性を持つ第2の二次巻線を有する2以上の二次巻線とを有し一次巻線に駆動信号が印加されるトランスDT1、第1の二次巻線からの信号によりオンオフ制御される第1スイッチング素子Qh、第2の二次巻線からの信号によりオンオフ制御される第2スイッチング素子Ql、第1の二次巻線の一端と第1スイッチング素子の制御端子との間に接続され第1スイッチング素子を駆動する第1駆動部Q11,Q12、第2の二次巻線の一端と第2スイッチング素子の制御端子との間に接続され第2スイッチング素子を駆動する第2駆動部Q21,Q22、第1の二次巻線電圧を倍電圧整流平滑して第1駆動部に供給する倍電圧整流平滑回路D11,D12,C11,C12、第2の二次巻線電圧を倍電圧整流平滑して第2駆動部に供給する倍電圧整流平滑回路D21,D22,C21,C22を有する。

(もっと読む)

スイッチング駆動回路

【課題】オンオフ動作させる外部機器のEMIによる誤作動を確実に防ぐスイッチング駆動回路を提供する。

【解決手段】スイッチング駆動回路1は、LED4をオンオフ動作させるスイッチ素子であるpMOSトランジスタT1と、pMOSトランジスタT1のゲートソース間の抵抗10と、抵抗10に制御電流を供給するnpnトランジスタT4を含むカレントミラー回路と、抵抗10及びnpnトランジスタT4との間に設けられる遮断回路としてのnMOSトランジスタT5とを備える。制御信号がLED4を消灯制御するローレベルLのときにnMOSトランジスタT5を同時にオフすることで、EMIの影響により抵抗10から流れ込出す電流を遮断する。これにより、LED4の誤点灯を確実に防ぐ。

(もっと読む)

リセット回路

【課題】マイクロコンピュータとCPUを安全かつ確実にリセットして正常起動させる。

【解決手段】第1制御回路41は第2電圧が動作電圧に達したときにリセット信号が入力されていれば初期化後に起動し、レギュレータIC20は第1電圧をレギュレートして生成した第2電圧を第1制御回路41に供給し、第2制御回路42は第3電圧が動作電圧に達したときにリセット信号が入力されていれば初期化後に起動し、レギュレータIC30は、第3電圧をレギュレートして生成した第4電圧を第2制御回路42に供給する機器において、リセット回路100は、第1電圧が第5電圧を超えて150msが経過するまでリセット信号の出力を継続させ、第1電圧が第5電圧を超えてから150msが経過するとリセット信号の出力を停止する。(第1電圧≧第2電圧、第3電圧≧第4電圧、第1電圧>第3電圧、第5電圧>第2電圧)

(もっと読む)

負荷駆動装置

【課題】負荷を駆動するための定電流のばらつきを低減することができる負荷駆動装置を提供する。

【解決手段】シャント抵抗20の一端側をオペアンプ34の反転入力端子に接続し、シャント抵抗20の他端側を基準電源32を介してオペアンプ34の非反転入力端子に接続する。シャント抵抗20に流れる電流は、駆動回路30内の第1スイッチング素子35を介して負荷10であるIGBTのゲートに流れるようになっている。これにより、基準電源32の基準電圧の値をVrefとし、シャント抵抗20の抵抗値をRoutとし、負荷10に流れる定電流の値をIcとすると、Vref=Rout×Icとなるようにオペアンプ34が第1スイッチング素子35のゲートをフィードバック制御する。これにより、シャント抵抗20に流れる電流の大きさが一定に制御され、ひいては負荷10に流す定電流のばらつきが低減される。

(もっと読む)

負荷駆動装置の製造方法

【課題】負荷駆動装置において負荷を駆動するためのスルーレートが狙い値となるように負荷駆動装置を製造する。

【解決手段】まず、半導体基板に第1基準電源32、スイッチング素子34、電流生成部35、およびオペアンプ33を備えた駆動回路30を形成する。この場合、第1基準電源32の第1基準電圧を調整することにより、負荷10に流す定電流の大きさを調整する。続いて、電流生成部35で生成されるテール電流が大きくなるようにテール電流のトリミングを行うことでオペアンプ33のスルーレートを調整する。これにより、オペアンプ33がスイッチング素子34を駆動したときに負荷10に流れる定電流が一定値に達するまでの定電流の立ち上がりの傾きを狙い値に調整することができる。

(もっと読む)

高周波半導体スイッチ回路

【課題】同時に2組以上の経路切替用FET段を導通状態にすることが可能な高機能な高周波スイッチ回路を電源端子の追加無しで小型化かつ低消費電力で実現する。

【解決手段】ダイオードスイッチロジック回路100は、共通入出力端子101と個別入出力端子102〜104それぞれとの間の経路のうち少なくとも1つを導通させ且つ制御端子105〜107の各制御電圧を、経路切替用FET段108〜110それぞれのゲートに印加させるとともに、制御端子105〜107の各制御電圧の論理合成電圧を、シャント用FET段111〜113のゲートに印加させ、かつ、論理合成電圧は、1組のシャント用FET段に印加される制御電圧の否定と、残りの組のシャント用FET段それぞれに印加される制御電圧の論理和と、の論理積で生成されるように構成されている。

(もっと読む)

負荷駆動装置

【課題】素子破壊などを抑制できる信頼性を有し、かつ、IGBTなどのスイッチングデバイスへ供給する定電流の精度を確保できる負荷駆動装置を提供する。

【解決手段】第1抵抗3と第1PchMOSFET4のソースとの間とオペアンプ5の出力端子との間に電圧制限回路6を備える。この電圧制限回路6により第1PchMOSFET4のゲート−ソース間の電位差が過大とならないように、第1PchMOSFET4のゲート電圧を制御する。例えば、第1PchMOSFET4のゲート電圧をクランプ電圧にてクランプすることにより、第1PchMOSFET4のゲート−ソース間の電圧が予め設定しておいた電圧となるようにする。これにより、第1PchMOSFET4のゲート−ソース間の耐圧を超える電位差が発生することを防止することが可能となる。

(もっと読む)

201 - 220 / 1,471

[ Back to top ]