Fターム[5J055EY01]の内容

Fターム[5J055EY01]の下位に属するFターム

Fターム[5J055EY01]に分類される特許

161 - 180 / 1,471

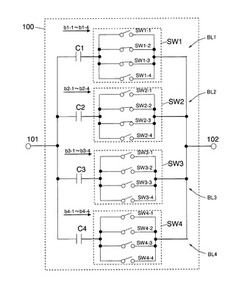

可変インピーダンス装置及び無線システム

【課題】 選択する容量の数に関わらずにそのオン抵抗を一定に保つことができる可変インピーダンス装置及びそれを用いた無線システムを提供する。

【解決手段】 一対の入出力端子101、102と、一対の入出力端子間に並列に接続された複数の回路ブロックBL1〜BL4と、を備え、回路ブロックは、一対の入出力端子の一方に一端が接続された容量性回路要素C1〜C4と、容量性回路要素の他端と一対の入出力端子の他方との間に互い並列に接続された回路ブロックの数以上の数のスイッチ素子SW1−1〜SW4−4を備えるスイッチ回路SW1〜SW4と、を備える。

(もっと読む)

ホールド回路

【課題】保持電圧の下降または上昇傾きを良好に調整可能なホールド回路を提供すること。

【解決手段】ホールド回路10は、入力端子20、第1出力端子22、基準電圧端子24、オペアンプ30、ダイオード32、コンデンサ36、抵抗R0、電圧発生回路50、を備えている。コンデンサ36は、一端が接続点26に接続され、他端が基準電圧端子24に接続される。抵抗R0は、一端が接続点26に接続される。ダイオード52のアノードが、オペアンプ38を介して接続点26に接続される。抵抗R0の他端と中間接続点58とが接続される。オペアンプ30は、非反転入力端子30bが入力端子20に接続され、反転入力端子30aが接続点26に接続され、出力端子30cがダイオード32に接続される。電圧発生回路50は、ダイオード52に入力される出力電圧V22から変化させたオフセット電圧V23を生成して、中間接続点58から出力する。

(もっと読む)

スイッチング回路

【課題】電力効率を低下させずに高速動作可能なスイッチング回路を提供する。

【解決手段】スイッチング回路は、入力電圧を第1の電圧に変換する第1のDC/DCコンバータB1と、制御信号に応じて第1の電圧を出力するか否か切り替える第1のスイッチ回路C1と、第1のスイッチ回路からの電圧の過渡特性を制御する第1の制御回路D1と、高圧側電源に一端が、出力端子に他端が接続され、第1の制御回路からの電圧に応じてオンオフされる第1の能動素子A1と、入力電圧を第2の電圧に変換する第2のDC/DCコンバータB2と、制御信号に応じて第1のスイッチ回路とは相補的に第2の電圧を出力するか否か切り替える第3のスイッチ回路C3と、第3のスイッチ回路からの電圧の過渡特性を制御する第2の制御回路D2と、出力端子に一端が、低圧側電源に他端が接続され、第2の制御回路からの電圧に応じてオンオフされる第2の能動素子A2とを備える。

(もっと読む)

電圧出力回路

【課題】プッシュ・プル接続された二つのスイッチ素子のON/OFFを切り換えること

によって生じる電力損失を抑制する。

【解決手段】プッシュ・プル接続された二つのスイッチ素子に対して並列に還流ダイオー

ドを設けておく。そして、何れのスイッチ素子もOFFの期間(デッドタイム期間)では

、ONにしようとする方のスイッチ素子に設けられた還流ダイオードに順方向電圧がかか

ったら、デッドタイム期間を終了して、一方のスイッチ素子をONにする。こうすれば、

二つのスイッチ素子の寄生容量での電荷の回生および充電が完了した後に、スイッチ素子

をONに切り換えることができるので、ONにしようするスイッチ素子の寄生容量に蓄え

られた電荷が、ONにしたスイッチ素子を流れて電力損失が発生することを回避すること

が可能となる。

(もっと読む)

出力回路、システム、及び出力回路の制御方法

【課題】信号波形の変異を抑制すること。

【解決手段】第1のトランジスタT1は、信号S3に応答してオンオフし、オンしたトランジスタT1は外部端子P2に接続された伝送路27をプルダウンする。伝送路27のレベルは、トランジスタT1のゲートと外部端子P2とをACカップリングするキャパシタC1により、キャパシタC1の容量値に応じた傾きで立ち下がる。プルダウン回路44は、外部端子P2の電位に応じて、トランジスタT1のゲート電圧をプルダウンする。

(もっと読む)

レベルシフト回路

【課題】消費電流の増加を抑制しつつ電源投入時にレベルシフタの状態を確定させる技術を提供する。

【解決手段】信号レベル変換部(11)と、安定化回路(12)とを具備するレベルシフト回路を構成する。安定化回路(12)は、第2電源電圧供給ノード(ND1)と接続ノード(ND2)との接続を制御する第1スイッチ(P3)と、接続ノード(ND2)電圧に応答して接地電圧供給ノード(GND)と出力ノード(ND3)との接続を制御する第2スイッチ(N3)とを備えることが好ましい。そして、第1スイッチ(P3)は、第2電源電圧(VDD)が、第1中間電圧を超えないときに、第2電源電圧供給ノード(ND1)と接続ノード(ND2)とを接続する。また、第2スイッチ(N3)は、第2電源電圧供給ノード(ND1)の電圧に応答して、出力ノード(ND3)と接地電圧供給ノード(GND)とを接続する。

(もっと読む)

スイッチング素子駆動回路

【課題】 電力伝送効率がよく、より小型のスイッチング素子駆動回路を提供する。

【解決手段】 実施形態に係るスイッチング素子駆動回路は、電力変換装置を構成するスイッチング素子と、前記スイッチング素子のオン/オフを切り替えるためのゲート信号を発生する制御演算手段と、前記ゲート信号を変調する為の所定周波数の交流信号を発生する発振手段と、前記発生されたゲート信号の立ち上がり及び立下りの各所定時間内において、前記交流信号の振幅を変化させ、前記ゲート信号を変調する変調手段と、前記変調手段にて変調されたゲート信号を復調し、前記スイッチング素子のゲートに供給する復調手段と、

前記制御演算手段と前記スイッチング素子間の絶縁を確保した上で、前記変調手段にて変調されたゲート信号を前記復調手段に伝送し、プリント基板上に実装されたトランスとを具備する。

(もっと読む)

電子装置

【課題】電流制御用トランジスタ、電流検出用抵抗及びオフ駆動用スイッチング素子の少なくともいずれかの異常を検出できる電子装置を提供する。

【解決手段】制御回路は、正常時のミラー期間Tmの終了時t4におけるIGBT110dのゲート電圧がミラー電圧Vmより高い場合、電流制御用FET121aのショート故障、又は、電流検出用抵抗121bのショート故障が発生していると判断する。具体的には、IGBT110dのゲート電圧の立ち上がり時t2を基準として、所定時間T1経過後のt4におけるIGBT110dのゲート電圧に基づいて異常を検出する。これにより、電流制御用FET121a又は電流検出用抵抗121bの異常を検出するころができる。

(もっと読む)

負荷駆動回路

【課題】複数の電源電圧条件に対して電流制限特性が追従し、負荷特性に適した電流制限を行なう負荷駆動回路を提供する。

【解決手段】図1に示す負荷駆動回路は、電源及び負荷に接続された出力MOSトランジスタと、出力MOSトランジスタの出力電圧に応じて、出力MOSトランジスタに流れる出力電流を複数段階の制限電流に制限すると共に、制限電流が切り替わる際の出力電圧を電源電圧の変化に基づいて切り替える電流制限値切り替え回路と、を備える。その結果、段階的に電流制限を行い、過剰な電流制限となることを妨げ、負荷条件の拡大を図る。さらに、電流制限値の切り替えを電源電圧に対応させて行なうため、当初の電源電圧条件とはことなる電源電圧で使用したとしても、電流制限特性が電源電圧の変動に追従し、全体として負荷特性に適した電流制限を行なうことができる。

(もっと読む)

半導体回路、半導体装置、及び電池監視システム

【課題】過大電流による素子の破壊を防止することができる、半導体回路、半導体装置、及び電池監視システムを提供する。

【解決手段】短絡保護回路30のPMOSトランジスタMP3により短絡状態の場合は、電源電圧VDDからFETゲート電圧出力端子FET_PAD(外部FET0)に電流が流れる経路をPMOSトランジスタMP0及び短絡電流検出用抵抗素子R0を経由する経路から、PMOSトランジスタMP1及び抵抗素子Rpuを経由する抵抗値が大きい経路に切り替えるため、短絡電流を制限することができ、従って、短絡により、電池監視IC14が破壊されるのを防止することができる。

(もっと読む)

複合半導体装置

【課題】電子回路の誤動作を防止でき、かつ、電力変換装置の小型化に寄与する複合半導体装置を提供する。

【解決手段】複合半導体装置10は、第1の端子G1から入力される信号に応じて第2の端子C1から第3の端子E1へ電流を流す第1のパワー半導体素子13と、第1の端子G2から入力される信号に応じて第2の端子C2から第3の端子E2へ電流を流す第2のパワー半導体素子16が同一基板(チップ)20内に形成された半導体装置であって、第2のパワー半導体素子16の第3の端子E2は、第1のパワー半導体素子13の第1の端子G1に電気的に接続されており、第1のパワー半導体素子13の第2の端子C1の電位が時間経過とともに増加したとき、第2のパワー半導体素子16の第3の端子E2を介して第1のパワー半導体素子13の第1の端子G1に電荷をチャージする電流路を備えた。

(もっと読む)

負荷駆動システム

【課題】制御回路ICと駆動回路ICとの間を接続する信号線に印加されるノイズの対策をより適切に行うことができる負荷駆動システムを提供する。

【解決手段】ECU11側に、複数の駆動回路に対してそれぞれ駆動制御信号を出力するタイミングに同期して、それぞれ異なるレベルの電圧を許可判別信号として出力する許可判別信号出力回路13を備える。また、EDU14側に、複数の駆動回路に対して、対応する駆動制御信号がアクティブになると共に、許可判別信号の電圧が対応する駆動回路について定められているレベルになると、駆動制御信号を対応する駆動回路に出力する駆動制御信号出力回路17を備える。

(もっと読む)

リーク補償された電子スイッチ

【課題】電子スイッチの開放されたスイッチを通したリーク電流は、信号クロストークを引き起こす。

【解決手段】スイッチング用の電子回路は少なくとも4個の電子スイッチ200のセット100を備える。第1サブセット110の少なくとも2個の電子スイッチ210,230は直列接続され、第2サブセット120の少なくとも2個の電子スイッチ220,240は直列接続される。前記第1サブセット110の第1電子スイッチ210に接続される第1バッファ310、及び前記第2サブセット120の第2電子スイッチ220に接続される第2バッファ320を備え、前記第1バッファ310は開状態における前記第1電子スイッチ210を通した電圧降下を最小化し、前記第2バッファ320は開状態における前記第2電子スイッチ220を通した電圧降下を最小化する。また2個のサブセット110,120の間に配され、グランドに接続されたスイッチ410を備える。

(もっと読む)

過電流保護装置

【課題】IGBT素子の短絡耐量を向上させ得る過電流保護装置を提供する。

【解決手段】過電流保護装置20では、各IGBT11a〜11fにゲート電圧Vgを印可するゲート駆動回路15に対してオフ信号を出力することで当該ゲート電圧Vgの印可を停止可能な保護回路22と、直流電源Eの電源電圧を制御可能な電源電圧制限回路23と、電源電圧を平滑化する平滑コンデンサCに蓄積された電荷を放電可能な放電回路24と、が設けられている。そして、電流検出部21により過電流が検出されると、保護回路22によりゲート電圧Vgの印可が停止され、電源電圧制限回路23により電源電圧が低減され、放電回路24により平滑コンデンサCに蓄積された電荷が放電される。

(もっと読む)

ドライバ回路

【課題】回路構成素子数の少ないドライバ回路を提供する。

【解決手段】L1とL2は伝送線路、TRはトランス、TR1とTR2は該トランスの一次側端子、TPは上記トランスの一次側中点タップ、S1とS2は送信回路である。また、Roは伝送線路の終端抵抗である。各々の送信回路は、NPNトランジスタQ1またはQ2、第一の抵抗R1またはR4、第二の抵抗R2またはR5、第三の抵抗R3またはR6からなる。また、T1とT2は、それぞれ、第一と第二の制御入力端子である。さらに、VCCは正電圧源である。そして、上記トランスの一次側中点タップTPは、上記正電源VCCに接続される。

(もっと読む)

出力回路

【課題】回路規模が小さく、出力トランジスタのしきい値電圧がばらついてもノイズを抑えつつターンオフ時間を短縮する。

【解決手段】駆動信号SdがLの時、トランジスタT1がオン、T2がオフしてVGS(T3)がほぼ電源電圧Vccに等しくなりトランジスタT3がオンする。駆動信号SdがHになるとトランジスタT1がオフ、T2がオンする。トランジスタT4がオンするので抵抗R2がバイパスされ、トランジスタT3のゲート電荷はトランジスタT4、T2を通して急速に放電する。VGS(T3)がVth(T4)+VDS(T2)よりも低下すると、トランジスタT4はオフとなり、以後はトランジスタT3のゲート電荷が抵抗R2とトランジスタT2を通して緩やかに放電する。トランジスタT3、T4のしきい値電圧は一致する傾向があるので、VGS(T3)がVTH(T3)に低下した時点でトランジスタT4をオフできる。

(もっと読む)

電子装置

【課題】オン駆動用定電流回路が故障しても、スイッチング素子の破損を抑えて駆動することができる電子装置を提供することを目的とする。

【解決手段】制御回路128は、オン駆動用定電流回路121が故障して、IGBT110dのゲートに正常時に流れ込む電流より大きい電流が流れ込むようになったとき、オフ駆動用定電流回路122の電流を調整する。これにより、IGBT110dのゲートに流れ込む電流、及び、ゲートから引き抜く電流を調整することができる。そのため、オン駆動用定電流回路121が故障しても、IGBT110dの破損を抑えて駆動することができる。

(もっと読む)

電子装置

【課題】スイッチング素子をオンするために、スイッチング素子の制御端子に定電流を供給して電荷を充電するオン駆動用定電流回路の異常を検出できる電子装置を提供する。

【解決手段】制御装置12は、オン駆動用定電流回路121と、オフ駆動用回路122と、制御回路128とを備えている。オン駆動用定電流回路121は、電流制御用FET121aと、電流検出用抵抗121bとを有している。制御回路128は、電流検出用抵抗121bの電圧に基づいて電流制御用FET121aを制御し、IGBT110dのゲートに定電流を流し込み、IGBT110dをオンする。オン駆動用定電流回路121の電流制御用FET121aや電流検出用抵抗121bが故障すると、それらに流れる電流や、それらに印加される電圧が変化する。そのため、電流検出用抵抗121bの電圧に基づいてオン駆動用定電流回路121の異常を検出することができる。

(もっと読む)

電圧駆動型スイッチングデバイスの駆動回路

【課題】ターンオン時のゲート電流を所望の電流値に高精度に設定でき、スイッチング損失の低減が可能な電圧駆動型スイッチングデバイスの駆動回路を得る。

【解決手段】IGBT1のゲート端子に接続され、駆動用パルス信号2のオン/オフゲート制御信号に基づき、IGBT1をターンオン/ターンオフさせるゲート信号を前記ゲート端子に出力するゲート駆動定電流回路が示されている。このゲート駆動定電流回路は、正電源3とGND電位4間に直列に接続された第1の抵抗5と第1のトランジスタ15と第2の抵抗6と制御信号伝達トランジスタ7、および正電源3とIGBT1のゲート端子間に直列に接続されたゲートオン抵抗8と定電流出力トランジスタ9を備え、第1のトランジスタ15のベース端子は第1のトランジスタ15のコレクタ端子と短絡接続されている。

(もっと読む)

インジケータ駆動回路

【課題】電源電圧の変動によるインジケータの光源のちらつきを抑制するインジケータ駆動回路を提供する。

【解決手段】インジケータ駆動回路1は、2つのnpnトランジスタQ2,Q6からなるカレントミラー回路200と、カレントミラー回路200の制御側のトランジスタQ2に制御電流を供給する電流源であるpMOSトランジスタQ3,Q4と、被制御側のpMOSトランジスタQ6に流れる電流により駆動され、インジケータのLED30をオンオフさせるpMOSトランジスタQ5を備える。電流源100からカレントミラー回路200へ流す制御電流は、外部からの制御信号によりnMOSトランジスタQ1を介して切り換えられる。電流源100を構成する2つのトランジスタQ3,Q4をカスコード接続で構成することで、カレントミラー回路200に流れる電流に対する電源VCCの変動の影響を小さくする。

(もっと読む)

161 - 180 / 1,471

[ Back to top ]