Fターム[5J055EY01]の内容

Fターム[5J055EY01]の下位に属するFターム

Fターム[5J055EY01]に分類される特許

141 - 160 / 1,471

ゲートドライブ回路

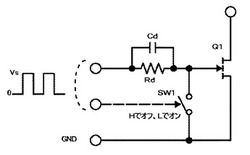

【課題】簡単な構成で、ワイドバンドギャップ半導体からなるスイッチ素子を駆動するゲートドライブ回路。

【解決手段】ワイドバンドギャップ半導体からなるスイッチ素子Q1であって、ドレインとソースとゲートとを有し、ゲートをドライブする信号とゲートとの間にコンデンサと抵抗の並列接続回路を介して接続され、オフ信号期間は、スイッチ素子Q1のゲート・ソース間を短絡するスイッチSW1とを備えることを特徴とするゲートドライブ回路。

(もっと読む)

パワー半導体スイッチの制御回路及びその制御方法

【課題】寄生容量の影響を最少化させることのできる、パワー半導体スイッチの改良された制御方法及び制御装置を提供する。

【解決手段】パワー半導体スイッチの制御接続端信号を生成するための信号処理ユニットを備えた、パワー半導体スイッチを制御する制御回路において、少なくとも一つの半導体素子が、定められたパワー半導体スイッチのコレクタ・エミッタ電圧を越えた時に、導通作動され、半導体素子の出力端が導電性の接続線を通じて抵抗直列回路の抵抗の間の接続点と、或いは信号処理ユニットと接続されている抵抗直列回路の出力端と接続されており、半導体素子のブレークダウン電圧が、半導体素子の出力端の電位が、パワー半導体スイッチがスイッチオン状態にある時のパワー半導体スイッチの制御接続端の電位よりも高くなるように選ばれている。

(もっと読む)

ESD保護回路

【課題】ESDパルスをもれなく検出し、かつ通常の電源投入時やスパイクノイズ印加時の誤検出を抑制する。

【解決手段】第1検出回路7はESDパルスの印加開始時から第1所定時間だけ第1検出信号を出力する。第2検出回路9は、第1検出信号を受け、かつESDパルスの印加が第2所定時間だけ持続したときに第3所定時間だけ第2検出信号を出力する。第1所定時間は電源の立ち上がり時間よりも短い。第2所定時間は第1所定時間よりも短く、かつスパイクノイズの印加時間よりも長い。第3所定時間はESDパルスの印加時間よりも長い。クランプ回路11は、第1検出信号及び第2検出信号の少なくとも一方が出力されているときはゲート端子47をGND端子3とは絶縁する。プルアップ回路13は、ゲート端子47を、第2検出信号が出力されているときは電源端子1に接続し、第2検出信号を出力されていないときは電源端子1とは絶縁する。

(もっと読む)

電子デバイス、およびオーディオデバイスを制御する複数の受動スイッチを有するオーディオアクセサリ

【課題】電子デバイスと、オーディオデバイスを制御するための複数の受動Spスイッチを有するオーディオアクセサリとを提供すること。

【解決手段】電子デバイスを制御するように適合されているシステムであって、システムは、電子デバイスに結合されているオーディオアクセサリを含み、オーディオアクセサリは、複数の抵抗型スイッチを有し、電子デバイスは、バイアス抵抗器とグラウンド接続とを介して抵抗型スイッチに電力を提供するように適合されているバイアス電圧供給源と、測定モジュールとを含み、測定モジュールは、バイアス電圧供給源と抵抗型スイッチとの間の接続上のバイアスポイントを監視することと、オーディオ出力によって引き起こされるグラウンドオフセット電圧を決定することと、グラウンドオフセット電圧を補償することと、スイッチのどれが係合しているかを決定することとを行うように適合されている。

(もっと読む)

スイッチング回路およびスイッチング回路を用いた撮像装置

【課題】EM−CCDのCMG駆動回路からEM−CCDの出力信号への飛び込みを低減しながら、負荷容量CMG電圧の振幅の減衰を防ぎ、矩形波特性を改善する。

【解決手段】論理バッファとPchMOSとNchMOSのゲート間にフェライトビーズとダイオードの並列接続を挿入し、MOSがターンオフする方向にダイオードが接続されているスイッチング回路において、PchMOSのドレインソース間導通抵抗が2オーム以上あり、PchMOSのドレインとNchMOSのドレインとが1オーム以上の抵抗で接続され、PchMOSのドレインと容量負荷間に、スイッチング基本波周波数におけるインピーダンスがスイッチング基本波周波数における前記容量性負荷のインピーダンスの1/2より低いインピーダンスのフェライトビーズを直列接続する。

(もっと読む)

パワーオンリセット回路

【課題】パワーオン時における回路電源電圧の変化の緩急に拘らず、非動作電圧から動作電圧へ変化時にリセット信号を確実に出力するパワーオンリセット回路を提供する。

【解決手段】本発明に係るパワーオンリセット回路は、回路電源電圧を受けて充電を行う充電回路と、回路電源電圧を受けて出力電圧を出力する動作電圧設定回路と、前記充電回路の出力する充電電圧、及び、前記動作電圧設定回路の出力する出力電圧を判定して、パワーオンリセット信号を出力する電圧判定回路とを備える。

(もっと読む)

窒化物半導体装置

【課題】駆動回路への要求を緩和した使いやすい高速動作の窒化物半導体装置を提供する。

【解決手段】実施形態によれば、窒化物半導体を含む、nチャンネル型の第1〜第4トランジスタと、抵抗と、を備えた窒化物半導体装置が提供される。第1トランジスタは、第1ゲートと、第1ソースと、第1ドレインと、を有する。第2トランジスタは、第2ゲートと、第1ゲートと接続された第2ソースと、第2ドレインと、を有する。第3トランジスタは、第3ゲートと、第1ソースと接続された第3ソースと、第1ゲート及び第2ソースと接続された第3ドレインと、を有する。第4トランジスタは、第3ゲートと接続された第4ゲートと、第1ソース及び第3ソースと接続された第4ソースと、第2ゲートと接続された第4ドレインと、を有する。抵抗の一端は第2ドレインと接続され、他端は第2ゲート及び第4ドレインと接続される。

(もっと読む)

ゲート回路

【課題】本発明は、パワー素子の過電流を速やかに抑制しつつ、di/dtを小さくしてパワー素子をオフすることができるゲート回路を提供することを目的とする。

【解決手段】本発明に係るゲート回路は、パワー素子の過電流発生と同時にパワー素子のゲート電圧の一部を抵抗素子に負担させる過電流抑制手段を有する。さらに、パワー素子の過電流を抑制した後は、抵抗値の高い抵抗素子を用いてパワー素子をゆっくりオフするオフ動作遅延手段を有する。

(もっと読む)

レベル変換バススイッチ

【課題】レベル変換時の信号の立ち上がりを速くすることのできるレベル変換バススイッチを提供する。

【解決手段】実施形態のレベル変換バススイッチは、低電圧レベル信号が伝送される低電圧レベル信号線と高電圧レベル信号が伝送される高電圧レベル信号線との間に、低電圧レベルの制御信号により導通が制御されるMOSトランジスタ型のスイッチ1が接続され、高電圧レベル信号線と高電圧電源線VccBとの間に、プルアップ抵抗2が接続される。このレベル変換バススイッチでは、加速回路3が、高電圧レベル信号の立ち上がりをプルアップ抵抗2による立ち上がりよりも速くし、加速期間制御回路4が、加速回路3の作動期間を制御する。

(もっと読む)

ゲート駆動回路、およびパワー半導体モジュール

【課題】 スイッチング素子を誤動作させずに高速低損失動作が可能なゲート駆動回路を部品点数の少ない簡易な回路構成で実現する。

【解決手段】 トランス15の1次側をローサイドゲート駆動回路2の出力端子に接続し、トランス15の2次側をハイサイドスイッチング素子5のゲート入力側に接続する。ローサイド駆動回路2から正極性のゲート駆動電圧が出力されるとハイサイドスイッチング素子5のゲート‐ソース間には負極性の電圧が印加されてゲート電圧は閾値以下に抑えられるため、ローサイドスイッチング素子がターンオンする際にハイサイドスイッチング素子はオフ状態を維持する。

(もっと読む)

出力バッファー回路

【課題】出力バッファーの面積・体積・部品点数の増加を抑制するとともに、ドライブ能力を向上させることが可能な出力バッファー回路を提供する。

【解決手段】第一駆動信号LINを伝達する第一入力経路4a、第二駆動信号RINを伝達する第二入力経路4b、第一入力経路4aと対応する第一出力バッファー6a及び第二入力経路4bと対応する第二出力バッファー6bを備える出力バッファー回路1において、入力経路切り替え手段8が、ステレオモード及びモノラルモードのうち、モノラルモードでは、第一入力経路4aと第一出力バッファー6a及び第二出力バッファー6bとを電気的に接続させ、出力経路切り替え手段10が、第一出力バッファー6a及び第二出力バッファー6bと、第一入力経路4a及び第一出力バッファー6aと対応する第一負荷2aとを、電気的に接続させる。

(もっと読む)

電力用半導体素子の駆動保護回路

【課題】電力用半導体素子の制御電極の短絡動作時の電圧を通常動作時の電圧と同じ値に制限し、安全で確実な遮断を行うことが可能な電力用半導体素子の駆動保護回路の提供を目的とする。

【解決手段】本発明の電力用半導体素子の駆動保護回路は、電力用半導体素子F1と、その制御電極を駆動する駆動回路と、電力用半導体素子F1の制御電極の電圧Vgeが一定値を超えないよう制限する電圧保護回路とを備える。電圧保護回路は、電力用半導体素子F1の制御電極にエミッタが接続されたゲート放電用トランジスタTr1と、ゲート放電用トランジスタTr1にベース電位を与える電圧発生回路B1とを備え、電圧発生回路B1は、電力用半導体素子F1の駆動正電源電圧VDDから、前記駆動回路における電圧降下ΔV1を超える電圧が電力用半導体素子F1の制御電極に印加されたときに、ゲート放電用トランジスタTr1がオンできる電圧を出力する。

(もっと読む)

半導体回路

【課題】 高電位側スイッチング素子の導通を示す第1状態から前記高電位側スイッチングデバイスの非導通を示す第2状態への遷移、または前記第2状態から前記第1状態への遷移に伴い発生する過渡的な電圧ノイズに曝された場合に発生する誤信号を確実に除去する半導体回路を提供する。

【解決手段】 高電位側スイッチング素子駆動回路1は、スイッチング素子7の導通状態を変化させる場合に第1、第2のレベルシフト素子21、24のオン/オフ状態を必ず同一状態にするためのフリップフロップ52と、マスク信号S11が確実にセット信号S9、リセット信号S10を覆うようにするための第1、2、3の遅延回路44、45、46を有する。

(もっと読む)

半導体スイッチ及び無線機器

【課題】端子切替時の歪みの増加を抑制した半導体スイッチ及び無線機器を提供する。

【解決手段】実施形態によれば、電源回路と、駆動回路と、スイッチ部と、補正回路と、を備えた半導体スイッチが供給される。前記電源回路は、電源電位と異なる第1の電位を生成する。前記駆動回路は、前記第1の電位と異なる第2の電位と前記第1の電位とが供給され、端子切替信号に基づいて前記第1の電位及び前記第2の電位の少なくとも一方を出力する。前記スイッチ部は、前記駆動回路の出力に応じて共通端子と高周波端子との接続を切り替える。前記補正回路は、前記端子切替信号の変化を検出し、前記第1の電位の極性と等しい極性の電荷を前記駆動回路に供給して前記第1の電位を補正する。

(もっと読む)

ゲート駆動回路

【課題】本発明は素子のスイッチング特性を改善したゲート駆動回路に係り、素子のスイッチング特性を任意に決定でき、十分な短絡耐量と、定常損失の抑制ができるゲート駆動回路を提供することを目的とする。

【解決手段】パワースイッチング素子のゲートのオン動作を行うオン動作回路を備える。該オン動作回路は、該ゲートへの入力を第一所定値以下に保つ上限リミット部を備えることを特徴とする。

(もっと読む)

半導体スイッチ回路

【課題】入出力端子におけるアイソレーション劣化を抑制可能とする。

【解決手段】

第1の入出力端子51と第2の入出力端子52間に第1の単位スイッチ101が、第1の入出力端子51と第3の入出力端子間53に第2の単位スイッチ102が、それぞれ設けられ、第2の入出力端子52とグランドとの間に第1のシャントスイッチ103及び第1のDCカットコンデンサ49が、第3の入出力端子53とグランドとの間に第2のシャントスイッチ104及び第2のDCカットコンデンサ50が、それぞれ直列接続され、第1及び第2の単位スイッチ101,102を構成する第1乃至第4のFET1〜4のゲート・ドレイン間には、それぞれ付加容量41〜44が接続されると共に、第1の単位スイッチ101に対して第1の端子間連絡用抵抗器31が、第2の単位スイッチ102に対して第2の端子間連絡用抵抗器32が、それぞれ並列接続されたものとなっている。

(もっと読む)

無線通信装置及び高周波スイッチ回路

【課題】回路規模が小さく、かつ消費電力の小さい無線通信装置及び高周波スイッチ回路を提供する。

【解決手段】無線通信装置100は、共用アンテナ101と、整合回路110、120と、高周波スイッチ回路130と、充電電力受電回路140と、応答器150と、から構成される。高周波スイッチ回路130は、電界効果トランジスタ131、132と、検波回路と、を備える。電界効果トランジスタ131、132のソース端子は共通接続される。検波回路は共通接続点に接続され、電界効果トランジスタ131のドレイン端子から出力された高周波信号を検波し、共通接続点の電位を基準とした検波電圧を電界効果トランジスタ131、132のゲート端子に印加する。電界効果トランジスタ131、132のドレイン端子間のインピーダンスは検波電圧に従って変化する。

(もっと読む)

出力バッファ回路

【課題】 誘導性負荷を駆動する出力バッファ回路の電力損失を低減する。

【解決手段】 誘導性負荷2から出力バッファ回路100に電流が流入している場合、スルーレート制御部140は、出力バッファ回路100の出力信号VOUTの立ち上がり過程において低いスルーレートから高いスルーレートへ変化させる制御を行うとともに、出力信号VOUTの立ち下がり過程において高いスルーレートから低いスルーレートに変化させる制御を行う。また、出力バッファ回路100から誘導性負荷2に電流が流出している場合に、スルーレート制御部140は、出力信号VOUTの立ち上がり過程において高いスルーレートから低いスルーレートに変化させる制御を行うとともに、出力信号VOUTの立ち下がり過程において低いスルーレートから高いスルーレートに変化させる制御を行う。

(もっと読む)

電源電圧検出回路

【課題】簡単な構成で電源投入時にも精度よく電源電圧の状態を検出する。

【解決手段】第1スイッチ(122)と第2スイッチ(124)とは直列に接続されてスイッチ部を形成し、第1スイッチ(122)は、基準信号に基づいて開閉が制御される。判定信号生成回路(110)は、第1電源電圧(VDD)と第2電源電圧(VSS)とに基づいて電源電圧判定信号(VG)を生成し、第2スイッチ(124)は、電源電圧判定信号(VG)に基づいて開閉が制御される。第1負荷素子(126)は、第1電源電圧(VDD)とスイッチ部との間に直列に挿入される。スイッチ部は、基準信号(Vref)が所定の第1電圧を超え、電源電圧判定信号(VG)が所定の第2電圧を超えたとき回路を閉成して第1負荷素子(126)に電流を供給し、第1負荷素子(126)とスイッチ部との接続ノードから第1電源電圧(VDD)の状態を示す第1出力信号(VOUT)を出力する。

(もっと読む)

ホールド回路

【課題】保持電圧の下降または上昇傾きを良好に調整可能なホールド回路を提供すること。

【解決手段】ホールド回路10は、入力端子20、第1出力端子22、基準電圧端子24、オペアンプ30、ダイオード32、コンデンサ36、抵抗R0、電圧発生回路50、を備えている。コンデンサ36は、一端が接続点26に接続され、他端が基準電圧端子24に接続される。抵抗R0は、一端が接続点26に接続される。ダイオード52のアノードが、オペアンプ38を介して接続点26に接続される。抵抗R0の他端と中間接続点58とが接続される。オペアンプ30は、非反転入力端子30bが入力端子20に接続され、反転入力端子30aが接続点26に接続され、出力端子30cがダイオード32に接続される。電圧発生回路50は、ダイオード52に入力される出力電圧V22から変化させたオフセット電圧V23を生成して、中間接続点58から出力する。

(もっと読む)

141 - 160 / 1,471

[ Back to top ]