Fターム[5J055EY01]の内容

Fターム[5J055EY01]の下位に属するFターム

Fターム[5J055EY01]に分類される特許

101 - 120 / 1,471

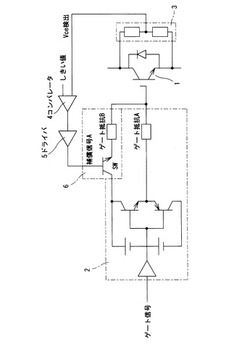

半導体スイッチング素子のゲート制御回路

【課題】スイッチング素子の発熱を抑制した過電圧抑制ゲート制御を確実、容易にし、さらにスイッチング素子を複数直列接続した半導体スイッチ回路における発振防止と分担電圧のバランス制御を確実、容易にする。

【解決手段】ゲートドライブ回路2によるゲート抵抗Aを通したIGBT1の主ゲート電流とは独立して、電圧補償ゲート制御回路3〜6はIGBT1のコレクタ・エミッタ間電圧Vceがしきい値を超えたときにゲート抵抗Bを通して電圧補償ゲート電流を注入し、電圧Vceがしきい値を下回ったときに電圧補償ゲート電流の注入をオフする。

ゲート抵抗Aの抵抗値に対してゲート抵抗Bの抵抗値を小さくする。電圧補償ゲート電流を注入した後にこのゲート電流の注入量とほぼ同じ電荷量分をIGBT1からゲート電流として引き抜く。

(もっと読む)

ゲートタイミング制御回路

【課題】半導体スイッチ,負荷電流,温度,主回路構成等によるサージ電圧の波形に応じて半導体スイッチの動作タイミングを調整することなく、各半導体スイッチの電圧分担を均等化させる。

【解決手段】直列接続された複数の半導体スイッチA,Bに出力されるゲート信号のタイミングを調整するゲートタイミング制御回路3において、コンパレータ4,4により、各半導体スイッチA,BのVce検出(A),(B)と、予め設定されたしきい値とを比較してVce検出における立ち上がりのタイミングを示すVce信号(A),(B)を出力する。そして、時間差制御部8において、ゲート信号に基づいて、前記各Vce信号(A),(B)の変化のタイミングが整合するように生成されたゲート出力(A),(B)をゲートドライバ2に出力する。

(もっと読む)

半導体装置

【課題】インバータ回路とそれを構成するスイッチ素子を駆動・制御する駆動・制御回路において、追加回路規模が少なく、所望の負電位を動的に印加できる駆動・制御回路、また、インバータ回路における短絡電流を削減し、損失の少ない電力変換回路を提供する。

【解決手段】半導体装置において、第1,第2スイッチ素子(下側アームのスイッチ素子LSW,同様の上側アームのスイッチ素子)を有するインバータ回路と駆動回路(L側ゲート駆動回路LGD,同様のH側ゲート駆動回路)と制御回路とを有し、駆動回路は、スイッチ素子のゲート電極をソース電位に駆動する回路と、スイッチ素子のゲート電極を負電位に駆動する回路とを有し、負電位に駆動する回路の出力ノードとスイッチ素子との間に直列にコンデンサが接続され、制御回路は、スイッチ素子がオフ状態からオン状態になる直前のスイッチ素子のゲート電極の電圧をソース電位と同じであるように制御する。

(もっと読む)

半導体デバイス駆動回路及び半導体装置

【課題】電源電圧が変動しても半導体デバイスのオン動作及びオフ動作を安定して駆動できる半導体デバイス駆動回路を得る。

【解決手段】ドライブ回路10は、入力回路11より得られる制御信号S11に基づき、インバータG4から電源電圧VCCにより決定される“H”(オンレベル)、あるいは接地電圧GNDにより決定される“L”(オフレベル)の出力電圧VOUT1を駆動信号として半導体デバイスQ1のゲートに出力する。基準電源部14は抵抗R1及びR2の直列接続により、電源電圧VCC,接地電圧GND間の電位差を所定の分圧比率(抵抗R1及びR2による抵抗比)で分圧して得られる電圧が基準電圧VREF1として得られる。バッファ回路8は基準電圧VREF1により決定される基準信号となる出力電圧VOUT2を半導体デバイスQ1のソースに付与する。

(もっと読む)

電力用半導体装置

【課題】複数の電力用半導体素子を並列接続する場合において、スイッチング損失を従来よりも低減する。

【解決手段】電力用半導体装置200は、互いに並列に接続された第1および第2の電力用半導体素子Q1,Q2と、駆動制御部100とを備える。駆動制御部100は、外部から繰返し受けるオン指令およびオフ指令に応じて第1および第2の電力用半導体素子の各々をオン状態またはオフ状態にする。具体的には、駆動制御部100は、オン指令に対して、第1および第2の電力用半導体素子Q1,Q2を同時にオン状態にする場合と、第1および第2の電力用半導体素子Q1,Q2の一方をオン状態にした後に他方をオン状態にする場合とに切替え可能である。駆動制御部100は、オフ指令に対して、第1および第2の電力用半導体素子Q1,Q2の一方をオフ状態にした後に他方をオフ状態にする。

(もっと読む)

スイッチング素子の駆動回路

【課題】オフ保持用スイッチング素子46をオフ状態とすべき期間において、この素子が誤ってオフ状態とされることに起因するスイッチング素子S*#の信頼性の低下を抑制することのできるスイッチング素子の駆動回路を提供する。

【解決手段】オフ保持回路48は、信号生成部26の操作信号INを入力としてゲートの充電処理の実行中であると判断された場合、オフ保持用スイッチング素子46をオフし、操作信号INを入力としてゲートの放電処理の実行中であると判断されて且つゲート電圧検出部50の出力信号GPRを入力としてゲート電圧Vgeが低いと判断された場合、オフ保持用スイッチング素子46をオンする。ここで、上記駆動回路は、ゲート電圧Vgeが閾値電圧を跨いでから出力信号GPRの論理が反転するまでの時間を、操作信号INを入力としてオフ保持回路48によって把握される充電処理指示時間の最小値以下とするように構成される。

(もっと読む)

絶縁ゲート型スイッチング素子のゲートの電位を制御する半導体装置、及び、回路

【課題】 絶縁ゲート型スイッチング素子のゲートの電位を制御する半導体装置であって、低速スイッチング用と高速スイッチング用とで共通して使用可能な半導体装置を提供する。

【解決手段】 絶縁ゲート型スイッチング素子のゲートの電位を制御する信号を出力する半導体装置であって、第1信号出力端子を有しており、第1電位と第1電位よりも高い第2電位の間で変動する基準信号の入力を受けるか、または、内部で前記基準信号を生成することが可能であり、前記基準信号が第1電位にあるときには第3電位となり、前記基準信号が第2電位にあるときには第3電位よりも高い第4電位となる信号を第1信号出力端子に出力する第1動作と、前記基準信号が第1電位にあるときには第4電位となり、前記基準信号が第2電位にあるときには第3電位となる信号を第1信号出力端子に出力する第2動作とを切り換えて実行することができる。

(もっと読む)

リセット回路

【課題】減電検出を利用して確実にリセットを掛ける。

【解決手段】整流電圧V+をレギュレータ24にてレギュレートした定電圧3.3Vを駆動電圧とされるマイコン30のリセット端子に接続される端子2と抵抗R1を介して定電圧3.3Vを入力される端子4とを備え、端子4の入力電圧が第1閾値を下回るとマイコン30にリセット信号を出力するリセットIC12と、抵抗R2を介して端子4にコレクタを接続され、エミッタをグランドに接続され、スイッチングトランス21の出力が所定レベルを下回るとオンするように構成されたトランジスタQ1と、を備え、トランジスタQ1がオンすると端子4に第1閾値を下回る電圧を入力する。

(もっと読む)

スイッチングアンプ

【課題】 2つの出力素子の入力が共にハイレベルになり次に電源オン状態に移行する際に動作を開始することができないとい問題を解決する。

【解決手段】 電源制御手段16は、スイッチングアンプ10が電源オフ状態に移行する場合に、スイッチSWがオフ状態になり、コンデンサC102を強制的に放電させ、第2電源電圧V2に対する基準電位V3を強制的に低下させる。基準電位V3に対するロジック電源電圧Vddは、基準電位V3と同じだけ低下していくので、基準電位V3から見たロジック電源電圧Vddは固定される。定電流回路は、第2電源電圧V2に対する基準電位V3の低下に伴い、定電流Iを減少させ、第1の電流I1および第2の電流I2を減少させる。従って、基準電位V3から見たロジック電源電圧Vddが低下しないうちに、第1の電流I1、第2の電流I2を減少させ、パルス発生手段の動作を正常な状態で終了できる。

(もっと読む)

スイッチング回路

【課題】スイッチング素子の動作に起因するノイズの大きさが低減された、小型で製造コストの低いスイッチング回路を提供する。

【解決手段】スイッチング素子と、一定周期でパルス波のドライバ信号を出力するドライバ信号出力回路と、ドライバ信号のパルス波の周期を複数含む一定期間内において駆動力を変化させながら、ドライバ信号の周期に同期してスイッチング素子を駆動する駆動回路とを備える。

(もっと読む)

容量性スピーカ駆動回路

【課題】高音の音声信号が所定のレベル以上で所定時間以上入力されたときに、利得を低減させて高音過電流が発生することを防止する。

【解決手段】出力ドライバのパワートランジスタに流れる電流が所定時間以上にわたって所定値を超えた場合に高音過電流検出信号を発生する高音過電流検出手段と、前記高音過電流検出信号が発生されると前記プリアンプの通過周波数帯域を低くさせる通過周波数帯域切替手段とを設けた。

(もっと読む)

半導体装置および電子機器

【課題】良好な逆回復特性と良好なEMCとを同時に実現することが出来て、かつ、従来の半導体装置よりも安価である半導体装置及び電子機器を提供する。

【解決手段】半導体装置1は、FET3のソースとMOSFET4のドレインとが接続されるとともに、一端が、FET3のゲートに接続され、他端が、MOSFET4のソースに接続される抵抗Rgsと、アノードが、FET3のゲートに接続され、カソードが、MOSFET4ソースに接続されるダイオードD1とを備える。

(もっと読む)

過電流保護電源装置

【課題】直流電源17からスイッチ用のFET18を経て負荷16へ電力を供給する電源装置においては、2種類の保護回路が設けられていた。第1は、該FETの温度を検出し、所定温度に達したら該FETをオフする回路である。第2は、デッドショート時のような大過電流が流れた場合には、電流を所定電流に制限する電流制限回路である。保護回路を2種類設けると、部品コストが大になっていた。

【解決手段】比較基準電圧生成回路40を電流供給部41と比較基準電圧発生抵抗部46とで構成し、比較基準電圧VX を生成する。過電流検出電圧生成回路50を電流供給部51と過電流検出抵抗部54とで構成し、FET18の電圧VDSが増大すると減少する電流検出電圧VY を生成する。電圧VDSの増大を検出してFET18をオフすれば、過電流保護も過熱保護も可能となる。

(もっと読む)

半導体スイッチング素子駆動回路

【課題】 高コスト化、サイズ大型化を抑制し、短絡保護回路が制限する電流値がばらついても、過電流保護回路を確実に作動させる半導体スイッチング素子駆動回路を提供する。

【解決手段】半導体スイッチング素子駆動回路は、ゲート端子への電圧の印加により第1端子および第2端子間に主電流を流す半導体スイッチング素子Q1と、主電流の大きさに比例する電流値または電圧値が閾値を超えたとき、主電流が所定時間の間、所定の電流値を超える過電流となったと判断して主電流を低下させる過電流保護回路OPと、主電流が所定時間より短時間で過電流よりさらに大きい過電流となる場合に、ゲート端子に印加するゲート電圧を過電流保護回路による主電流の低下よりも早く低下させる短絡保護回路SPと、短絡保護回路の主電流の低下作動時に閾値を小さくする閾値変更回路TCと、を有する。

(もっと読む)

リセット回路

【課題】複数の電源電圧を駆動電圧とするSoC IC(System on a Chip Integrated Circuit)に対し、負荷変動やノイズに影響されること無く、複数の電源電圧の供給とリセット解除タイミングとのシーケンスを守ってリセットを行う。

【解決手段】供給ラインL1とリセット端子16との間においてエミッタを供給ラインL1に向けつつコレクタをリセット端子16に向けて介挿されたトランジスタTr1と、トランジスタTr1のベースとグランドとの間においてコレクタをトランジスタTr1のベースに向けつつエミッタをグランドに向けて介挿されたトランジスタTr2と、トランジスタTr1のコレクタとグランドとの間においてコレクタをトランジスタTr2のコレクタに向けつつエミッタをグランドに向けて介挿されたトランジスタTr3とを備える。

(もっと読む)

駆動回路、駆動信号出力回路及びインクジェットヘッド

【課題】出力する駆動信号の遅延を小さくし且つ小型化した安価な駆動回路、駆動信号出力回路及びインクジェットヘッドを実現することである。

【解決手段】駆動回路30は、負荷を駆動するプッシュ側のMOSFET32及びプル側のMOSFET33と、アノード、カソードがMOSFET32のゲート、ソースに接続されたツェナーダイオード38と、アノード、カソードがMOSFET33のソース、ゲートに接続されたツェナーダイオード39と、昇圧回路31の出力端とMOSFET32のゲートとに接続された抵抗36と、昇圧回路31の出力端とMOSFET33のゲートとに接続された抵抗37と、抵抗36、抵抗37に並列に接続されたスピードアップコンデンサ42,43と、を備える。MOSFET32,33のソースが高圧側、グランドに接続され、MOSFET32,33のドレインが互いに接続される。

(もっと読む)

負荷駆動装置

【課題】急激なアンダーシュート波形が生成されることにより発振状態になって不安定な動作を引き起こすことを防止する。

【解決手段】パワー素子4をオンさせる際に、パワー素子4の制御端子41に比較的大きな電流を供給することで制御端子41の電圧を比較的大きな勾配で上昇させつつ、制御端子41の電圧がクランプ電圧に至ってから電圧状態が安定化するまでは、制御端子41への比較的大きな電流の供給を保持する。そして、制御端子41の電圧状態が安定化した後に、制御端子41への電流供給が定電流回路31のみから為されるようにし、比較的小さな電流が制御端子41に供給されるようにする。

(もっと読む)

負荷駆動装置

【課題】よりゲート電圧の傾きのバラツキを小さくすることで、スイッチング損失や電圧サージおよびピーク電流のバラツキを小さくする。

【解決手段】オフ保持デバイス5に対してオフ許可信号が禁止状態から許可状態に切り替わったことが伝わることを制御遅延演算回路6によって遅延時間だけ遅らせるようにする。これにより、遅延時間経過後に、既に定電流の狙い値まで達して安定した値になっている定電流駆動回路30の出力電流をスイッチング素子1のゲート1aに供給されるようにできる。したがって、ゲート電圧の立ち上がり傾きのバラツキを小さくすることができ、スイッチング損失や電圧サージおよびピーク電流のバラツキを小さくすることが可能となる。

(もっと読む)

半導体装置と、それを用いたインバータ、コンバータおよび電力変換装置

【課題】ターンオン時間のばらつきが小さな半導体装置を提供する。

【解決手段】この半導体装置は、ノードN1,N2間に直列接続された高耐圧、高GmのトランジスタQ1および低耐圧、低GmのトランジスタQ2と、トランジスタQ2に並列接続された低耐圧、高GmのトランジスタQ3とを含む。トランジスタQ2をオンさせるとトランジスタQ1がオンし、さらにトランジスタQ3をオンさせるとノードN1,N2間が導通状態になる。したがって、低耐圧のトランジスタQ2をオンさせて高耐圧のトランジスタQ1をオンさせるので、ターンオン時間のばらつきが小さくなる。

(もっと読む)

過電流保護電源装置

【課題】直流電源11からスイッチ用のFET12を経て負荷14へ電力を供給する電源装置においては、2種類の保護回路が設けられていた。第1は、該FETの温度を検出し、所定温度に達したら該FETをオフする回路である。第2は、デッドショート時のような大過電流が流れた場合には、電流を所定電流に制限する電流制限回路である。保護回路を2種類設けると、部品コストが大になっていた。

【解決手段】FETのドレイン・ソース間電圧に比例した電流Iを生成する電流変換回路4と、容量素子を含む一次遅れ回路として構成された過電流検出用電圧発生回路6とを直列接続し、その接続点Sの電圧を過電流検出用電圧VS とする。過電流検出回路5から制御回路3へ過電流検出信号が入力されて来たとき、制御回路3はFET12をオフする。過電流検出用電圧発生回路6の回路定数の設定を工夫することにより、VS を速やかに大になるようにすることが出来、1種類の保護回路で大過電流時にも保護が出来る。

(もっと読む)

101 - 120 / 1,471

[ Back to top ]