Fターム[5J055EZ54]の内容

電子的スイッチ (55,123) | 機能的回路 (8,211) | 電源回路、特徴がある定電圧回路 (631) | 昇圧回路 (91)

Fターム[5J055EZ54]に分類される特許

1 - 20 / 91

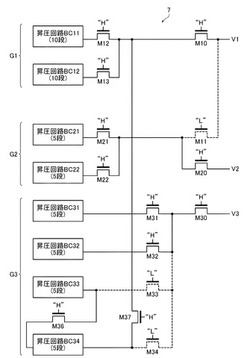

電圧生成回路

【課題】回路面積を低減させることのできる電圧生成回路を提供する。

【解決手段】一の実施の形態に係る電圧生成回路は、第1の電圧値の第1電圧を発生させる第1の昇圧回路と、第2の電圧値の第2電圧を発生させる複数の第2の昇圧回路を含む第2昇圧回路群とを有する。複数の第2の昇圧回路は、第1の状態から第2の状態に移行する際に互いに直列に接続され第1昇圧回路とともに第1電圧を発生可能に構成されている。

(もっと読む)

昇降圧回路、スイッチ回路

【課題】駆動用のMOSトランジスタのオン抵抗が小さく、リーク電流の発生を防ぎ、しかも小型化、低消費電力化に適した昇降圧回路を提供する。

【解決手段】入力電圧IN2が入力される入力端子104、入力電圧IN2に基づいてVCCまたはGNDを出力するMOSトランジスタ201、203、入力電圧IN2に基づいて2VCCまたはGNDを出力するMOSトランジスタ202、204、MOSトランジスタ201、202に一端が接続され、他端がMOSトランジスタ202、204に接続される容量素子206、ソース・ドレイン端子の一方に2VCCが供給され、ソース・ドレイン端子の他方にVCCが供給され、2VCCまたはGNDがゲート端子に供給され、2VCCまたはGNDによってオン、オフされるMOSトランジスタ205と、によって昇圧回路を構成する。

(もっと読む)

スイッチング回路及び電源装置

【課題】 半導体スイッチが故障することを抑制することのできるスイッチング回路を提供する。

【解決手段】

電源装置1は、電流路内に配置されオン・オフ動作可能なメインFET131と、メインFET131にオン・オフ動作を行わせる制御部19と、メインFET131の温度を検出する第1サーミスタ134と、電流路内においてメインFET131と並列に配置されオン・オフ動作可能なサブFET132と、を備え、制御部19は、メインFET131の温度が所定温度を超えた場合に、オン・オフ動作を行わせるFETをメインFET131からサブFET132に切り替える。

(もっと読む)

昇圧回路及びその給電方法

【課題】簡略化された回路構成でノイズ低減効果を持つ多相駆動型の昇圧回路を実現する。

【解決手段】昇圧回路は、所定周期のクロック信号を出力する発振回路と、前記クロック信号の1本の配線に直列接続され、トータル遅延時間が前記所定周期よりも長い複数の遅延回路と、前記複数の遅延回路に対応して前記1本の配線に接続された複数の分割昇圧回路と、を含む。

(もっと読む)

ゲート駆動回路、電力変換回路、3相インバータ、及びゲート駆動方法

【課題】電力変換回路において、ノーマリオン型トランジスタを利用したスイッチング素子への貫通電流を抑制する。

【解決手段】ハイサイドトランジスタ21とローサイドトランジスタ22の少なくとも一方は、ノーマリオン型トランジスタである。2つのゲート駆動回路11、12の少なくとも一方は、正電源から供給される第1電源電圧VDDと、負電圧源30から供給され接地電圧GNDよりも低い第2電源電圧VNEGとに応じた駆動電圧GH、GLを、ノーマリオン型のトランジスタのゲートに出力する。制御回路40は、第2電源電圧VNEGが参照電圧Vrefよりも高い場合、ハイサイドトランジスタ21に流れるドレイン電流を遮断する。

(もっと読む)

半導体装置

【課題】発光装置に含まれる発光素子の発光輝度を周囲の情報に応じて調節する表示シス

テムを提供する。

【解決手段】本発明において、センサー2011が周囲の情報を電気信号として検出し、

これをCPU2013は、あらかじめ設定しておいた比較データに基づきEL素子の発光

輝度を補正するための補正信号に変換する。この補正信号が電圧可変器2010に入力さ

れることにより、電圧可変器2010が所定の補正電位をEL素子に印加する。以上の表

示システムによりEL素子2003の発光輝度を制御することができる。

(もっと読む)

インターフェース回路

【課題】ノイズを低減することができるインターフェース回路を提供することを課題とする。

【解決手段】インターフェース回路は、電源電圧端子が第1の電源電圧ノードに接続され、入力信号を増幅する第1のバッファ(111)と、第2の電源電圧ノード及び前記第1のバッファの電源電圧端子間に接続されるスイッチ(124)と、前記第1のバッファの入力信号がローレベルからハイレベルに立ち上がると、遅延時間経過後に前記スイッチをオフからオンに切り換える第1の制御回路(127)とを有する。

(もっと読む)

負荷駆動回路

【課題】簡単な構成で負荷オープン状態を検出することができる負荷駆動回路を提供する。

【解決手段】電源端子T1に入力される入力電圧Vinよりも低い基準電圧V1と出力端子T2の電圧Voutとを比較する第1のコンパレータ8と、スイッチング素子2がオフ状態で、且つ負荷オープン状態である場合に、出力端子T2の電圧Voutを基準電圧V1よりも高く、且つ入力電圧Vinよりも低いclamp電圧にクランプするクランプ回路7とを備えることにより、第1のコンパレータの出力によって、負荷オープン状態を検出する。また、入力電圧Vinよりも低く且つclamp電圧よりも高い基準電圧V2と出力端子T2の電圧Voutとを比較する第2のコンパレータ9を備えることにより、第1のコンパレータ及び第2のコンパレータ9の出力によって、負荷オープン状態と出力天絡状態とを検出する。

(もっと読む)

半導体装置

【課題】半導体を用いた半導体装置として、論理回路がある。論理回路にはダイナミック論理回路とスタティック論理回路とがあり、トランジスタ等を用いて構成される。ダイナミック論理回路は情報を一定期間保持することができる。そのため、ダイナミック論理回路は、スタティック論理回路と比較して、トランジスタからのリーク電流が問題となる。

【解決手段】論理回路は、オフ電流が小さい第1のトランジスタと、ゲートが電気的に接続された第2のトランジスタと、を有し、第2のトランジスタのゲートのノードには第1のトランジスタを介して電荷が供給される。ノードに対して、第1及び第2の容量を介して電荷を供給する。電荷の状態に応じて、第2のトランジスタのオン、オフが制御される。第1のトランジスタは、チャネル形成領域に酸化物半導体を有する。

(もっと読む)

制御信号発生回路およびそれを用いた半導体装置

【課題】半導体装置の制御に好適な制御信号発生回路を提供する。

【解決手段】ジョンソンカウンタ31は、フリップフロップFF1〜FF4およびゲート回路41〜44を含み、順次入力されるスタート信号ST1〜ST4に応答してそれぞれ制御信号C1〜C4を「H」レベルにした後、順次入力されるストップ信号SP1〜SP4に応答してそれぞれ制御信号C1〜C4を「L」レベルにする。したがって、多数のフリップフロップを用いることなく、所望の時間間隔で制御信号C1〜C4を順次「H」レベルにし、順次「L」レベルにすることができる。

(もっと読む)

半導体装置

【課題】半導体を用いた半導体装置として、論理回路がある。論理回路にはダイナミック論理回路とスタティック論理回路とがあり、トランジスタ等を用いて構成される。ダイナミック論理回路は情報を一定期間保持することができる。そのため、ダイナミック論理回路は、スタティック論理回路と比較して、トランジスタからのリーク電流が問題となる。

【解決手段】論理回路は、オフ電流が小さい第1のトランジスタと、ゲートが電気的に接続された第2のトランジスタと、を有し、第2のトランジスタのゲートのノードには第1のトランジスタを介して電荷が供給される。ノードに対して、複数の容量を介して電荷を供給する。電荷の状態に応じて、第2のトランジスタのオン、オフが制御される。第1のトランジスタは、チャネル形成領域に酸化物半導体を有する。

(もっと読む)

駆動回路、駆動信号出力回路及びインクジェットヘッド

【課題】出力する駆動信号の遅延を小さくし且つ小型化した安価な駆動回路、駆動信号出力回路及びインクジェットヘッドを実現することである。

【解決手段】駆動回路30は、負荷を駆動するプッシュ側のMOSFET32及びプル側のMOSFET33と、アノード、カソードがMOSFET32のゲート、ソースに接続されたツェナーダイオード38と、アノード、カソードがMOSFET33のソース、ゲートに接続されたツェナーダイオード39と、昇圧回路31の出力端とMOSFET32のゲートとに接続された抵抗36と、昇圧回路31の出力端とMOSFET33のゲートとに接続された抵抗37と、抵抗36、抵抗37に並列に接続されたスピードアップコンデンサ42,43と、を備える。MOSFET32,33のソースが高圧側、グランドに接続され、MOSFET32,33のドレインが互いに接続される。

(もっと読む)

表示装置

【課題】表示装置の走査信号線の駆動回路において、走査信号線の出力波形なまりを改善し、表示品質を高めた表示装置を提供する。

【解決手段】表示装置は、複数の信号線Gnに対して、順に画素トランジスタを導通させる電位であるアクティブ電位を印加する駆動回路210を備え、前記駆動回路210は、前記複数の信号線のうちの一の信号線である出力信号線の一端に、より上位の前記出力信号線において出力されるアクティブ電位が入力されることに起因して、クロック信号を印加してアクティブ電位を出力させる主駆動回路240と、前記出力信号線の他端、及び前記クロック信号の信号線が、ソース/ドレインを介して接続されたトランジスタである補助トランジスタを含む補助駆動回路250と、を有する。

(もっと読む)

過電圧保護回路

【課題】電圧伝達経路における電圧降下が小さい過電圧保護回路を提供する。

【解決手段】入力電圧と第1の電圧とを入力して、昇圧した第2の電圧を、電圧伝達経路110の遮断または導通を制御するスイッチ回路SWのMOSトランジスタPSWのゲートに供給する昇圧回路CPと、MOSトランジスタPSWのゲートに蓄積された電荷を放電する放電回路DCGとを備える。

(もっと読む)

スイッチング素子駆動回路

【課題】スイッチング素子駆動回路において、スイッチング素子のスイッチング損失を抑制する。

【解決手段】 ゲート電圧検出回路201は、スイッチング素子11のゲート電圧Vgsを検出し、このゲート電圧がスイッチング素子11の閾値電圧未満に設定された所定電圧未満のとき、Hレベルの昇圧指示信号を出力する。電圧制御回路103は、前記昇圧指示信号がLレベルの間は、制御電源102の所定電圧V1をそのまま出力し、前記昇圧指示信号がHレベルの間は、前記所定電圧V1を昇圧した電圧V2を出力する。駆動信号出力回路104は、PWMパルス出力回路111から出力されるPWMパルスの電圧を電圧制御回路103から出力される電圧に増幅する。従って、駆動信号出力回路104からスイッチング素子11への駆動信号は、前記PWMパルスがHレベルになった時に、先ず昇圧された電圧V2となり、スイッチング素子11のゲート電圧Vgsが所定電圧にまで上昇すると、所定電圧V1となる。

(もっと読む)

半導体装置

【課題】高電位側スイッチ素子の十分な駆動電圧を実現した半導体装置を提供する。

【解決手段】半導体装置は、入力電圧用端子、出力用端子、接地電位用端子、電源電圧用端子、第1端子を有し、入力電圧用端子と出力用端子との間にソースードレイン経路を有する第1MOSを含む第1チップ、出力用端子と接地電位用端子との間にソースードレイン経路を有する第2MOSを含む第2チップ、第1MOSのゲートにその出力が接続された第1駆動回路、第2MOSのゲートにその出力が接続された第2駆動回路、電源電圧用端子に接続されたドレインと、第1端子に接続されたソースとを有するPMOSとを含む第3チップが一つのパッケージ内に封止され、第1端子と出力用端子との間に容量が接続可能とされ、第2MOSがオンとされるとき、PMOSはオンとされ、第2MOSがオフとされるとき、PMOSはオフとされる。

(もっと読む)

高周波モジュールおよび無線通信システム

【課題】低コスト化または小型化を実現可能なマルチバンド対応の高周波モジュールおよび無線通信システムを提供する。

【解決手段】例えば、高周波電力増幅装置HPAIC1は、GSM用のパワーアンプ回路部PABK_LB(PABK_HB)と、GSMかW−CDMAかを選択するモード設定信号Mctlを受けて、アンテナスイッチ制御信号SctlをVSW1レベルかVSW2レベルで出力する制御回路を備える。VSW2は、発振回路OSCからのクロック信号を用いてVSW1を昇圧することで生成される。HPAIC1は、MctlによってGSMが選択された際には、OSCを停止させると共にVSW1レベルのSctlをアンテナスイッチ装置ANTSWに出力し、MctlによってW−CDMAが選択された際には、OSCを用いてVSW2レベルのSctlをANTSWに出力する。

(もっと読む)

集積回路装置、電子機器及び集積回路装置の製造方法

【課題】 出力端子から出力される電圧値に応じて複数種の中から選択される耐圧に設定される集積回路装置等の提供すること。

【解決手段】 第1の耐圧を有する第1の出力トランジスター構造Tr_M1,Tr_M2と、第1の耐圧よりも高い第2の耐圧を有する第2の出力トランジスター構造Tr_H1,Tr_H2とが形成された半導体基板に、マスクを変えて配線して所定の耐圧に設定される集積回路装置である。配線により第1の耐圧が選択されると、第1,第2の出力トランジスター構造の双方が出力端子OUTと接続され、第2の出力トランジスター構造は、ダイオード接続されて静電気保護素子D1,D2を形成する。配線により第2の耐圧が選択されると、第1の出力トランジスター構造は出力端子OUTに非接続とされ、第2の出力トランジスター構造が出力端子OUTと接続される第2耐圧出力段トランジスターを形成する。

(もっと読む)

入出力回路

【課題】昇圧した電圧でLCDを駆動するような場合でも、その共用の入出力端子から実用的な出力データ信号の出力が可能となる。

【解決手段】入出力回路100において、スリーステート出力バッファが出力データ信号とLCD駆動信号の両方に対してそれぞれ第1、第2出力バッファ106、108として設けられ、第1出力バッファ106を構成するPチャンネルMOSトランジスタ116のソース端子に電源電圧V1が供給され、且つ出力データ信号が出力として選択されていない状態でPチャンネルMOSトランジスタ116、118のバックゲート端子に電源電圧V1から昇圧された昇圧電圧V2が供給され、更に、第2出力バッファ108を構成するPチャンネルMOSトランジスタ116のソース端子とバックゲート端子とに昇圧電圧V2が供給される。

(もっと読む)

負荷駆動回路

【課題】ハイサイドスイッチとして用いられるNチャネル型のMOSFETのターンオフ動作に際し、簡単な構成でオフ時間Toffと立下り時間Tfの最適化が可能な負荷駆動回路を提供する。

【解決手段】電源3と負荷1との間に接続されたハイサイドスイッチとしてパワーMOSFET2を用いた負荷駆動回路10であって、パワーMOSFET のゲート電圧Vgと電源3の電源電圧Vpとを比較する比較回路11と、パワーMOSFET2のターンオフ動作においてパワーMOSFET2のゲート端子から電荷を放電させる遮断回路12とを具備し、遮断回路12によってパワーMOSFET2のゲート端子から電荷を放電させる放電速度は、ゲート電圧Vgが電源電圧Vpより高い場合の放電速度よりも、ゲート電圧Vgが電源電圧Vpより低い場合の放電速度が遅くなるように設定されている。

(もっと読む)

1 - 20 / 91

[ Back to top ]