Fターム[5J055FX04]の内容

電子的スイッチ (55,123) | 制御、帰還信号の発生 (8,841) | 帰還を行うもの (2,113) | 電気信号に変えられる現象、物理量 (2,102) | 電流値 (552)

Fターム[5J055FX04]に分類される特許

1 - 20 / 552

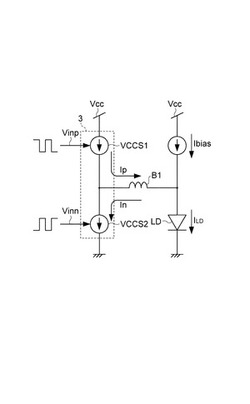

駆動回路、及び、光送信装置

【課題】変調信号の大きさ及び応答速度を向上可能な駆動回路及び光送信装置を提供する。

【解決手段】差動信号の入力に応じて発光素子LDの駆動電流を増減する駆動回路3である。差動信号の正相信号Vinpが入力される端子と、差動信号の逆相信号Vinnが入力される端子と、発光素子LDのアノードに接続されている端子と、正相信号Vinpが入力される端子に接続されている正相信号処理回路と、逆相信号Vinnが入力される端子に接続されている逆相信号処理回路と、アノードが接続されている端子に接続されている第1及び第2の電圧制御電流源回路を備える。第1の電圧制御電流源回路には、正相信号Vinpに対応する電圧及び逆相信号Vinnの逆相に対応する電圧が入力され、第2の電圧制御電流源回路には、逆相信号Vinnに対応する電圧及び正相信号Vinpの逆相に対応する電圧が入力される。

(もっと読む)

過電流検出回路および負荷駆動装置

【課題】回路用電源電圧としてむやみに高い電圧を用いることなく、シャント抵抗の低電位側端子の電圧がグランド電位付近となる異常が原因で生じる過電流を検出する。

【解決手段】検出電流出力部11は、シャント抵抗Rsの各端子電圧を入力し、その入力した電圧から負荷2に流れる電流に応じた検出電流を出力する。過電流判定部12は、検出電流に基づいて負荷2に過電流が流れているか否かを判定する。検出電流出力部11において、通常時に駆動用電源電圧Vdに近い電圧が印加される部分と、回路用電源電圧Vcに近い電圧が印加される部分との間の経路に第1ダイオードD1および第2ダイオードD2を逆方向に介在させることにより、第1トランジスタT1および第2トランジスタT2がブレークダウンして電流が流れることを阻止する。

(もっと読む)

電磁機器駆動装置および電磁機器の駆動方法

【課題】電磁機器の累積使用量が多くなっても少ないと同じ一定時間で電磁機器を動作状態から停止状態に移行させる。

【解決手段】電磁機器駆動装置は、励磁用電源から電磁コイルへの通電が停止したときに逆起電力によって電磁コイルの両端間に生じる電圧をクランプするフリーホイール回路と、フリーホイール回路によってクランプされた電圧が、電磁機器の累積使用量が少ないときよりも多いときの方が高くなるように、フリーホイール回路の動作を制御するコントローラーと、を備える。

(もっと読む)

誘導性負荷駆動装置

【課題】電流回生ルートから電流還流ルートへの切替時におけるホールドコンデンサの電荷抜けを抑制して電流検出精度の向上を実現可能な誘導性負荷駆動装置を提供する。

【解決手段】第1のスイッチング素子と、第2のスイッチング素子と、還流回路と、逆起電流回生回路と、第2のスイッチング素子とアースとの間に介挿されたシャント抵抗とを備えた誘導性負荷駆動回路から誘導性負荷に供給される駆動電流を検出する誘導性負荷駆動装置であって、シャント抵抗の両端に接続された差動増幅器と、第1及び第2のスイッチング素子を制御するプロセッサと差動増幅器の出力端子とを結ぶ配線に介挿されたサンプルスイッチと、プロセッサから第2のスイッチング素子に出力される制御信号がオンレベルに遷移してから所定の遅延時間の経過後にサンプルスイッチをオンにさせる遅延回路とを備える。

(もっと読む)

スイッチ制御装置

【課題】互いにオンオフ状態が反転するように制御すべき2つのスイッチング素子の特性に応じて容易にデッドタイムを調整可能なスイッチ制御装置を提供する。

【解決手段】互いにオンオフ状態が反転するように制御する第1及び第2のスイッチング素子を備えるスイッチ制御装置であって、前記第1及び第2のスイッチング素子の内、一方のスイッチング素子に出力する制御信号をオフレベルに切替えた時点から、コンデンサの容量で設定される設定期間後に他方のスイッチング素子に出力する制御信号をオンレベルに切替える信号を出力する制御信号生成回路を備える。

(もっと読む)

半導体集積回路

【課題】不具合の発生が抑制された半導体集積回路を提供する。

【解決手段】電圧レベルの高いHi信号、及び、該Hi信号よりも電圧レベルの低いLo信号が異なるタイミングで入力される第1入力端子と、Hi信号が常時入力される第2入力端子と、第1入力端子のHi信号によって第1動作状態、第1入力端子のLo信号によって第2動作状態に制御される素子と、を有する半導体集積回路であって、第2入力端子とグランドとの間にスイッチング素子が設けられており、該スイッチング素子は、第1入力端子にHi信号が入力されている時にOFF状態、第1入力端子にLo信号が入力されている時にON状態となる。

(もっと読む)

出力ドライバー回路

【課題】nMOSトランジスタM2のゲート−ソース間に加わる電圧を耐圧電圧未満に制限する際に消費電流の増加を抑制する。

【解決手段】pMOSトランジスタM1がオフし、かつnMOSトランジスタM2がオンしたとき、ツェナーダイオードZD2により、nMOSトランジスタM2のゲート端子とソース端子との間の電圧を一定電圧に制限する。nMOSトランジスタM2のゲート端子とソース端子との間に耐圧電圧よりも高い電圧が加わることを避けることが可能になる。このとき、定電流電源20bが電源からツェナーダイオードZD2を通してグランドに流れる電流を制限する。電源からトランジスタM3、M5b、M6bを通してnMOSトランジスタM2のゲート端子に流れる電流をnMOSトランジスタM6bが制限する。

(もっと読む)

モード選択回路

【課題】設定に用いる端子数を減らすことができ、且つ回路規模の小型化を図りうるモード選択回路を提供する。

【解決手段】モード選択回路1には、通電経路5の電流状態に応じた定電流を複数の電流比較経路7に流す定電流生成回路9が設けられている。更に、複数の電流比較経路7に対してそれぞれ比較電流を流す定電流源40が設けられ、定電流源40によって複数の電流比較経路7に流される比較電流が互いに異なる電流値となるように構成されている。更に、電流比較部20は、それら複数の各比較電流と前記定電流とを比較したときの比較結果をモード判定部30に出力しており、モード判定部30はこのような比較結果を得ることで通電経路5の状態に応じたモードに設定している。

(もっと読む)

半導体装置

【課題】簡単な回路構成により誤動作を防止できる半導体装置を得る。

【解決手段】パワー素子Q1とパワー素子Q2がトーテムポール接続されている。駆動回路1が入力信号INに応じてパワー素子Q2を駆動し、駆動回路2が入力信号/INに応じてパワー素子Q1を駆動する。駆動回路1は、電源に接続された高圧端子と、低圧端子とを有する。抵抗R1の一端がパワー素子Q2のエミッタに接続され、抵抗R1の他端が駆動回路1の低圧端子に接続されている。スイッチング素子Q3が駆動回路1の高圧端子と抵抗R1の一端との間に接続されている。スイッチング素子Q3は入力信号INに応じてオン・オフする。入力信号INがオフ信号の場合に、駆動回路1は低圧端子の電圧VGNDをパワー素子Q2のゲートに供給してパワー素子Q2はオフする。入力信号INがオフ信号の場合に、スイッチング素子Q3はオンする。

(もっと読む)

半導体装置

【課題】スイッチング素子のターンオン直後における、過電流保護回路の誤動作防止と過電流検出遅れ防止とを両立させる。

【解決手段】半導体装置は、スイッチング素子1のセンス端子に流れるセンス電流を電圧(センス電圧)に変換するセンス抵抗4と、センス電圧が閾値を越えたときにスイッチング素子1の保護動作を行う過電流保護回路3とを備える。過電流保護回路3は、上記閾値を、第1基準電圧VREF1またはそれよりも低い第2基準電圧VREF2に切り替えることができる。過電流保護回路3は、スイッチング素子1が定常状態のときは、上記閾値を第2基準電圧VREF2とし、スイッチング素子1のターンオン直後のミラー期間のときは、上記閾値を第1基準電圧VREF1に設定する。

(もっと読む)

ソレノイドの通電制御装置

【課題】ソレノイドに流れる電流を検出するタイミングと、PWM信号を出力するタイミングとのずれを抑制可能なソレノイドの通電制御装置を提供する。

【解決手段】ソレノイドの通電制御装置100は、ソレノイド50に流れる電流の電流値の取得用の電流取得用タイマ10と、当該電流取得用タイマ10の計数結果に基づいて、ソレノイド50の通電を制御するスイッチング素子51を駆動するPWM信号の1周期内において予め設定された回数だけ電流値を取得する電流値取得部11と、PWM信号の出力用のPWM制御用タイマ20と、1周期内に取得された電流値に基づき、次の1周期にスイッチング素子51に通電する通電時間を設定し、当該設定した通電時間に応じたPWM信号を出力するPWM制御部21と、PWM制御用タイマ20の計時結果に基づき、電流取得用タイマ10の計時値を更新する計時値更新部41と、を備える。

(もっと読む)

過電流保護回路

【課題】過電流検出抵抗の温度特性の影響をキャンセルすることのできる過電流保護回路を提供する。

【解決手段】基準抵抗と第1定電流源との第1接続点には、該第1接続点の電位の温度特性が、過電流検出抵抗の電圧検出端子の電位の温度特性と等しくなるように、第1接続点に対して正の温度特性を有する第2定電流を供給する第2定電流源が接続されている。第2定電流源は、負の温度特性を有する第3定電流を供給する第3定電流源と、温度特性を有さない第4定電流を供給する第4定電流源と、第3定電流源に対して直列接続された第1トランジスタと、第4定電流源に対して直列接続された第2トランジスタと、により構成された第1カレントミラー回路と、第4定電流源と第2トランジスタとの接続点に接続され、第1接続点に第2定電流を供給するための電流経路と、を有する。第3定電流源は、過電流検出抵抗と同じ基板に形成されている。

(もっと読む)

過電流検出装置

【課題】駆動に適した推奨値からずれた電気的特性を持つ負荷を駆動した場合でも誤検出を極力防止する。

【解決手段】しきい値生成回路11は、抵抗13、14にしきい値生成電流ITH、ITLを流してしきい値電圧VTH、VTLを生成し、コンパレータ12はシャント抵抗7の検出電圧Vaと比較して過電流検出信号Scを得る。しきい値補正回路17は、平均負荷電流、負荷電流の交流変化分、電源電圧VBが大きいほどしきい値電圧VTH、VTLを増やし、負荷4の温度が低いほどしきい値電圧VTH、VTLを増やす。

(もっと読む)

パワーモジュール

【課題】制御電源電圧が低下した場合においても、半導体デバイスの熱破壊を防止することが可能なパワーモジュールを提供する。

【解決手段】パワーモジュール100は、半導体デバイス10のIGBT11を駆動する駆動回路20と、IGBT11のコレクタ電流がトリップレベルに達したときにIGBT11の保護動作を行う保護回路30と、駆動回路20に供給される制御電源電圧VDを検出する制御電源電圧検出回路40とを備える。保護回路30は、制御電源電圧VDが所定値よりも低くなると、センス抵抗を抵抗R1から抵抗R1,R2の直列回路に切り替えることで、トリップレベルを下げる。

(もっと読む)

電流制御装置

【課題】電流制御装置をマイクロコントローラと電流制御用ICを用いて構成するとともに、多チャンネル化した際にも小型で低コストな電流制御装置を提供することにある。

【解決手段】電流制御装置は、電流制御用半導体素子1と、電流制御用半導体素子1に、負荷を駆動するためのPWMパルスを出力し、電流制御用半導体素子から、ハイサイド電流検出回路6とローサイド電流検出回路7の出力を入力するマイクロコントローラ12とを有する。電流制御用半導体素子1の出力合成回路8は、PWMパルスに同期して、1つの信号線上にハイサイド電流検出回路6の出力と、ローサイド電流検出回路7の出力を切り替えて、マイクロコントローラ12に出力する。

(もっと読む)

ハイサイドスイッチ回路

【課題】所定のスイッチング動作を実行しつつ、破壊耐性を向上することが可能なハイサイドスイッチ回路を提供する。

【解決手段】電源電圧をスイッチングして出力するハイサイドスイッチ回路100は、電源電圧Vccが印加される電源端子1に一端が接続された第1の出力MOSトランジスタM1、第1の出力MOSトランジスタの他端に一端が接続され電圧出力端子2に他端が接続された第2の出力MOSトランジスタM2、第1の出力MOSトランジスタに流れる電流の検出信号を出力する電流検出回路6、第1の出力MOSトランジスタが線形領域で動作するように第1の出力MOSトランジスタのゲートに第1の制御電圧を印加する第1のゲートドライバ4、第2の出力MOSトランジスタが線形領域で動作するように第2の出力MOSトランジスタのゲートに第2の制御電圧を印加する第2のゲートドライバ5を備える。

(もっと読む)

負荷駆動装置

【課題】負荷電流検出手段により検出された負荷電流を用いてリーク故障を確実に検出する。

【解決手段】駆動回路33a、33bの出力端子Ta2、Tb2から電源線6に至る還流経路内にシャント抵抗9a、9bを接続し、電源線5と給電分岐点Nsとの間に共通のシャント抵抗24を接続する。駆動制御回路32は、MOSFET7a、7bをPWM駆動し、負荷電流検出回路12a、12bから負荷電流Ia、Ibを入力し、総電流検出回路23から総電流Isを入力する。検出負荷電流Ia、Ibに対しそれぞれ対応するPWM駆動信号のオフ駆動期間をマスク処理し、マスク処理した検出負荷電流Iam、Ibmを加算した加算電流Icmと検出総電流Isとを比較する。両者が等しい場合には正常状態と判定し、異なる場合にはショート故障またはリーク故障が生じたと判定する。

(もっと読む)

ゲート駆動回路

【課題】双方向に導通可能なスイッチング素子に逆電流が流れた場合であってもスイッチング素子の損失を低減させることができるゲート駆動回路。

【解決手段】双方向に導通可能なスイッチング素子SWと、スイッチング素子のオンオフを制御する制御部11と、スイッチング素子に流れる電流を検出する電流検出部12と、電流検出部によってスイッチング素子に逆方向の電流が流れたことが検出された時に、制御部によるオンオフの制御とは独立に、スイッチング素子をオン制御するゲート駆動部13とを備える。

(もっと読む)

トランジスタ回路、双方向スイッチ回路、ダイオード回路及びトランジスタ回路の製造方法

【課題】トランジスタのゲートへの電流を防ぐ。

【解決手段】ノーマリーオン型の第1トランジスタと、ドレインが、第1トランジスタのソースと接続され、第1トランジスタとカスコード接続されたノーマリーオフ型の第2トランジスタと、第2トランジスタのソースと第1トランジスタのゲートとの間に設けられた、第2トランジスタのソースから第1トランジスタのゲートへと流れる電流を抑制する第1電流抑制部とを備えるトランジスタ回路を提供する。

(もっと読む)

低Vf逆導通FET回路及び多機能FET回路用IC

【課題】内部ダイオード又は外部ダイオードを使用せずに、逆方向へ導通可能なMOS−FET回路を提供すること。

【解決手段】MOS−FET(10)と、このMOS−FET(10)のドレインをマイナス入力に接続し、ソースをプラス入力に接続したオペアンプ(15)と、このオペアンプ(15)の出力を一方の入力とし、ゲート端子(14)を他方の入力とした第一OR回路(17)とからなり、前記第一OR回路(17)の出力を前記MOS−FET(10)のゲートに接続した。

(もっと読む)

1 - 20 / 552

[ Back to top ]