Fターム[5J055FX37]の内容

電子的スイッチ (55,123) | 制御、帰還信号の発生 (8,841) | 最初に動作する検出回路の素子、回路 (2,393) | FET、BiTrの閾値を利用 (731)

Fターム[5J055FX37]に分類される特許

101 - 120 / 731

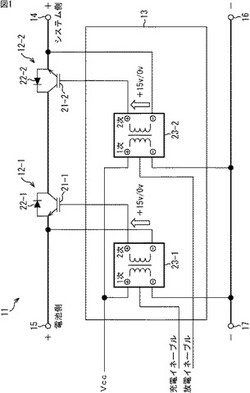

電気回路、充電制御装置、充電システム、および制御方法

【課題】より簡易的な構成で半導体スイッチを駆動する回路を実現する。

【解決手段】充放電切替回路11は、プラス側の電力線に挿入される半導体スイッチ12−1および12−2と、入力側の端子に入力される入力電圧を、所定の出力電圧に変換して出力側の端子から出力する絶縁型DCDCコンバータ23−1および23−2とを備える。そして、絶縁型DCDCコンバータ23−1および23−2の出力側のマイナス端子がプラス側の電力線に接続され、絶縁型DCDCコンバータ23−1および23−2の出力側のプラス端子が半導体スイッチ12−1および12−2の開閉を制御する端子に接続される。本発明は、例えば、高電圧の電源の充放電を制御する回路に適用できる。

(もっと読む)

CMOS回路及び半導体装置

【課題】しきい電圧VTが小さくてもリーク電流が小さく、また高速にかつ小さな電圧振幅で動作するCMOS回路さらには半導体装置を提供することである。

【解決手段】ゲートとソースを等しい電圧にしたときにドレインとソース間に実質的にサブスレショルド電流が流れるようなMOST(M)を含む出力段回路において、その非活性時には、前記MOST(M)のゲートとソース間を逆バイアスするように該MOST(M)のゲートに電圧を印加する。すなわち、MOST(M)がpチャンネル型の場合にはp型のソースに比べて高い電圧をゲートに印加し、また、MOST(M)がnチャンネル型の場合にはn型のソースに比べて低い電圧をゲートに印加する。活性時には、入力電圧に応じて該逆バイアス状態を保持するかあるいは順バイアス状態に制御する。

(もっと読む)

半導体遮断回路

【課題】スナバ回路や波形発生回路等を用いずに、回路面積が大型になったり、生産コストを高くなったりするのを抑えることのできる半導体遮断回路を提供する。

【解決手段】制御部11が、短絡や過電流が発生したと判断して半導体遮断器12が電流を遮断するとき、スイッチS3,S4の電気的接続状態をオン状態に切り替え、ゲート電圧調整部の抵抗値を低い状態にして、半導体遮断器12のゲート電圧VGを半導体遮断器12が遮断を開始する閾値電圧V1よりもやや高いレベルまで短時間で一気に減少させる。次に、スイッチS1,S3の電気的接続状態をオフ状態に切り替え、ゲート電圧調整部の抵抗値を高い状態にして、半導体遮断器12のゲート電圧VGを半導体遮断器12が遮断を完了する閾値電圧V2よりもやや低いレベルまで緩やかに減少させる。

(もっと読む)

表示パネルドライバ及びそれを用いた表示装置

【課題】駆動電圧の極性切替(極性反転)が可能な表示パネルドライバの消費電力を低減する表示パネルドライバを提供する。

【解決手段】本発明による表示パネルドライバは、表示パネルの画素に接続された第1データ線及び第2データ線を駆動する出力段として、第1電源範囲で駆動する第1出力段24A及び第4出力段24Bを利用する第1モードと、第1電源範囲よりも広い第2電源範囲で駆動する第2出力段73A及び第3出力段73Bを利用する第2モードとを切替える第1スイッチ回路50と、第2モードの間に、正極性駆動電圧と負極性駆動電圧の出力先となるデータ線6を切替える第2スイッチ回路30とを備える。又、第1出力段24Aは、ウェルが他のNMOSトランジスタから分離され、バックゲートがソースに接続された第1プルダウン出力トランジスタMN18を備える。

(もっと読む)

スイッチ回路装置

【課題】従来技術によるスイッチ回路装置では、ドライバ回路がアンテナ端子とポートとの間に振幅の大きい高周波信号を入力した際に、ドライバ回路内部でリーク電流が発生し、スイッチ回路装置の消費電力が増大する、という問題がある。

【解決手段】ドライバ回路の出力部に、リーク電流抑制回路部を設ける。本発明のスイッチ回路装置によれば、リーク電流抑制回路部が高周波信号の侵入を抑制するので、ドライバ回路は出力状態を保持することが出来て、リーク電流の問題が解決される。

(もっと読む)

半導体装置

【課題】コモンノイズを低減する。

【解決手段】半導体装置10は、直列に接続された半導体スイッチング素子11,12と、正極端子13と、負極端子14と、出力端子15とを具備する半導体モジュール16と、半導体モジュール16に絶縁されたボディ17とを備える。ボディ17と、各端子13,15,14およびデバイスとの間の各浮遊容量C1,C2,C3,C0と、ボディ17の浮遊インダクタンスLbと、コモンノイズの電流経路に応じた角速度ωとに対して、

[1/(ω・C1)<{ω・Lb+1/(ω・C0)}]と、[1/(ω・C3)<{ω・Lb+1/(ω・C0)}]と、(C2<C1)と、(C2<C3)とを満たす。

(もっと読む)

負荷駆動装置

【課題】複数の負荷の駆動状態に応じて、スイッチング損失の低減とノイズの抑制とを図ることができる負荷駆動装置を提供する。

【解決手段】複数の負荷2A〜2Dについて個別に設けられ、半導体スイッチング素子5,6により前記負荷をスイッチング駆動する複数の負荷駆動手段3A〜3Dで、台形波傾き制御プリドライバ7が、NチャネルMOSFET5,6のゲートに対してそれぞれ台形波状のパルス信号を出力する場合に、台形波の立上り及び立下りの傾きを変更可能に構成し、4チャネル駆動の場合は傾きを大きく、1チャネル駆動の場合は台形波の傾きを小さくする。

(もっと読む)

バッファ回路

【課題】TFT特性のばらつきにかかわらず画像ムラがなく、高精細・高解像度の良好な画像を得ることができる半導体表示装置の駆動回路および半導体表示装置を提供する。

【解決手段】半導体表示装置はソース信号線側駆動回路と、ゲイト信号線側駆動回路とを有し、駆動回路はシフトレジスタ回路からのタイミング信号をバッファする複数のインバータ回路を有するバッファ回路を有し、インバータ回路は複数のインバータ回路を並列に接続して構成される。

(もっと読む)

電流制御用半導体素子、およびそれを用いた制御装置

【課題】センス比の温度分布依存性を除去し、センスMOSFETによる電流検出の精度を向上できる電流制御用半導体素子、およびそれを用いた制御装置を提供することにある。

【解決手段】電流制御用半導体素子1は、同一半導体チップ上に、電流を駆動するメインMOSFET7と、メインMOSFET7に並列に接続し、メインMOSFETの電流を分流して電流検出を行うためのセンスMOSFET8とを有する。メインMOSFETは、複数のチャネルを有し、一列に配列されたマルチフィンガーMOSFETを使用して形成される。マルチフィンガーMOSFET7の中心から、最も遠いチャネルまでの距離をLとすると、マルチフィンガーMOSFETの中心から(L/(√3))の位置に最も近いチャネルを、センスMOSFET8のチャネルとして使用する。

(もっと読む)

切替回路及び受信回路

【課題】2つのクロック信号を切り替えて出力する切替回路において、出力信号のデューティ比を、入力されるクロック信号のデューティ比に保つこと。

【解決手段】切替回路100は、制御信号CONTに応じて、入力信号IN1,IN2を切り替えて出力信号OUTとして出力する。具体的には、制御信号CONTが「Lレベル」のときには、クロックドインバーターX2が動作し、信号IN1が信号OUTとして出力され、制御信号CONTが「Hレベル」のときには、クロックドインバーターX4が動作し、信号IN2が信号OUTとして出力される。

(もっと読む)

電流駆動装置

【課題】駆動電圧を駆動回路へ安定的に供給しつつ、部品点数を少なくすることができる電流駆動装置を提供する。

【解決手段】パワートランジスタ3の主端子および制御端子が主端子接続端子13および制御端子接続端子14にそれぞれ接続されることにより、第1の電源4の電圧を所定の目標出力電圧に降圧する3端子レギュレータ10として機能する3端子レギュレータ構成回路12と、第1の電源4より低い電圧を出力する第2の電源6からの電力を用いて、3端子レギュレータ構成回路12がパワートランジスタ3の制御端子に印加する目標出力電圧に対応する制御電圧を設定する電圧設定回路18と、制御端子接続端子14に接続され、第1の電源4から電力が供給されると、3端子レギュレータ構成回路12の出力電圧VOUTが予め定められた電圧VC以下となるようにパワートランジスタ3の制御端子に印加される制御電圧を制御する電圧制限回路19とを備える。

(もっと読む)

電源検知回路

【課題】電源検知回路において、BT劣化によって比較回路のミスマッチが増大することに起因する電源検知信号の精度の劣化を抑制する。

【解決手段】検知用比較回路104は、入力切替信号生成回路112によって、その出力の活性状態と非活性状態との切替時付近では、入力信号102と基準電圧103とを入力して、その両者の比較を行う。一方、前記切替時付近以外では、比較回路非使用時入力電圧110が検知用比較回路104に入力されて、その差動入力が同電位に固定される。従って、BT劣化による電源検知精度の経年劣化が有効に抑制される。

(もっと読む)

半導体スイッチ回路

【課題】低周波帯域において線形性劣化のない半導体スイッチ回路を提供する。

【解決手段】入出力端子間に直列にソースおよびドレインを接続した1又は2以上の電界効果トランジスタと、電界効果トランジスタのゲートに接続した抵抗を備えた半導体スイッチ回路において、電界効果トランジスタのゲート−ドレイン間およびゲート−ソース間に、キャパシタをそれぞれ接続可能とした。

【効果】FETのゲート−ドレイン間およびゲート−ソース間すべてにキャパシタを接続したことにより、従来より低い周波数帯域においてゲート電極に接続する抵抗よりFETのインピーダンスが十分低くなるため、線形性を向上させることが可能となる。

(もっと読む)

モータ制御装置及びバルブタイミング調整装置並びにインバータ回路の通電制御方法

【課題】モータの実回転方向が回転方向指令と逆になった場合に、フリーホイールダイオードにおいて発生する損失を軽減できるモータ制御装置を提供する。

【解決手段】制御回路60は、外部より指令として与えられるモータ4の目標回転方向Dtと、回転角センサSU,SV,SWが出力するセンサ信号に基づき信号生成ブロック72により検出されるモータ4の実回転方向Drとが相違する方向不一致状態を検出すると、120度通電方式から180度通電方式に切り替えてインバータ部76を構成する上段スイッチング素子FU,FV,FWのオン期間を進み位相側に拡げるように制御し、還流電流を上段スイッチング素子FU,FV,FWを介して流す。

(もっと読む)

駆動装置

【課題】駆動回路やトランジスタにおいてばらつきがあっても、PWM駆動信号の駆動デューティ成分が小さい場合にも、上側トランジスタと下側トランジスタのシュート・スルー(貫通状態)を防止する。

【解決手段】入力端子の第2レベルまたは第1レベル信号に応じてスイッチングデバイスの制御端子に駆動電流をシンク出力するシンク回路と、スイッチングデバイスのオフ期間中に制御端子を経て容量性の電流をシンクする電流シンクトランジスタと、入力端子の信号に応じてソース回路の入力駆動信号と、シンク回路あるいは前記シンクトランジスタへの入力駆動信号とを生成するI/F回路と、シンク回路または前記シンクトランジスタへの入力駆動信号をシンク回路かあるいはシンクトランジスタのどちらに入力駆動信号として出力するかを選択するセレクタと、この選択動作を制御するセレクタへの選択信号を受ける入力端子とを備える。

(もっと読む)

半導体集積回路および高周波モジュール

【課題】出力波形のリップルを低減可能な半導体集積回路を提供する。

【解決手段】例えば、高周波スイッチ回路RFSWと、そのオン・オフを制御するスイッチ制御回路SWCTLを備え、SWCTLは、2個のダウンコンバータ回路VGEN1,VGEN2と、レベルシフト回路LS[1]〜LS[4]を備える。各LS[n]は、レベルシフト段LSSG[n]とその後段に接続された出力段OTSG[n]を持ち、RFSWは、OTSG[n]からの制御信号OUT[n]によって制御される。LSSG[n]は、VGEN1からの負の電源電圧(−VSS1)を用いて動作し、OTSG[n]は、VGEN2からの負の電源電圧(−VSS2)を用いて動作する。−VSS1では、LSSG[n]のレベルシフト動作に伴いリップルが生じ得るが、−VSS2ではOTSG[n]の動作がスイッチング動作であるためリップルが生じ難い。

(もっと読む)

ゲート駆動回路

【課題】本発明は、レベルシフト高圧トランジスタのゲートに接続される電源の電圧が高い場合にも低い場合にも弊害なく稼動するゲート駆動回路を提供することを目的とする。

【解決手段】ゲート電圧の波形がパルス信号で制御されるレベルシフト高圧トランジスタと、該レベルシフト高圧トランジスタのゲートと電源を接続する抵抗と、該レベルシフト高圧トランジスタのドレインと接続され、該レベルシフト高圧トランジスタのドレイン電流に応じてゲート駆動信号を出力する高電圧回路と、該レベルシフト高圧トランジスタのソース及びゲートと接続され、該ドレイン電流が増大すると該抵抗を流れる電流を増大させるように構成されたカレントミラー回路と、該電源の電源電圧が低い場合は該抵抗の抵抗値を低減させ、該電源の電源電圧が高い場合は該抵抗の抵抗値を維持する抵抗調整手段とを有する。

(もっと読む)

インバータ回路および表示装置

【課題】より少ない素子数で、さらなる高速化を実現することの可能なインバータ回路、およびこのインバータ回路を備えた表示装置を提供する。

【解決手段】バッファ回路1は、互いに直列に接続されたインバータ回路10およびインバータ回路20を備える。インバータ回路20は、並列関係にあるトランジスタTr21およびトランジスタTr22と、これらのトランジスタTr21,Tr22のゲート電圧Vgの補正を行う閾値補正回路21を有する。閾値補正回路21は、トランジスタTr21のゲートに対して、トランジスタTr21の閾値電圧Vth1(図示せず)またはトランジスタTr21の閾値電圧Vth1に対応する電圧をオフセットとして設定する。閾値補正回路21は、さらに、トランジスタTr22のゲートに対して、トランジスタTr22の閾値電圧Vth2(図示せず)またはトランジスタTr22の閾値電圧Vth2に対応する電圧をオフセットとして設定する。

(もっと読む)

高周波スイッチ回路

【課題】2次高調波歪みの発生を抑制することができる高周波スイッチ回路を提供することである。

【解決手段】本発明にかかる高周波スイッチ回路は、共通端子と第1の端子との間に配置された第1のスイッチ(T11〜T14)と、共通端子と第2の端子との間に配置された第2のスイッチ(T21〜T24)と、を少なくとも備える。第1のスイッチが備える電界効果トランジスタには、第1のスイッチがオフ状態の時に生成される寄生容量を相殺する補償容量(Cdb11〜Cdb14)がドレインとボディとの間、またはソースとボディとの間に形成されている。また、第2のスイッチが備える電界効果トランジスタには、第2のスイッチがオフ状態の時に生成される寄生容量を相殺する補償容量(Cdb21〜Cdb24)が、ドレインとボディとの間、またはソースとボディとの間に形成されている。

(もっと読む)

電子回路、パワーオンリセット回路、集積回路装置及び電子機器

【課題】電源投入時に初期状態を確実に設定できる電子回路、パワーオンリセット回路、集積回路装置及び電子機器等を提供すること。

【解決手段】電子回路は、各回路素子がトランジスターで構成される複数の回路素子XA1〜XB2と、第1の高電位電源電圧VDDが供給され、VDDが所定の電圧レベルになるまでは、低電位電圧レベルに設定され、VDDが所定の電圧レベルを越えると、VDDに追従して電圧レベルが上昇する第2の高電位電源電圧VINTを出力する電源出力回路100とを含む。複数の回路素子のうち、初期状態においてその出力ノードが高電位電圧レベルになる回路素子である第1のグループの回路素子XA1、XA2には、VDDが供給され、初期状態においてその出力ノードが低電位電圧レベルになる回路素子である第2のグループの回路素子XB1、XB2には、VINTが供給される。

(もっと読む)

101 - 120 / 731

[ Back to top ]