Fターム[5J055FX37]の内容

電子的スイッチ (55,123) | 制御、帰還信号の発生 (8,841) | 最初に動作する検出回路の素子、回路 (2,393) | FET、BiTrの閾値を利用 (731)

Fターム[5J055FX37]に分類される特許

121 - 140 / 731

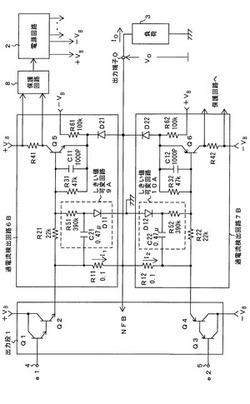

電力増幅器の過電流検出回路及びその方法

【課題】 しきい値を的確に可変して過電流検出の誤作動を防止する。

【解決手段】 過電流検出回路6Bは、Q2のエミッタと出力端子Oの間の電流検出抵抗R11の両端間に抵抗R21、R31が接続されている。R31の両端が過電流検出トランジスタQ5のベース−エミッタ間に接続されており、出力端子Oと−VB の間にダイオードD21、抵抗R61が接続されており、D21のカソードがQ5のエミッタと接続されている。R21とR31の接続点とグランド間には抵抗R51とD11が接続されており、R51とD11の接続点とQ2のエミッタの間にコンデンサC21が接続されている。R51、D11、C21のしきい値可変回路9Aは出力電圧の大きさが大きくなるとしきい値を大きくし、出力電圧の大きさが小さくなるとしきい値を小さくするが、C21とD11により、出力電圧の大きさが増加するときはしきい値を早く増大変化させ、減少するときはしきい値をゆっくり減少変化させる。

(もっと読む)

誘導素子駆動回路

【課題】 低消費電流化と高速動作化のトレードオフを克服し、貫通電流防止と駆動効率向上を可能にする誘導素子駆動回路を提供する。

【解決手段】 PWM信号を入力する入力端子11と、ソースが第1の電源端子に接続されたPMOS高耐圧トランジスタM0と、ソースがGNDに接続され、ドレインがトランジスタM0のドレインに接続されたNMOS高耐圧トランジスタM1と、トランジスタM0のドレイン及びトランジスタM1のドレインの接続点に設けられ、誘導素子L1を駆動する信号を出力する出力端子12と、出力端子12の電位変化を検出してトランジスタM0をオフした後にトランジスタM1をオンする電圧検出回路9とを備える。この電圧検出回路9は、出力端子12の端子電圧VLXがLowになったことを検知し、Highを出力してトランジスタM1をオンするので、貫通電流を防止する。

(もっと読む)

半導体装置及び制御方法

【課題】メモリの出力バッファの平均電流値を低減し、消費電流を抑制すること。

【解決手段】本発明に係る半導体装置は、メモリリードアドレスDの連続性を判定し、判定結果Hを出力するアドレス連続性判定回路23と、判定結果Hに基づいて、メモリリードアドレスDに対応するリードデータを出力するメモリの出力バッファ22の駆動能力を制御する駆動能力切り替え制御回路24と、CPUの要求リードアドレスAに対応するリードデータが当該CPUへ到達するまでの期間に、CPU要求リードアドレスAに連続する予想アドレスを生成するアドレス生成部12と、予想アドレスに対応するリードデータを格納するプリロードバッファ14を備える。

(もっと読む)

電子回路

【課題】

内部電源電圧を遮断するパワーダウンモードへの移行を誤動作無く確実に実行するパワーダウンモードの移行シーケンスを備えた電子回路を提供する。

【解決手段】

電源電圧から降圧してシステム電圧を発生するシステム電圧発生回路10と、システム電圧を供給されて動作する第1の内部回路30と、電源電圧を供給されて動作する入出力回路24と、第1の内部回路30からの信号を入力し、電源電圧の電圧レベルに変換するレベルシフタ23と、システム電圧発生回路10を制御する制御回路40とを備え、制御回路40は起動信号P4を入力し、この起動信号に所定の遅延時間を与えた短絡制御信号P5を出力する遅延回路100を有し、起動信号はレベルシフタ23を非活性又は活性として制御し、短絡制御信号はシステム電圧発生回路10を停止状態又は動作状態として制御する構成とした。

(もっと読む)

高電圧スイッチング回路

【課題】高電圧処理能力および改善された実行能力を有する効率的なスイッチング回路を提供する。

【解決手段】第1および第2のIII−V族トランジスタを有し、第2のIII−V族トランジスタは、第1のIII−V族トランジスタよりも大きな降伏電圧を有する。さらに、第1のIII−V族トランジスタと並列に配置されるシリコンダイオードを有し、この並列配置は、第2のIII−V族トランジスタと直列に接続、効率的な3端子デバイスであり、第1端子は第2のIII−V族トランジスタのゲート、第1のIII−V族トランジスタのソースおよびシリコンダイオードのアノードに結合する。第2端子は第1のIII−V族トランジスタのゲートと結合し、第3端子は第2III−V族トランジスタのドレインと結合する。

(もっと読む)

電子スイッチ装置

【課題】商用交流電源から電子機器への電力供給をオン又はオフするために使用者が操作するスイッチ部品として、各国の安全規格を満たさないスイッチ部品であっても自在に利用可能な電子スイッチ装置を提供すること。

【解決手段】本発明によれば、発振手段が、操作スイッチにより二次側コイルの両端が開放されると発振し、該二次側コイルの両端が短絡されると、一次側コイルのインダクタ値の減少に起因し発振が停止するので、二次側コイルの両端の状態が発振手段からの出力の出力態様に反映される。よって、かかる出力態様に基づくことにより、電力供給路の導通又は遮断を操作スイッチの操作状態に応じて行うことができる。ここで、操作スイッチが接続される二次側コイルは、一次側コイルに対して絶縁されているので、各国の安全規格を満たさないスイッチ部品を操作スイッチとして使用したとしても、操作スイッチを操作する使用者の安全を確保できる。

(もっと読む)

半導体スイッチ集積回路

【課題】チップやパッケージのサイズやコストの増加を抑えるとともに、安定動作が実現できる半導体スイッチ集積回路を提供する。

【解決手段】制御電圧印加端子と、オン状態のFETとオフ状態のFETの接続点との間に、抵抗素子を接続する。さらにオフ状態のFETのソース端子とドレイン端子との間に抵抗素子を接続する。その結果、制御電圧以外に外部からGND電位を含めたDC電圧を加えなくとも、半導体スイッチ集積回路を構成するFETのドレイン端子、ソース端子に安定に電圧を供給することができ、オフ状態のFETのソース端子およびドレイン端子の電位を所定の電位に設定することができる。

(もっと読む)

パワーオンリセット回路

【課題】誤動作を起こす可能性があった。

【解決手段】電源投入初期もしくは電源電圧降下時にリセット信号を発生し初期化するパワーオンリセット回路であって、電源電圧に応じた電圧を分圧した第1の比較電圧を生成する第1の比較電圧生成部と、電源電圧に応じた第1の電圧を出力する基準電圧生成部と、電源電圧端子と第1のノードとの間に接続され、制御端子に前記第1の電圧を入力するデプレッション型の第1のトランジスタと、前記第1のノードと接地端子との間に接続され、制御端子が前記第1のノードに接続されるエンハンスメント型の第2のトランジスタと、を備え、前記第1のノードの電位に応じた電圧を第2の比較電圧として生成する第2の比較電圧生成部と、前記第1、第2の比較電圧との比較結果に応じてリセット信号を出力する比較器と、を有するパワーオンリセット回路。

(もっと読む)

送受信モジュール

【課題】大きなパルス幅を有する大電力の高周波信号が入力された場合であっても、リミタ回路および受信回路の増幅器が破壊されることを抑制することができる送受信モジュールを提供する。

【解決手段】アンテナ11と、リミタ回路16および受信系電力増幅器17を備えた受信回路14と、送信系電力増幅器20を備えた送信回路15とが、送受信切替スイッチ13により接続され、アンテナ11と送受信切替スイッチ13の間に設けられた検波回路12により、送受信切替スイッチ13を制御する制御信号を生成する。送受信切替スイッチ13は、制御信号が入力されない状態ではアンテナ11と受信回路14とを導通させ、制御信号が入力されるとアンテナ11と送信回路15とを導通させる。制御信号は、送受信切替スイッチ13に信号が入力された時から、リミタ回路16の熱時定数よりも短い時間までの間に送受信切替スイッチ13に入力される。

(もっと読む)

半導体集積回路装置及び送受信システム

【課題】入力信号に対する増幅器の出力信号の利得特性を線形化するために必要な回路の面積を低減できる半導体集積回路装置及び送受信システムを提供する。

【解決手段】半導体集積回路装置は、切り替え可能な複数の第1の利得特性を有し、入力信号に対して前記第1の利得特性を切り替えて中間信号を生成し、第2の利得特性を有する回路に前記中間信号を出力する線形化回路を備え、前記線形化回路は、少なくとも1つの第1の整流素子を有し、前記入力信号を線形化する線形化器と、前記第1の整流素子と逆極性の複数の第2の整流素子と、制御信号に基づき前記複数の第2の整流素子のうち少なくとも1つを選択する第1の切り替え部とを有し、前記線形化器に並列に接続され、前記線形化器による前記入力信号の線形化を抑制する線形化抑制器とを備える。

(もっと読む)

信号保持回路およびこれを使用したシステム保護装置

【課題】電源電圧が低下したときに信号保持回路での信号保持を確実に解除する。

【解決手段】出力端子toを複数の入力端子のうちの1つtbに接続し、残りの外部入力端子taに外部信号が入力される論理和回路14と、該論理和回路14の出力端子に接続された単一パルスを生成するパルス生成回路15とを備え、前記論理和回路14の前記外部入力端子tbにハイレベルのパルス信号が入力されたときに、当該論理和回路14の出力をハイレベルに保持する信号保持回路13であって、前記論理和回路14の前記出力端子toと前記入力端子tbとの間に、電源電圧低下時に当該論理和回路14によるハイレベル保持状態を解除する電圧を高めるダイオードDを介挿した。

(もっと読む)

コンパレータ回路

【課題】低消費電力動作を実現しつつ信号処理に向けた論理判定時間を格段に削減することができる。

【解決手段】入力電圧と参照電圧とを比較して論理判定結果の出力電圧を発生して差動増幅器を含むコンパレータ回路において、微小電流であるバイアス電流を発生して差動増幅器に供給する電流源と、差動増幅器からの差動電圧を反転して反転信号を出力する第1のインバータ回路と、電流源のバイアス電流を検出し、第1のインバータ回路の貫通電流を検出し、検出したバイアス電流及び検出した貫通電流に基づいて、差動増幅器が論理判定を行わない期間はバイアス電流で差動増幅器を動作させる一方、差動増幅器が論理判定する期間はバイアス電流を増加させてなる適応バイアス電流を用いて差動増幅器を動作させるように適応バイアス電流制御を行うための適応バイアス電流を発生して差動増幅器に供給する適応バイアス電流生成回路とを備える。

(もっと読む)

半導体装置及び電子機器

【課題】消費電力を低減することができる半導体装置及びそれを用いた電子機器を提供す

ることを課題とする。

【解決手段】本発明の半導体装置は、高電位電源から第1の電位が供給され、低電位電源

から第2の電位が供給され、入力ノードに第1の信号が入力されると、出力ノードから第

2の信号を出力する。本発明の半導体装置は、第2の信号の電位差を、第1の電位と第2

の電位の電位差よりも小さくすることにより、配線の充電と放電に伴う消費電力を低減す

ることができる。

(もっと読む)

半導体集積回路

【課題】 ゲート酸化膜の信頼性を維持しながら、待機時のリーク電流を抑制でき、回路面積の増加を最小限にでき、欠陥を確実に検出することができる半導体集積回路を実現する。

【解決手段】 論理回路10と電源電圧Vddの供給端子との間にスイッチング回路20を設ける。動作時に、スイッチング回路20のトランジスタMP0のゲートに0Vの電圧を印加し、チャネル領域に電源電圧Vddと同じかまたは僅かに低いバイアス電圧VBを印加することで、トランジスタMP0のしきい値電圧を低くし、その電流駆動能力を大きくする。待機時にトランジスタMP0のゲートに電源電圧Vddと同じ電圧を印加し、ソースに電源電圧より低い電圧を印可し、チャネル領域に電源電圧Vddと同じかまたはそれより高いバルクバイアス電圧VBを印加し、トランジスタMP0のドレイン電流を最少化することにより、論理回路10の電流経路を遮断し、リーク電流の発生を抑制する。

(もっと読む)

バッファリング回路および増幅回路

【課題】 回路のダイナミックレンジを圧迫しないと共に、チップサイズの増大を抑制することができるバッファリング回路及び増幅回路を提供する。

【解決手段】 入力端子及び出力端子を有するバッファリング回路でドレインが第1電圧ラインに接続され、ソースが前記出力端子に接続され、ゲートが前記入力端子に接続された第1プルアップドライバと、ソースが前記出力端子に接続され、ゲートが前記入力端子に接続された第2プルアップドライバと、前記第2プルアップドライバのドレインに定電流を供給する定電流回路と、前記出力端子と第2電圧ラインとの間に配置されたプルダウンドライバとを備え、前記プルダウンドライバは、前記定電流回路の定電流から前記第2プルアップドライバに流れる電流を減じた差電流に基づいた電流を流すように構成されている。

(もっと読む)

スイッチングレギュレータ

【課題】 小型・低雑音のスイッチングレギュレータを提供する。

【解決手段】 導通、遮断の2状態が交互に切り替わる複数のトランジスタで構成されたスイッチングレギュレータの出力段と、その出力段トランジスタを各々個別に駆動するための駆動回路から構成され、当該駆動回路は、各々出力段トランジスタにおける遮断から導通状態への遷移時間が、導通から遮断状態への遷移時間に比べて長くなるように立ち上がり、立ち下がり時の駆動能力をアンバランスに設定され、各々の遷移時間は、出力信号の電位があらかじめ設定された電位に達したことを判定して変化させることを特徴とするスイッチングレギュレータとして構成される。

(もっと読む)

半導体装置

【課題】消費電力の増加を招くことなくオフの状態を実現することのできる半導体装置を提供する。

【解決手段】ゲートに電圧が印加されていない状態でオン状態であるパワー素子と、パワー素子のゲートに第1の電圧を印加するためのスイッチング用の電界効果トランジスタと、パワー素子のゲートに第1の電圧より低い電圧を印加するためのスイッチング用の電界効果トランジスタと、を有し、上記スイッチング用の電界効果トランジスタはオフ電流が小さい半導体装置である。

(もっと読む)

出力ドライバ回路

【課題】通信速度の高速化に加えて、消費電力の低減や、あるいは伝送波形品質の向上が図れる出力ドライバ回路を提供する。

【解決手段】例えば、正極および負極出力ノード(TXP,TXN)を電圧で駆動する電圧信号生成回路ブロックVSG_BKと、データ入力信号DIN_P,DIN_Nの遷移を受けてパルス信号を生成するパルス信号生成回路PGEN1,PGEN2と、当該パルス信号のパルス幅の期間でTXP,TXNを電流で駆動する電流信号生成回路ブロックISG_BKp1,ISG_BKn1を備える。電流信号生成回路ブロックは、TXP,TXNの寄生容量(Cp1,Cp2)を高速に充電すると共に、パルス幅に応じたプリエンファシスを行う。VSG_BKは、TXP,TXNにおける定常状態の電圧レベルを定めると共に、TXP,TXNをインピーダンスZ0で終端する。

(もっと読む)

貫通電流防止回路および車両用モータ駆動回路

【課題】半導体スイッチング素子の実動作に応じて貫通電流を防止することで動作信頼性を向上する。

【解決手段】下アーム側のIGBT(BTU2)に流れる通電電流を測定するときに、トランジスタQ2がIGBT(BTU2)の通電電流を直列抵抗R1およびR2の印加電圧によってセンシングする。そしてトランジスタQ3がトランジスタQ2の出力信号をレベルシフトする。そして、トランジスタQ4がトランジスタQ3のエミッタ電圧に応じてIGBT(BTU1)を強制的にオフ制御する。

(もっと読む)

アンテナスイッチおよびそれを内蔵した高周波モジュール

【課題】アンテナスイッチの高調波歪特性を改善する。

【解決手段】アンテナスイッチのアンテナ端子2にアンテナが接続され、第1信号端子3とアンテナ端子2の間に第1転送スイッチ100が接続され、第2信号端子4とアンテナ端子2の間に第2転送スイッチ101が接続され、第1信号端子3と接地電位の間に第1シャントスイッチ102が接続され、第2信号端子4と接地電位の間に第2シャントスイッチ103が接続される。負電圧生成回路104の入力10は第1信号端子3に供給される送信信号に応答可能とされ、出力端子11に生成される負電圧に応答して第2転送スイッチ101と第1シャントスイッチ102とはオフ状態に制御される。

(もっと読む)

121 - 140 / 731

[ Back to top ]