Fターム[5J055FX37]の内容

電子的スイッチ (55,123) | 制御、帰還信号の発生 (8,841) | 最初に動作する検出回路の素子、回路 (2,393) | FET、BiTrの閾値を利用 (731)

Fターム[5J055FX37]に分類される特許

141 - 160 / 731

電気光学装置、シフトレジスタ回路および半導体装置

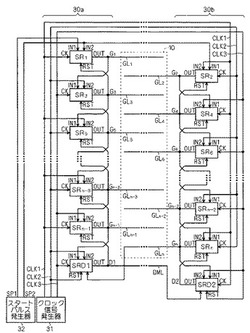

【課題】ゲート線駆動回路の領域を効率よく利用できると共に、ゲート線選択信号の立ち上がり速度の低下(立ち上がり遅延)を防止できる電気光学装置、並びに、それに適した単一導電型のトランジスタで構成されたシフトレジスタ回路を提供する。

【解決手段】ゲート線駆動回路30は、複数のゲート線GLの奇数行を駆動する奇数ドライバ30aと、偶数行を駆動する偶数ドライバ30bとから成る。奇数および偶数ドライバ30a,30bの単位シフトレジスタSRの各々は、2行前の選択信号Gk-2を受け、その2水平期間遅れて自己の選択信号Gkを活性化させる。偶数ドライバ30bのスタートパルスSP1は、奇数ドライバ30aのスタートパルスSP2よりも1水平期間だけ位相が遅れている。

(もっと読む)

レベルシフト回路

【課題】消費電力低下および速度向上が可能なレベルシフト回路を提供する。

【解決手段】レベルシフト回路2は、第1入力端子11、第2入力端子12、第1出力端子21、第2出力端子22、第1PMOSトランジスタ31、第2PMOSトランジスタ32、第1NMOSトランジスタ41、第2NMOSトランジスタ42、第1ブートストラップ回路51および第2ブートストラップ回路52を備える。第1ブートストラップ回路51は、第1充電用スイッチ511,第1転送用スイッチ512,第1容量部513および第1インバータ回路514を含む。第2ブートストラップ回路52は、第2充電用スイッチ521,第2転送用スイッチ522,第2容量部523および第2インバータ回路524を含む。

(もっと読む)

半導体スイッチ及び無線機器

【課題】オフ歪みを低減した半導体スイッチを提供する。

【解決手段】負の第1の電位を生成する電圧生成回路と、外部から入力される端子切替信号に応じて前記第1の電位を変化させる電圧制御回路と、電源電圧または電源電圧よりも高い正の第2の電位と前記第1の電位とが供給され、前記端子切替信号を入力し前記端子切替信号に基づいて前記第1の電位及び前記第2の電位の少なくとも一方を出力する駆動回路と、SOI基板に設けられ、前記駆動回路の出力により端子間の接続を切り替えるスイッチ部と、を備えたことを特徴とする半導体スイッチが提供される。

(もっと読む)

PLD回路、集積回路装置及び電子機器

【課題】消費電力を低減できるPLD回路、集積回路装置及び電子機器等を提供すること。

【解決手段】PLD回路は、各トランジスター列が直列接続されたプログラマブルな複数のトランジスターを有する第1〜第m(mは2以上の整数)のトランジスター列TA1〜TAmを含む。第1〜第mのトランジスター列TA1〜TAmの一端に第1の非直流電源VS1が供給される。第1〜第mのトランジスター列TA1〜TAmの各トランジスター列は、複数の入力信号XP(X1P〜XiP)、XN(X1N〜XiN)によってオン・オフされる。第1の非直流電源VS1の電圧により規定される第1のホールド期間に、第1〜第mのトランジスター列TA1〜TAmの他端のノードである第1〜第mのノードNA1〜NAmの電圧レベルを各々出力する。

(もっと読む)

出力バッファ回路

【課題】出力遅延を短縮できる出力バッファ回路を提供する。

【解決手段】信号PenがLレベルからHレベルに切り替わり信号NenがHレベルからLレベルに切り替わった直後において、定電流源Is1が追従しきれずまた切り替わっていない場合には、ノードPは未だHレベルのままであるので、ノードOUTはLレベルのままである。この状態で、切り替え前にHレベルのノードNに接続されていたノードAは、切り替えによりHレベルのノードPへ接続される。これと同時に、インバータinv3の出力部がHレベルからLレベルに切り替わっているので、キャパシタC2を介して、ノードAもHレベルからLレベルに切り替えられる。このとき、ノードPの電位はノードAと等しくなるまで引き下げられ、Lレベルへ遷移する。

(もっと読む)

送信ドライバ回路

【課題】フリーホイールダイオードを用いることなく、より低い電圧のアンダーシュートでも低減できる送信ドライバ回路を提供する。

【解決手段】PチャネルMOSFET22のドレインをグランドに接続して、NチャネルMOSFET21,PチャネルMOSFET22のソースをそれぞれ信号線3H,3Lに接続する。第1データ電圧設定部41は、信号出力部がハイレベル信号を出力すると、ゲート21G,22G間の電位差を(2・R1・Iref)にする電圧信号を設定し、第2データ電圧設定部42は、信号出力部がロウレベル信号を出力すると、ゲート21G,22G間の電位差をゼロにする電圧信号を設定する。これらの作用により、伝送線路3を構成する信号線3H,3L間の電圧を変化させて差動信号を伝送する。

(もっと読む)

プリエンファシス機能を含む出力回路と半導体装置

【課題】プリエンファシス機能を有する出力回路において、デエンファシス時における差動出力信号のコモンモード電圧のプリエンファシス時のコモンモード電圧からの変動を抑制する。

【解決手段】入力信号とその相補信号とを差動入力して差動出力し、差動出力信号のうち高電位側の出力信号にデエンファシスをかける際に、当該デエンファシス電流を供給するトランジスタ(N3、N4)に流れる電流を絞る回路(N5、N6、R3)を備え、デエンファシス時の前記出力信号のハイレベルの前記出力信号のプリエンファシス時のハイレベルからの変化量を縮減させ、デエンファシス時の前記差動出力信号のコモンモード電圧をプリエンファシス時のコモンモード電圧に近づける。

(もっと読む)

駆動回路および表示装置

【課題】出力電圧の立ち上がるタイミングのばらつきを低減することの可能な駆動回路、およびこの駆動回路を備えた表示装置を提供する。

【解決手段】バッファ回路1は、互いに直列に接続されたインバータ回路10およびインバータ回路20を備えている。インバータ回路20は、3つのトランジスタTr21,Tr22,Tr23を有している。そのうちの2つのトランジスタTr21,Tr22は、デュアルゲート型のトランジスタである。これらトランジスタTr21,Tr22のバックゲートの電圧を調整することにより、トランジスタTr21,Tr22の閾値電圧を調整することができる。

(もっと読む)

駆動回路および表示装置

【課題】出力電圧の立ち上がるタイミングのばらつきを低減することの可能な駆動回路、およびこの駆動回路を備えた表示装置を提供する。

【解決手段】バッファ回路1は、互いに直列に接続されたインバータ回路10およびインバータ回路20を備えている。インバータ回路20は、インバータとして機能する回路(3つのトランジスタTr21,Tr22,Tr23)と、トランジスタTr21,Tr22のゲート電圧Vgの補正を行う閾値補正回路21とを有している。閾値補正回路21は、トランジスタTr21,Tr22のゲートに対して、トランジスタTr21,Tr22の閾値電圧Vth1,Vth2をオフセットとして設定するようになっている。

(もっと読む)

半導体装置

【課題】終端抵抗のオンオフの切り替え時に外部端子にインピーダンスの急激な変化が生じることを低減する。

【解決手段】外部端子(図2のDQに相当)と、外部端子に接続され、出力信号を外部端子に出力可能とする出力回路(図2の21に相当)と、外部端子に終端抵抗をオンオフ可能に接続する終端回路(図2の22に相当)と、終端抵抗がオフ状態又はオン状態のいずれか一方の状態から他方の状態に変化するまでの時間を、データ出力時に出力信号が一方の論理レベルから他方の論理レベルへ変化するまでの時間以上となるように制御する第1のスルーレート制御回路(図2の23aに相当)と、を備える。

(もっと読む)

半導体装置

【課題】入力信号のHレベルまたはLレベルを正しく検知できる半導体装置を提供する。

【解決手段】半導体装置100は、閾値調整信号に基づいて論理閾値電位を調整可能な入力バッファ(入力CMOS回路11)と、入力バッファの入力と出力とが結線されたレプリカ(レプリカ12)と、予め設定された基準電位(ノードNdHの電位)を発生する基準電位発生回路(基準電位発生回路13)と、レプリカ(レプリカ12)の出力電位(ノードNdRの電位)と基準電位(ノードNdHの電位)とを比較し、閾値調整信号(閾値調整信号CTRL)を入力バッファ(入力CMOS回路11)とレプリカ(レプリカ12)とに出力する比較回路(比較回路14)と、を備える。

(もっと読む)

出力バッファ回路、入力バッファ回路、及び入出力バッファ回路

【課題】スルーレートを適切に調整可能なバッファ回路を提供する。

【解決手段】

CMOS出力バッファ回路は、バッファ回路Buffer[1]〜[4]を備えている。各バッファ回路は、電源電圧端子又は接地端子と出力端子との間にトランジスタPO及びNOを有している。各バッファ回路中の複数個のトランジスタPO及びNOは、外部からの制御信号に従い選択的に動作可能な状態とされる。各バッファ回路中の3個のトランジスタPOは、所定のサイズ比を有するように形成されている。

(もっと読む)

データ出力回路

【課題】プリエンファシスまたはディエンファシスのためのドライバの追加がなくても、プリエンファシスまたはディエンファシス動作を行えるデータ出力回路を提供すること。

【解決手段】インピーダンスコードによって各々オン・オフされ、出力ノードにデータを出力する複数の駆動手段311、312を備え、前記インピーダンスコードが、前記駆動手段をターンオンさせる値を有する第1のグループと前記駆動手段をオフさせる値を有する第2のグループとに分けられ、プリエンファシス期間の間には、前記第2のグループによる制御を受ける駆動手段の全部または一部がターンオンされる。

(もっと読む)

半導体記憶装置および昇圧回路

【課題】回路面積の削減しつつ、消費電流やピーク電流の増大を抑制することが可能な半導体記憶装置を提供する。

【解決手段】昇圧回路は、第1ないし第4の整流素子と、第1ないし第4のMOSトランジスタと、第1ないし第4のキャパシタと、スイッチ回路と、を備える。スイッチ回路は、第1のMOSトランジスタの他端と第3の整流素子の一端との間の第1の接続点、および、第2のMOSトランジスタの他端と第4の整流素子の一端との間の第2の接続点に接続された低レベル端子と、第3のMOSトランジスタの他端、および、第4のMOSトランジスタの他端に接続された高レベル端子と、を有し、低レベル端子の電圧または高レベル端子の電圧を切り換えて、出力端子に出力するスイッチ回路と、を含む。

(もっと読む)

論理回路及び半導体装置

【課題】クロックゲーティングを行う論理回路において、待機電力を低減すること又は誤動作を抑制すること。

【解決手段】論理回路は、クロック信号が供給されない期間に渡って、ソース端子及びドレイン端子に電位差が存在する状態でオフするトランジスタを有する。該トランジスタのチャネル形成領域は、水素濃度が低減された酸化物半導体によって構成される。具体的には、当該酸化物半導体の水素濃度は、5×1019(atoms/cm3)以下である。そのため、当該トランジスタのリーク電流を低減することができる。その結果、当該論理回路の待機電力を低減すること及び誤動作を抑制することができる。

(もっと読む)

集積回路装置及び電子機器

【課題】通常動作モード、低消費電力動作モードでの省電力化等を図れる集積回路装置及び電子機器等の提供。

【解決手段】集積回路装置は、外部電源電圧VDDEを受けて、外部電源電圧VDDEを降圧した第1の電源電圧VDDAを出力する第1のレギュレーターRG1と、外部電源電圧VDDEを受けて、外部電源電圧VDDEを降圧した第2の電源電圧VDDBを出力する第2のレギュレーターRG2と、第1の電源電圧VDDAが供給され、通常動作モード及び低消費電力動作モードにおいて動作する第1のロジック回路LG1と、第2の電源電圧VDDBが供給され、通常動作モードにおいて動作し、低消費電力動作モードでは非動作になる第2のロジック回路LG2を含む。

(もっと読む)

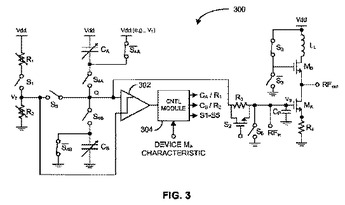

アクティブデバイスをバイアスするシステム及び方法

アクティブデバイスに対するバイアス電圧を発生する装置が開示され、第1の電圧源と、第1の電圧源に応答してチャージを発生するように適応されたキャパシティブエレメントと、アクティブデバイスに対するバイアス電圧を発生するためにチャージを供給するように適応された第1のスイッチングエレメントとを備える。本装置は、アクティブデバイスの1以上の特性に基づいてキャパシティブエレメントをコントロールするように適応されコントローラを備えるかもしれない。コントローラは、リファレンス電圧に基づいて、すなわちアクティブデバイスの1以上の特性に基づいて前記キャパシティブエレメントのキャパシタンスをコントロールかもしれない。  (もっと読む)

(もっと読む)

スイッチトキャパシタ型積分器

【課題】待機電流を抑制することによって、低消費電力のスイッチトキャパシタ型積分器を実現する。

【解決手段】φ1において入力信号の電荷をサンプリングするサンプルキャパシタC1と、φ2においてサンプルキャパシタC1の電荷を仮想ノード4を介して累積する蓄積キャパシタC2と、蓄積キャパシタC2にサンプルキャパシタC1の電荷を供給する主トランジスタMP1,MN1と、主トランジスタMP1,MN1のゲート端子と仮想接地ノード4の間に挿入された校正キャパシタC3,C4と、φ1において校正キャパシタC3,C4に対して、仮想ノード4が基準電位Vcmにあるときの主トランジスタMP1,MN1のゲート・ソース間電圧が略閾値電圧となる電位差が生じるように電荷を供給する校正装置12と、を有する。

(もっと読む)

高耐圧スイッチ回路およびそれを用いた半導体集積回路装置

【課題】 双方向スイッチにおいて、ドレイン電圧またはドレイン-ソース間電圧に基づいて、上記スイッチのゲート-ソース間電圧を制御する手段と、上記制御手段を介して、上記スイッチのゲート端子に電圧を印加するスイッチドライバとを備えている双方向スイッチを提供する。

【解決手段】 双方向スイッチであるメインスイッチと、上記メインスイッチのゲート-ソース間電圧を、上記メインスイッチのドレイン電圧、ソース電圧に基づいて制御する手段と、上記制御手段を介して上記メインスイッチのゲート端子に電圧を印加するスイッチドライバとを備えている双方向スイッチを構成する。

(もっと読む)

高周波半導体スイッチ

【課題】トランジスタのドレインとバックゲート間およびソースとバックゲート間に生じる電流の漏洩を抑圧し、高周波信号の透過損失の増大を抑制できる高周波半導体スイッチを得る。

【解決手段】高周波半導体スイッチは、接地部を有するSi等の真性半導体基板と、この真性半導体基板に形成され、バックゲート端子を有するMOSトランジスタと、真性半導体基板の接地部およびMOSトランジスタのバックゲート端子間に設けられたインダクタとを備える。

(もっと読む)

141 - 160 / 731

[ Back to top ]