Fターム[5J055GX05]の内容

Fターム[5J055GX05]に分類される特許

121 - 140 / 525

高電圧差動信号方式のためのドライバ回路

高電圧差動信号方式のためのドライバ回路(200)。この回路は、入力に応答して第1の出力で第1の正の遷移を生成する第1の正のドライバ(205A)を含む。この回路は更に、第1の正のドライバに結合され、電流の生成を可能にする第1の電流要素(210A)を含む。更に、この回路は、第1の電流要素(210A)に結合され、第1の電流要素に起因して、入力及び電流に応答して、第1の正の遷移の速度に類似する速度で、第2の出力で第1の負の遷移を生成する、第1の負のドライバ(215A)を含む。  (もっと読む)

(もっと読む)

プリエンファシス機能を含む出力回路と半導体装置

【課題】プリエンファシス機能を有する出力回路において、デエンファシス時における差動出力信号のコモンモード電圧のプリエンファシス時のコモンモード電圧からの変動を抑制する。

【解決手段】入力信号とその相補信号とを差動入力して差動出力し、差動出力信号のうち高電位側の出力信号にデエンファシスをかける際に、当該デエンファシス電流を供給するトランジスタ(N3、N4)に流れる電流を絞る回路(N5、N6、R3)を備え、デエンファシス時の前記出力信号のハイレベルの前記出力信号のプリエンファシス時のハイレベルからの変化量を縮減させ、デエンファシス時の前記差動出力信号のコモンモード電圧をプリエンファシス時のコモンモード電圧に近づける。

(もっと読む)

送信ドライバ回路

【課題】フリーホイールダイオードを用いることなく、より低い電圧のアンダーシュートでも低減できる送信ドライバ回路を提供する。

【解決手段】PチャネルMOSFET22のドレインをグランドに接続して、NチャネルMOSFET21,PチャネルMOSFET22のソースをそれぞれ信号線3H,3Lに接続する。第1データ電圧設定部41は、信号出力部がハイレベル信号を出力すると、ゲート21G,22G間の電位差を(2・R1・Iref)にする電圧信号を設定し、第2データ電圧設定部42は、信号出力部がロウレベル信号を出力すると、ゲート21G,22G間の電位差をゼロにする電圧信号を設定する。これらの作用により、伝送線路3を構成する信号線3H,3L間の電圧を変化させて差動信号を伝送する。

(もっと読む)

半導体装置

【課題】終端抵抗のオンオフの切り替え時に外部端子にインピーダンスの急激な変化が生じることを低減する。

【解決手段】外部端子(図2のDQに相当)と、外部端子に接続され、出力信号を外部端子に出力可能とする出力回路(図2の21に相当)と、外部端子に終端抵抗をオンオフ可能に接続する終端回路(図2の22に相当)と、終端抵抗がオフ状態又はオン状態のいずれか一方の状態から他方の状態に変化するまでの時間を、データ出力時に出力信号が一方の論理レベルから他方の論理レベルへ変化するまでの時間以上となるように制御する第1のスルーレート制御回路(図2の23aに相当)と、を備える。

(もっと読む)

駆動回路および表示装置

【課題】出力電圧の立ち上がるタイミングのばらつきを低減することの可能な駆動回路、およびこの駆動回路を備えた表示装置を提供する。

【解決手段】バッファ回路1は、互いに直列に接続されたインバータ回路10およびインバータ回路20を備えている。インバータ回路20は、インバータとして機能する回路(3つのトランジスタTr21,Tr22,Tr23)と、トランジスタTr21,Tr22のゲート電圧Vgの補正を行う閾値補正回路21とを有している。閾値補正回路21は、トランジスタTr21,Tr22のゲートに対して、トランジスタTr21,Tr22の閾値電圧Vth1,Vth2をオフセットとして設定するようになっている。

(もっと読む)

駆動回路および表示装置

【課題】出力電圧の立ち上がるタイミングのばらつきを低減することの可能な駆動回路、およびこの駆動回路を備えた表示装置を提供する。

【解決手段】バッファ回路1は、互いに直列に接続されたインバータ回路10およびインバータ回路20を備えている。インバータ回路20は、3つのトランジスタTr21,Tr22,Tr23を有している。そのうちの2つのトランジスタTr21,Tr22は、デュアルゲート型のトランジスタである。これらトランジスタTr21,Tr22のバックゲートの電圧を調整することにより、トランジスタTr21,Tr22の閾値電圧を調整することができる。

(もっと読む)

液晶表示装置のソースドライバー回路

【課題】 本発明は、液晶表示装置のソースドライバー集積素子でパワードロップに対する復帰時間を縮める技術を提供する。

【解決手段】本発明によってソースドライバーに適用されるガンマバッファー回路では、差動増幅部と電流ミラー部のモストランジスターらを直接連結しないでダイオード結合型モストランジスターを通じて連結した。これによって、出力端のモストランジスターのゲートの動作範囲がダイオード結合型モストランジスターのドレッシーホールド電圧程度減るようになる。これによって電源端子電圧ドロップ後復帰時間及び接地端子電圧バウンシング後に復帰時間が減って、入力トランジスターのマッチング特性が改善されて、これによってランダムオフセットが低減される。

(もっと読む)

半導体集積回路装置

【課題】電源投入手順によらずに安定した動作を行う入出力回路の制御を、回路規模の増大を抑え、チューニングが不要なデジタル回路のみで実現する集積回路を提供する。

【解決手段】信号発生器113で生成した信号を、レベルシフト回路111で電源電圧Vcc2の信号振幅へ変換する。次にVcc2の信号振幅に変換したものを、もう一度レベルシフト回路112で内部電源電圧Vcc1の信号振幅へ変換して、フィードバック信号を生成する。比較器114で信号発生器113が生成したオリジナルの信号と、2つのレベルシフトを経て生成された、フィードバック信号とを論理的に比較し、一致しない場合にはVcc2の電源が遮断されていると見なして、入出力回路115での不定伝播を防止するように制御を行う。

(もっと読む)

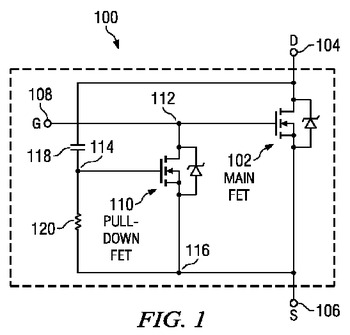

ゲート・プルダウンを備えたMOSFET

スイッチングタイプのDC−DCパワー・コンバータのMOSFETメインスイッチ・トランジスタ(102)のドレインとゲートとの間にプルダウンMOSFET(110)が結合される。プルダウンMOSFET(110)のゲートは、キャパシタ118によってメインスイッチ・トランジスタ(102)のドレインに結合され、抵抗(120)によってメインスイッチ・トランジスタ(102)のソースに接続される。プルダウンMOSFET(110)は、メインスイッチ・トランジスタ(102)にわたる電圧降下への容量性結合によって動作され、ミラー効果によるメインスイッチ・トランジスタ(102)の意図しないターンオンを避ける又は低減するため、メインスイッチ・トランジスタ(102)のゲートをそのソース電位にまたはその近辺に保持するために用いられ得る。

(もっと読む)

(もっと読む)

ポジションスイッチの出力判定装置

【課題】長期間使用した場合でも、常に適正なスイッチ位置の判定を行うことができるポジションスイッチの出力判定装置を提供する。

【解決手段】本発明に係わるポジションスイッチの出力判定装置(20)は、少なくとも2つの位置間の変位により、第1電圧レベルまたは当該第1電圧レベルと異なる第2電圧レベルとを出力するポジションスイッチ(10)の出力判定装置であって、前記第1電圧レベルと前記第2電圧レベルとの間での切り替りを判定するための判定電圧レベルを記憶する記憶手段(21)と、前記ポジションスイッチから出力された電圧レベルが、前記判定電圧レベルを跨いで変化したときに、当該変化の前後で検出した前記第1電圧レベルと前記第2電圧レベルとの中間の電圧レベルを検出し、当該検出した電圧レベルを前記判定電圧レベルとして前記記憶手段の記憶内容を更新する制御手段(22)と、を備える。

(もっと読む)

電圧駆動型半導体素子のゲート駆動装置

【課題】電圧駆動型半導体素子のスイッチング時に配線インダクタンスにより発生する素子間のサージ電圧を低減するためにゲート駆動回路のゲート抵抗を大きくすると、スイッチングの動作遅れ時間が長くなる。

【解決手段】電圧駆動型半導体素子のターンオフ時において、オフ信号によりゲート電荷を放電させる時にはオフ信号印加の初めに第1の抵抗体とコンデンサにより早く放電させることにより、スイッチング動作時間遅れの増加を防止し、その後第2の抵抗体に切換ることによりゲート電流を減少させることによって、素子間のサージ電圧を低減する。また、電圧駆動型半導体素子のターンオン時には、ダイオードが導通状態となることにより、該第1の抵抗体と該第2の抵抗体が並列構成となるので、前記第1の抵抗体の抵抗値により、早くゲート電荷を充電することができる。

(もっと読む)

パワーオンクリア回路

【課題】電源電圧の立ち上がり状態の影響を受けないクリア信号を生成、出力するパワーオンクリア回路を提供する。

【課題の解決手段】パワーオンクリア回路は、電源の投入によってパルスを発生するパルス発生回路1と、発生したパルスを遅延して出力する遅延回路5と、遅延されたパルスが入力する縦続接続した2段のインバータ6,7と、遅延回路5の前段側の出力が入力する入力端子と1段目のインバータ6の出力が入力する入力端子とを有するNOR回路8とを備え、NOR回路8の出力を電源電圧の立ち上がり状態の影響を受けない第1のクリア信号とし、インバータ7の出力を電源電圧の立ち上がり状態に応じた第2のクリア信号とするものである。

(もっと読む)

半導体装置および電子機器

【課題】パワー半導体素子を駆動するためのドライバを低コストで得ることが可能な半導体装置およびそれを備えた電子機器を提供する。

【解決手段】半導体装置101は、ハイサイド駆動部62からの駆動信号を受ける第1のスイッチング機能部と、ローサイド駆動部64からの駆動信号を受ける制御電極とを有する第2のスイッチング機能部とを備え、ハイサイド駆動部62は、ノーマリーオン型の電界効果トランジスタを含み、スイッチング制御信号の基準電圧を出力ノードの電位へシフトした駆動信号を出力し、第1のスイッチング機能部はノーマリーオン型の第1の電界効果トランジスタTr1を含み、第2のスイッチング機能部はノーマリーオン型の第2の電界効果トランジスタTr2を含み、ハイサイド駆動部62および第1の電界効果トランジスタTr1は第1の半導体チップ71に含まれている。

(もっと読む)

レベルシフタ誤動作防止回路

【課題】本発明は、レベルシフタ誤動作防止回路に係り、レベルシフタの誤動作を、信号伝達の過大な遅延と消費電流の増大とを招くことなく防止することにある。

【解決手段】伝達すべき信号に応じて駆動されるN型トランジスタ30と、N型トランジスタ30の出力に応じて駆動されるP型トランジスタ32と、P型トランジスタ32を駆動するために設けられるプルアップ抵抗34と、を有する、基準電圧が互いに異なる2つの回路系の間で信号伝達を行うレベルシフタ16の誤動作を防止する回路において、2つの回路系の基準電圧が相対変位した際、N型トランジスタ30に存在する寄生容量36へプルアップ抵抗34を介して充電電流が供給される前に、その寄生容量36へ充電電流を供給する急速充電手段を設ける。

(もっと読む)

半導体装置及び半導体装置の電源制御方法

【課題】1つの回路ブロックに対して設けた複数の電源スイッチを順次オンさせていく構成において、スイッチオンのタイミングを適切に制御可能な半導体装置を提供する。

【解決手段】半導体装置は、内部回路と、内部回路へ電流を供給する複数の並列な経路にそれぞれ設けられ、導通状態又は非導通状態に制御される複数の電源スイッチと、内部回路への電源を遮断する指示又は電源を供給する指示を行なう命令部と、内部回路に電源スイッチを介して供給される電流が定常状態であるか否かを検知して検知結果を出力する変動検知部と、命令部の電源供給指示に応答して、複数の電源スイッチを順次導通状態にして内部回路への電流供給量を増やしていく際に、複数の電源スイッチを導通させるタイミングを検知結果に応じて制御する論理回路とを含む。

(もっと読む)

時定数回路、スイッチ回路、DC/DCコンバータ及び表示装置

【課題】単調に減衰するだけの出力電圧特性に比べて、急峻に減衰した後に緩やかに減衰する出力電圧特性が得られる時定数回路等を提供する。

【解決手段】時定数回路10は、抵抗素子111と容量素子121との並列回路131,…が第一の端子14と第二の端子15との間に複数直列に接続されて成る直並列回路16と、第二の端子15に接続された第三の端子17と第四の端子18との間に接続された分圧用抵抗素子19と、を備えている。並列回路131は抵抗素子111と容量素子121とから成り、並列回路132は抵抗素子112と容量素子122とから成り、・・・、並列回路13nは抵抗素子11nと容量素子12nとから成る。nは、並列回路131〜13nの数であり、2以上の整数である。

(もっと読む)

半導体装置、及びその制御方法

【課題】発振回路と信号入出力回路とを切り替えて使用可能な半導体装置、及びその制御方法を提供することである。

【解決手段】本発明にかかる半導体装置は、発振素子1が接続可能な第1及び第2の外部接続端子2、3と、反転増幅器4と、反転増幅器の出力側と入力側との間に接続されたフィードバック抵抗5と、反転増幅器4の入力側に接続されたカップリング容量11に印加されるバイアスを安定化するバイアス安定化回路6と、第1の信号入出力部7と、第2の信号入出力部8と、を備える。半導体装置を発振回路として使用する場合は、反転増幅器4およびバイアス安定化回路6を動作状態とし、第1及び第2の信号入出力部7、8を停止状態とする。信号入出力回路として使用する場合は、反転増幅器4およびバイアス安定化回路6を停止状態とし、第1及び第2の信号入出力部7、8を動作状態とする。

(もっと読む)

駆動装置、及び表示装置

【課題】並列接続された複数の出力アンプ回路において所望の駆動能力を実現することができる駆動装置、及び表示装置を提供すること。

【解決手段】本発明に係る駆動装置(ソースドライバ1)は、並列接続された複数の出力アンプ回路10と、複数の出力アンプ回路10に、バイアス電圧供給源25からバイアス電圧を供給するバイアス配線(幹バイアス配線22)と、複数の出力アンプ回路10に、電源電圧供給源35から電源電圧を供給する電源配線31と、複数の出力アンプ回路10に供給される電源電圧とバイアス電圧との差が所望となるように、バイアス電圧にオフセット電圧を重畳する補正手段(バッファ26)とを備えた。

(もっと読む)

半導体集積回路およびそれを備えた電子機器およびその制御方法

【課題】より少ない消費電力で信号処理装置の動作モードを安定的に変更する。

【解決手段】制御回路(30)は、レギュレータ回路(10)の出力電圧(Vout)で動作する信号処理装置(20)に対する動作モードの変更要求(MODE)を受け、レギュレータ回路(10)の出力電圧(Vout)を変更し、その後、変更要求(MODE)に従って信号処理装置(20)の動作モードを変更する。

(もっと読む)

電源検出回路

【課題】 電源検出回路の誤動作を抑制すること

【解決手段】 パワーダウン検出回路10及びパワーオン検出回路12を初期化するための初期化信号nrsetxを生成するスタータ回路18において、パワーオンが検出されている第1期間に電源電圧を中間ノードへ供給する切替回路を有する。第1の期間において第1電源電圧から中間ノードへ電源電圧を供給することにより、スタータ回路の出力を安定させることができる。その結果、電源検出回路の誤動作を抑制することができる。

(もっと読む)

121 - 140 / 525

[ Back to top ]