Fターム[5J055GX05]の内容

Fターム[5J055GX05]に分類される特許

101 - 120 / 525

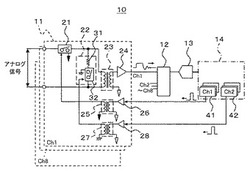

アナログ入力装置

【課題】信号トランスの励磁エネルギーを速やかに消費させ、入力信号のバックスイングおよび各チャンネルの読み込み時間を短縮して、高速化可能なアナログ入力装置を得る。

【解決手段】外部から入力されたアナログ信号を絶縁する信号トランス23と、信号トランス23の1次側に接続され、オンオフ制御されることでアナログ信号をパルス形状に変化させる第1スイッチ素子21と、信号トランス23の1次側に、信号トランス23の巻線端子と並列に接続され、互いに直列に接続された抵抗素子31および第2スイッチ素子32からなるリセット回路22と、第1スイッチ素子21に対して、オンオフ制御のための第1制御パルス信号を出力するとともに、第1制御パルス信号を出力した後に、第2スイッチ素子32に対して、信号トランス23の巻線に励磁されたエネルギーを消費するための第2制御パルス信号を出力する第1、第2シーケンス手段41、42とを備える。

(もっと読む)

可変ゲート電界効果トランジスタ(FET)及びこのFETを備える電気電子装置

【課題】可変ゲート電界効果トランジスタ(FET)及びこのFETを備える電気電子装置を提供する。

【解決手段】熱によるFETのソース及びドレイン間の電流減少の問題を効果的に解決し、またFETの温度を低めることができる可変ゲートFET及びこのFETを備える電気電子装置を提供し、可変ゲートFETは、FETと、FETの表面または発熱部分に取り付けられ、回路的には、FETのゲート端子に連結されておりゲート端子の電圧を変化させるゲート制御素子と、を備え、FETの温度が所定温度以上に上昇しているときに、ゲート制御素子が、ゲート端子の電圧を変化させて、FETのソース及びドレイン間のチャンネル電流を制御する。

(もっと読む)

容量性負荷駆動回路

【課題】容量性負荷の静電容量と回路抵抗値とから決定される回路時定数が変化することによって生じる容量性負荷の充電速度または放電速度の変化を防止し、所望の駆動波形を得ることが可能な容量性負荷駆動回路を提供する。

【解決手段】容量性負荷駆動回路は、容量性負荷である複数の駆動素子と、複数のコンデンサーと、前記複数のコンデンサーに電力を供給する電源と、前記複数のコンデンサーと前記複数の駆動素子間の接続を切替える切替え手段と、前記切替え手段を制御する制御手段と、を有し、前記制御手段は、前記複数の駆動素子に対して印加される電荷容量の予測値に基づいて、前記切替え手段の接続状態を維持することを特徴とする。

(もっと読む)

インバータ回路および表示装置

【課題】消費電力を抑えつつ、トランジスタの閾値電圧のばらつきに起因する出力電圧のばらつきを抑えることの可能なインバータ回路、およびこのインバータ回路を備えた表示装置を提供する。

【解決手段】6Tr3Cで構成されるインバータ回路において、入力端子IN2に、入力端子IN1に入力されるパルス信号の位相よりも進んだ位相のパルス信号が印加される。これにより、入力端子IN1の電圧がハイからローに変化する際に、トランジスタT5のゲート−ソース間電圧から、トランジスタT5の閾値電圧の影響が取り除かれるので、その後にトランジスタT5がオンしてトランジスタT5に電流が流れたときに、その電流値Idsからも、トランジスタT5の閾値電圧の影響が取り除かれる。

(もっと読む)

半導体装置及び制御方法

【課題】メモリの出力バッファの平均電流値を低減し、消費電流を抑制すること。

【解決手段】本発明に係る半導体装置は、メモリリードアドレスDの連続性を判定し、判定結果Hを出力するアドレス連続性判定回路23と、判定結果Hに基づいて、メモリリードアドレスDに対応するリードデータを出力するメモリの出力バッファ22の駆動能力を制御する駆動能力切り替え制御回路24と、CPUの要求リードアドレスAに対応するリードデータが当該CPUへ到達するまでの期間に、CPU要求リードアドレスAに連続する予想アドレスを生成するアドレス生成部12と、予想アドレスに対応するリードデータを格納するプリロードバッファ14を備える。

(もっと読む)

電子回路

【課題】

内部電源電圧を遮断するパワーダウンモードへの移行を誤動作無く確実に実行するパワーダウンモードの移行シーケンスを備えた電子回路を提供する。

【解決手段】

電源電圧から降圧してシステム電圧を発生するシステム電圧発生回路10と、システム電圧を供給されて動作する第1の内部回路30と、電源電圧を供給されて動作する入出力回路24と、第1の内部回路30からの信号を入力し、電源電圧の電圧レベルに変換するレベルシフタ23と、システム電圧発生回路10を制御する制御回路40とを備え、制御回路40は起動信号P4を入力し、この起動信号に所定の遅延時間を与えた短絡制御信号P5を出力する遅延回路100を有し、起動信号はレベルシフタ23を非活性又は活性として制御し、短絡制御信号はシステム電圧発生回路10を停止状態又は動作状態として制御する構成とした。

(もっと読む)

電子スイッチ装置

【課題】商用交流電源から電子機器への電力供給をオン又はオフするために使用者が操作するスイッチ部品として、各国の安全規格を満たさないスイッチ部品であっても自在に利用可能な電子スイッチ装置を提供すること。

【解決手段】本発明によれば、発振手段が、操作スイッチにより二次側コイルの両端が開放されると発振し、該二次側コイルの両端が短絡されると、一次側コイルのインダクタ値の減少に起因し発振が停止するので、二次側コイルの両端の状態が発振手段からの出力の出力態様に反映される。よって、かかる出力態様に基づくことにより、電力供給路の導通又は遮断を操作スイッチの操作状態に応じて行うことができる。ここで、操作スイッチが接続される二次側コイルは、一次側コイルに対して絶縁されているので、各国の安全規格を満たさないスイッチ部品を操作スイッチとして使用したとしても、操作スイッチを操作する使用者の安全を確保できる。

(もっと読む)

電源供給装置

【課題】GNDレベルの入力信号を入力する入力回路を備える場合であっても接地端子がオープン状態にあるときにスイッチング用トランジスタ素子をオフ状態に保持すること。

【解決手段】電源供給装置1は、電源2と負荷3との間に接続されたスイッチング用トランジスタ素子Fと、スイッチング用トランジスタ素子Fをオン/オフすることによって電源2から負荷3への電力供給を制御する駆動回路4と、電源2からの電力を利用して駆動される周辺回路6と、スイッチング用トランジスタ素子Fのゲート端子とソース端子との間に接続された電流駆動型の補償トランジスタユニット5と、接地電圧を供給する接地ユニット8とを備える。補償トランジスタユニット5は、周辺回路6と接地ユニット8を介して電源2から所定値以上の電流が供給された場合、スイッチング用トランジスタ素子Fのゲート端子とソース端子との間をショートする。

(もっと読む)

半導体スイッチ回路

【課題】 切替時間の短縮と消費電流の低減を図ることができる半導体スイッチ回路を提供する。

【解決手段】 外部からの経路切替信号の状態が変化した直後から予め設定された時間だけ、レベルシフト短絡スイッチ回路でレベルシフトしない高電圧でスイッチ回路を駆動し、一定時間経過後はレベルシフト短絡スイッチ回路を開放させることによりレベルシフト回路を経由させ、電圧降下させた電圧でスイッチ回路を駆動させる。

(もっと読む)

信号保持回路およびこれを使用したシステム保護装置

【課題】電源電圧が低下したときに信号保持回路での信号保持を確実に解除する。

【解決手段】出力端子toを複数の入力端子のうちの1つtbに接続し、残りの外部入力端子taに外部信号が入力される論理和回路14と、該論理和回路14の出力端子に接続された単一パルスを生成するパルス生成回路15とを備え、前記論理和回路14の前記外部入力端子tbにハイレベルのパルス信号が入力されたときに、当該論理和回路14の出力をハイレベルに保持する信号保持回路13であって、前記論理和回路14の前記出力端子toと前記入力端子tbとの間に、電源電圧低下時に当該論理和回路14によるハイレベル保持状態を解除する電圧を高めるダイオードDを介挿した。

(もっと読む)

スイッチングレギュレータ

【課題】 小型・低雑音のスイッチングレギュレータを提供する。

【解決手段】 導通、遮断の2状態が交互に切り替わる複数のトランジスタで構成されたスイッチングレギュレータの出力段と、その出力段トランジスタを各々個別に駆動するための駆動回路から構成され、当該駆動回路は、各々出力段トランジスタにおける遮断から導通状態への遷移時間が、導通から遮断状態への遷移時間に比べて長くなるように立ち上がり、立ち下がり時の駆動能力をアンバランスに設定され、各々の遷移時間は、出力信号の電位があらかじめ設定された電位に達したことを判定して変化させることを特徴とするスイッチングレギュレータとして構成される。

(もっと読む)

バッファリング回路および増幅回路

【課題】 回路のダイナミックレンジを圧迫しないと共に、チップサイズの増大を抑制することができるバッファリング回路及び増幅回路を提供する。

【解決手段】 入力端子及び出力端子を有するバッファリング回路でドレインが第1電圧ラインに接続され、ソースが前記出力端子に接続され、ゲートが前記入力端子に接続された第1プルアップドライバと、ソースが前記出力端子に接続され、ゲートが前記入力端子に接続された第2プルアップドライバと、前記第2プルアップドライバのドレインに定電流を供給する定電流回路と、前記出力端子と第2電圧ラインとの間に配置されたプルダウンドライバとを備え、前記プルダウンドライバは、前記定電流回路の定電流から前記第2プルアップドライバに流れる電流を減じた差電流に基づいた電流を流すように構成されている。

(もっと読む)

過電流保護装置及び過電流保護システム

【課題】同一の電源に接続された複数の過電流保護装置どうしで、リトライ動作を実行するタイミングに時間差を持たせることが可能な過電流保護装置、及び過電流保護システムを提供する。

【解決手段】IC回路51-1のFET(Q1)をオンとした際に、バッテリ電圧VBAが閾値電圧以下となった場合には、各IC回路のFET(Q1)を全てオフとし、更に、FET(Q1)のオンからバッテリ電圧VBAが閾値電圧以下となるまでの時間を計時する。この時間が400μsec未満であれば、カウント値Nをインクリメントする。その後、ランダムに設定された待機時間Tpが経過した後、再度FET(Q1)をオンとする動作を繰り返し、カウント値Nが7に達した時点で、IC回路51-1のFET(Q1)をオフ状態に保持する。従って、デッドショートの発生している負荷駆動用の回路のみを確実に停止させ、それ以外の負荷駆動用の回路の駆動を継続させることができる。

(もっと読む)

半導体装置

【課題】同一電源系統に接続された複数の主バッファの動作台数の変化により生じる半導体装置の出力のばらつきを抑制すること。

【解決手段】本発明の一態様に係る半導体装置は、入力されるデータに応じて複数の信号線を駆動する、複数の主バッファを備える主バッファ回路2と、主バッファと同数のダミーバッファを備えるダミーバッファ回路5と、主バッファ回路2及びダミーバッファ回路5に接続された電源と、主バッファ回路2が接続された主バッファ配線と、ダミーバッファ回路5に接続され、主バッファ配線と略同一の負荷を有するダミーバッファ配線と、主バッファ回路の複数の主バッファのスイッチング状況を検知するスイッチング検出回路3と、スイッチング検知結果に基づいて、ダミーバッファのスイッチング数を制御するダミーバッファスイッチング回路4とを備える。

(もっと読む)

適応標本化装置および適応標本化プログラム

【課題】入力信号のフレームを標本化する場合に、入力信号の性質に応じた不等間隔で標本化を行う技術を提供する。

【解決手段】適応標本化装置1Aは、フレーム記憶手段10と、フレームに対して、標本点数を減らした複数の異なる標本化間隔で標本化して縮小信号とし、この縮小信号群を出力する階層化信号縮小手段20と、この各縮小信号を入力信号と同じ標本化間隔に戻して、フレームとの誤差をブロックごとに定量化し誤差信号として出力する階層化誤差演算手段30と、フレームの各ブロックに対して適用する標本化間隔の割り当て方である標本化パターンを複数記憶する標本化パターンデータベース50と、各誤差信号と、標本化パターンとに基づき、誤差を最適化する標本化パターンを探索する最適化手段70と、この最適化手段が求めた標本化パターンに基づき、入力信号のフレームを標本化し、出力信号として出力する標本選択配置手段80と、を備える。

(もっと読む)

電子回路

【課題】

内部電源回路からの内部電源電圧が安定状態となり、レベルシフタの入力が適正となった後に、レベルシフタを活性化させるパワーダウンモードの復帰シーケンスを備えた電子回路を提供する。

【解決手段】

電源電圧からシステム電圧を発生するシステム電圧発生回路10と、システム電圧を供給されて動作する内部回路30と、入出力回路24と、内部回路からの信号を入力し、電源電圧の電圧レベルに変換し入出力回路へ出力するレベルシフタ23と、レベルシフタを制御する制御回路40とを備え、システム電圧発生回路10が停止状態から動作状態へ移行するとき、制御回路は内部回路が動作状態であることを判定する第1の判定手段41と、システム電圧が所定値に達したか、または所定値に収束したかを判定する第2の判定手段42とを備え、双方の判定手段の結果に基づいてレベルシフタを活性化する構成とした。

(もっと読む)

負荷駆動制御装置

【課題】消費電力を抑えつつ、高輝度で安定した駆動を得るとともに駆動制御回路全体の寿命を向上させる。

【解決手段】負荷20に接続される駆動制御部10を備え、駆動制御部10は、負荷20の定格電流値IFと、パルス駆動したときの絶対最大定格電流値Imaxから予め設定されたピーク電流値Ipに基づいてパルス幅変調することで、負荷20のオン期間を規定した第1のオン/オフ周期による第1駆動パルスP1を生成し、第1のオン/オフ周期のオン期間の中でさらにスイッチングさせることで、パルスの最大振幅がIpとなるように、第2のオン/オフ周期による第2駆動パルスP2を生成する定電流パルス駆動部14とを備え、第2駆動パルスP2によって駆動された電流を前記負荷20に印加することによって、負荷20を連続的に駆動させるとともに、充放電制御部15のキャパシタンスC1を信頼性寿命の高いセラミックコンデンサーを使用した。

(もっと読む)

レベルシフト回路

【課題】消費電力低下および速度向上が可能なレベルシフト回路を提供する。

【解決手段】レベルシフト回路2は、第1入力端子11、第2入力端子12、第1出力端子21、第2出力端子22、第1PMOSトランジスタ31、第2PMOSトランジスタ32、第1NMOSトランジスタ41、第2NMOSトランジスタ42、第1ブートストラップ回路51および第2ブートストラップ回路52を備える。第1ブートストラップ回路51は、第1充電用スイッチ511,第1転送用スイッチ512,第1容量部513および第1インバータ回路514を含む。第2ブートストラップ回路52は、第2充電用スイッチ521,第2転送用スイッチ522,第2容量部523および第2インバータ回路524を含む。

(もっと読む)

PLD回路、集積回路装置及び電子機器

【課題】消費電力を低減できるPLD回路、集積回路装置及び電子機器等を提供すること。

【解決手段】PLD回路は、各トランジスター列が直列接続されたプログラマブルな複数のトランジスターを有する第1〜第m(mは2以上の整数)のトランジスター列TA1〜TAmを含む。第1〜第mのトランジスター列TA1〜TAmの一端に第1の非直流電源VS1が供給される。第1〜第mのトランジスター列TA1〜TAmの各トランジスター列は、複数の入力信号XP(X1P〜XiP)、XN(X1N〜XiN)によってオン・オフされる。第1の非直流電源VS1の電圧により規定される第1のホールド期間に、第1〜第mのトランジスター列TA1〜TAmの他端のノードである第1〜第mのノードNA1〜NAmの電圧レベルを各々出力する。

(もっと読む)

出力バッファ回路

【課題】出力遅延を短縮できる出力バッファ回路を提供する。

【解決手段】信号PenがLレベルからHレベルに切り替わり信号NenがHレベルからLレベルに切り替わった直後において、定電流源Is1が追従しきれずまた切り替わっていない場合には、ノードPは未だHレベルのままであるので、ノードOUTはLレベルのままである。この状態で、切り替え前にHレベルのノードNに接続されていたノードAは、切り替えによりHレベルのノードPへ接続される。これと同時に、インバータinv3の出力部がHレベルからLレベルに切り替わっているので、キャパシタC2を介して、ノードAもHレベルからLレベルに切り替えられる。このとき、ノードPの電位はノードAと等しくなるまで引き下げられ、Lレベルへ遷移する。

(もっと読む)

101 - 120 / 525

[ Back to top ]