Fターム[5J055GX05]の内容

Fターム[5J055GX05]に分類される特許

141 - 160 / 525

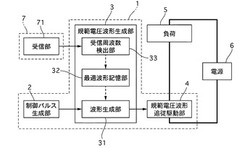

スイッチング回路

【課題】 受信機が受信するノイズを低減することができるスイッチング回路を提供すること。

【解決手段】 パワートランジスタM1を駆動して負荷5を作動させる駆動電圧波形を生成するスイッチング回路1において、ラジオ受信機7が受信している送信局の周波数を検出する受信周波数検出部33と、負荷5を制御する制御パルスを生成する制御パルス生成部と、駆動電圧の変位により生じる高調波のスペクトル包絡線の谷部が、ラジオ受信機7が受信している送信局の周波数を含むように駆動電圧波形の立ち上がり部分と立ち下がり部分の波形を生成する最適波形記憶部32と、最適波形記憶部32が生成した駆動電圧波形の立ち上がり部分と立ち下がり部分の波形を、制御パルスに適用して駆動波形を生成する波形生成部31とを備えた。

(もっと読む)

負荷制御装置

【課題】負荷への電力投入時における突入電流による素子の破壊又は劣化を防止しうる負荷制御装置を提供する。

【解決手段】操作スイッチ4から起動信号を受信したときに、制御部13は、第1電源部14への電力を供給する電源が第2電源部15から第3電源部16に切り替わる前に、主開閉部11に対して主スイッチ素子11aを導通させるための初期駆動信号を出力する。

(もっと読む)

電源検出回路

【課題】 電源検出回路の誤動作を抑制すること

【解決手段】 パワーダウン検出回路10及びパワーオン検出回路12を初期化するための初期化信号nrsetxを生成するスタータ回路18において、パワーオンが検出されている第1期間に電源電圧を中間ノードへ供給する切替回路を有する。第1の期間において第1電源電圧から中間ノードへ電源電圧を供給することにより、スタータ回路の出力を安定させることができる。その結果、電源検出回路の誤動作を抑制することができる。

(もっと読む)

半導体装置

【課題】電源回路等を追加することなく、第1の電源電圧が低下してもダイナミックVTによる高速化の効果の低減を抑制できる半導体装置を提供する。

【解決手段】第1の回路は、第1の電源電圧を供給する第1の電源ラインと第1の電源電圧よりも低い第2の電源電圧を供給する第2の電源ライン間に接続された、トランジスタを備える。制御回路は、第1の電源ラインと第2の電源ライン間に接続され、上記トランジスタのバックゲートに第1の電源電圧と第2の電源電圧の電位差よりも振幅が大きい制御信号を供給する。

(もっと読む)

半導体集積回路

【課題】本発明は、中央処理装置の低消費電力モード時に外部から供給されるアナログ信号の正確なAD変換を行うことができる半導体集積回路を提供することを目的とする。

【解決手段】割込み信号のエッジ検出を行ってエッジ検出信号を生成するエッジ検出手段11と、外部から供給されるアナログ信号をエッジ検出信号により保持し、中央処理装置13からの制御により、保持しているアナログ信号をAD変換して中央処理装置に供給するAD変換手段12とを有し、割込み信号又はエッジ検出信号によって中央処理装置が低消費電力モードからクロックを高速とする通常モードとなった後にAD変換手段12に保持しているアナログ信号をAD変換したデジタルデータを中央処理装置13に取り込む。

(もっと読む)

差動増幅器

【課題】入力端子にノイズが発生する。

【解決手段】第1の電流経路は、第1の電源端子と第1の出力端子間に接続され、制御端子に差動入力信号の一方が入力される第1のトランジスタと、第2の電源端子と第1の出力端子との間に接続され、制御端子に差動入力信号の他方が入力される第2のトランジスタと、第1の電源端子と第1のトランジスタとの間に接続される第1のスイッチ回路とを有し、第2の電流経路は、第2の電源端子と第2の出力端子との間に接続され、制御端子に差動入力信号の一方が入力される第3のトランジスタと、第1の電源端子と第2の出力端子との間に接続され、制御端子に差動入力信号の他方が入力される第4のトランジスタと、第2の電源端子と第3のトランジスタとの間に接続される第2のスイッチ回路とを有し、第1、第2のスイッチ回路は、制御信号により導通状態が制御される差動増幅器。

(もっと読む)

光電センサユニット

【課題】複数の機能を備える光電センサユニットにおいてユーザの用途やワークに応じた設定を容易に設定可能とすることで、光電センサユニットが有する能力を適切に引き出すことができる光電センサユニットを提供すること。

【解決手段】検出機能及び表示機能を定める複数の設定パラメータの設定内容を初期化する通常の初期化処理を実行する通常初期化モードと、ユーザの用途に応じて一部の設定パラメータを推奨される設定内容に変更した上で、残りの設定パラメータを初期化する特別初期化モードのいずれかを選択する設定画面を表示し、特別初期化処理が実行されると、複数の設定パラメータの組み合わせが推奨される設定内容に自動的に設定される。

(もっと読む)

電源回路、及び電子機器

【課題】FET内で発生するオン抵抗の上昇を抑制することで、使用するFETの耐性を下げ、以ってコストを低減する

【解決手段】FETをオン・オフするためのゲート電圧を所定タイミングで供給するゲートドライブ回路と、第一入力ラインと前記ゲートドライブ回路との間に介在して、第一入力ラインに供給されるゲートドライブ電圧の電圧値が一定の値になった場合に第一入力ラインとゲートドライブ回路とを導通させる第一のスイッチ回路と、スタート信号が前記FETのスイッチング動作をオフにすることを示すローレベルに変化した場合に、この信号変化に応じて第一入力ラインからゲートドライブ回路へのゲートドライブ電圧の供給を遮断する第二のスイッチ回路と、を有する。

(もっと読む)

パルス幅変調回路および電圧帰還型D級増幅回路

【課題】出力負荷を駆動する電圧帰還型D級増幅回路の周波数特性を改善する。

【解決手段】入力信号のPWM変調を行なう比較回路(26A,26B)に、PWMキャリアとなる三角波(TOSC)を与える三角波信号発生器(30)に対し、三角波の勾配を補正する三角波補正回路(32)を設ける。三角波(TOSC)のスルーレート(勾配)を出力回路駆動用指令値(COMPOUTP,COMPOUTM)のデューティが50%近傍となる領域において小さくする。

(もっと読む)

半導体集積回路

【課題】ゲート面積を増大させることなく、電界効果トランジスタ間のしきい値電圧のバラツキを自律的に補正させる。

【解決手段】補正回路12は、電子回路11に含まれる半導体素子間の電気的特性の差が所定の周期内の電気的特性の劣化量より大きい場合、その電気的特性の劣化量の小さい方の半導体素子の劣化を進行させ、電子回路11に含まれる半導体素子間の電気的特性の差が所定の周期内の電気的特性の劣化量より小さい場合、その電気的特性に差のある半導体素子の劣化を所定の周期ごとに交互に進行させる。

(もっと読む)

入力信号の移動平均を出力する平均化回路

【課題】アナログ入力信号をデジタル化することなく、そのアナログ信号形態のままで移動平均による平均化処理を行わせ、これにより、回路の簡単や消費費電力の低減化をはかりつつ、後段でのアナログ信号処理を行いやすくする。

【解決手段】積分回路を形成する演算増幅器12と、一方の電極端子に入力信号Vinが印加されるとともに、他方の電極端子がスイッチング回路ph1またはph2を介して基準電位または上記演算増幅器の積分入力に接続される第1の入力容量素子C1と、一方の電極端子がスイッチング回路ph3またはph4を介して上記演算増幅器の積分出力または上記演算増幅器の積分入力に接続されるとともに、他方の電極端子が基準電位に接続される第2の入力容量素子C2を有し、スイッチング回路ph1,ph3とph2,ph4は、入力信号Vinの周波数域よりも十分に高い周波数でオン/オフさせられるとともに、一方のオフ区間内に他方がオンされ、かつ他方のオフ区間内に一方がオンされる。

(もっと読む)

半導体集積回路装置及び電源システム

【課題】パワースイッチをオンとする際に発生する電源ノイズが許容値を超えないようにし、かつ、内部回路に与える電源電圧の立ち上がり時間を短縮することができるようにした半導体集積回路装置を提供する。

【解決手段】信号処理回路15に対する電源投入時に、パワースイッチをなすNMOSトランジスタ21−1〜21−4、22−1〜22−4のうち、まず、NMOSトランジスタ21−1〜21−4をオンとする。その後、信号処理回路15が出力端子20−1に出力する出力信号OUTの電圧変化を検出し、電源ノイズがピーク値に達したことが検出されると、NMOSトランジスタ22−1〜22−4をオンとする。

(もっと読む)

高速多重化回路

【課題】高速動作時の出力波形品質を改善する。

【解決手段】高速多重化回路は、データ信号列(D1P,D1N),(D2P,D2N)毎に設けられ、入力されたデータ信号列を共通に接続された信号出力端子に選択的に出力する第1のトランジスタQ1P,Q1N,Q2P,Q2Nと、トランジスタQ1P,Q1Nから構成される差動対またはトランジスタQ2P,Q2Nから構成される差動対のいずれか一方をクロック信号CK1,CK2に応じてオンにする第2のトランジスタQ3,Q4と、トランジスタQ1P,Q1N,Q2P,Q2N,Q3,Q4にコレクタ電流を流す電流源となる第3のトランジスタQ6,Q7と、第3のトランジスタQ6,Q7のコレクタとエミッタ側の電源電圧VEEとの間に挿入されたコンデンサC1とを備える。

(もっと読む)

電子制御装置

【課題】誘導性負荷に通電される電流値をPWM制御する電子制御装置において、負荷の個体差、温度特性によるインダクタンスと抵抗値のばらつきがあってもオーバーシュート・アンダーシュートの発生を回避でき、短時間に精度よく電流制御を行える方法を提供する。

【解決手段】直前のPWM周期の電圧を印加する区間の電流計測値の最大値および電圧を印加しない区間の電流計測値の最小値を計測する電流計測部244と、電流最大値と電流最小値から負荷11のインダクタンスと抵抗値を推定する負荷R・L推定部245と、負荷のインダクタンス値と抵抗値とから次PWM周期の電圧印加時間による誘導性負荷に通電される電流を予測して、目標電流設定部243で設定された目標電流と比較することにより、次PWM周期のデューティ比を決定するPWM設定部246とを備え、次PWM周期のデューティ比でPWM駆動回路を駆動する。

(もっと読む)

エンハンスメントモード型およびデプレションモード型のワイドバンドギャップ半導体JFETのためのゲートドライバ

接合形電界効果トランジスタ(JFET)を駆動するための、DC接続2段ゲートドライバが提供される。JFETは、SiC JFETのようなワイドバンドギャップ接合形電界効果トランジスタ(JFET)であり得る。ドライバは、第1ターンオン回路、第2ターンオン回路及びプルダウン回路を含む。ドライバは、入力パルス幅変調(PWM)制御信号を受け入れて、JFETのゲートを駆動させるための出力ドライバ信号を発生させるように配置される。 (もっと読む)

マルチプレクサ回路

【課題】マルチプレクサの動作異常を正確に検出可能とするマルチプレクサ回路を提供する。

【解決手段】複数チャンネルから入力されるアナログ入力信号を順次取り込み、当該入力信号を多重化して出力するマルチプレクサと、当該マルチプレクサから出力されるアナログ入力信号を複数のチャンネルに各々対応した複数のデジタル出力信号へ変換するADコンバータと、複数のデジタル出力信号の出力値を監視し、当該出力値が全て予め定められた範囲内である状態が予め定められた判定時間の間継続している場合、マルチプレクサの動作が異常状態であると判定する処理装置と、アナログ入力信号の1つとして、判定時間より短い周期のパルス信号をマルチプレクサへ出力するパルス信号発生装置とを備えるマルチプレクサ回路。

(もっと読む)

半導体集積回路

【課題】従来の半導体集積回路は、クロスオーバー電圧の変動幅が増大するという問題があった。

【解決手段】本発明にかかる半導体集積回路は、差動入力の一方に基づいて第1及び第2の信号を生成するプリドライバ4cと、差動入力の他方に基づいて第3及び第4の信号を生成するプリドライバ回路4dと、VDDとVSSとの間に設けられ、第1の信号に基づいて制御されるMN4と、第2の信号に基づいて制御されるMP4と、からなる出力回路5aと、VDDとVSSとの間に設けられ、第3の信号に基づいて制御されるMN8と、第4の信号に基づいて制御されるMP8と、からなる出力回路5bと、VDDに応じた第1の制御信号を生成する制御信号生成回路6と、を備える。さらに、プリドライバ4cは、第1の制御信号に基づいて第1の信号を制御し、第2のプリドライバ4dは、第1の制御信号に基づいて第3の信号を制御する。

(もっと読む)

CV変換回路

【課題】コストおよび消費電力の増大をともなう高速の演算増幅器に依存することなく、IC化に適した回路でもって、高い周波数領域での静電容量挙動を高感度かつ高確度に検出できるようにし、これにより、高周波領域での誘電率挙動による物性の検査や分析を的確に行うことを可能にする。

【解決手段】2つのセンサ容量素子Cx1,Cx2を高周波クロック信号+Φ1に同期して相補的に充放電させる通電回路50と、その2つのセンサ容量素子の通電電流差分ΔIxと上記高周波クロック信号+Φ1とのアナログ乗算操作によって、上記通電電流差分に応じた直流成分を有する電圧Vo1を出力する同期検波回路10と、この同期検波回路10の検波出力電圧を平滑処理しながら増幅する演算増幅器30とを備え、この演算増幅器30の出力から上記2つのセンサ容量素子の静電容量差分ΔCxに対応する直流出力電圧を得る。

(もっと読む)

ドライブ回路

【課題】連続通弧により半導体スイッチが故障に至るような誤動作を回避するドライブ回路を提供する。

【解決手段】外部から入力された駆動信号に基づいて半導体スイッチ20を駆動させるドライブ回路10bであって、駆動信号に基づいて半導体スイッチ20の駆動制御を行うゲートドライバ16と、ゲートドライバ16による制御の状態にかかわらず、駆動信号の立ち上がりのタイミングに基づいて半導体スイッチ20のスイッチング周期の終了時までの所定期間に強制的に半導体スイッチ20をオフさせる強制オフ回路18とを備える。

(もっと読む)

負荷駆動装置及び負荷駆動制御装置

【課題】パワーオンリセット以外のリセットの場合に負荷を駆動し続け、パワーオンリセットの場合には、例えば負荷を駆動するための信号が与えられるまで、負荷を駆動しないようにすることが可能な負荷駆動装置、及び該負荷駆動装置を備える負荷駆動制御装置を提供する。

【解決手段】電源ラインBL側と接地電位との間に直列に接続されたコンデンサC1及び抵抗R1からなる微分器が電源ラインBLの電圧の立ち上がりを微分した微分電圧に基づいて、入力端子221,231を電源ラインBLに夫々プルアップする抵抗R4,R14の入力端子221,231側と接地電位との間にダイオードD3,D13を介して接続されたFETQ1が、少なくとも入力端子221,231に入出力ポート35,36より負荷L1,L2を駆動するための信号を与えられるまで導通する。

(もっと読む)

141 - 160 / 525

[ Back to top ]