Fターム[5J055GX05]の内容

Fターム[5J055GX05]に分類される特許

61 - 80 / 525

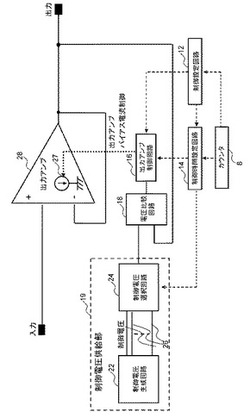

スルーレート制御回路、制御方法及び半導体集積回路

【課題】出力アンプのスルーレートを、出力負荷変動があっても高精度に調整可能なスルーレート制御回路を提供すること。

【解決手段】制御時間設定回路がスルーレートを検出するタイミング信号を発生し、電圧比較回路が、出力アンプの出力信号と、上記のタイミング信号によるタイミングに応じた制御電圧との比較を行う。比較結果に応じて、出力アンプ制御回路が、出力アンプのバイアス電流を制御する。上記した処理を、スルーレート制御期間において複数回繰り返す。

(もっと読む)

ホールド回路

【課題】保持電圧の下降または上昇傾きを良好に調整可能なホールド回路を提供すること。

【解決手段】ホールド回路10は、入力端子20、第1出力端子22、基準電圧端子24、オペアンプ30、ダイオード32、コンデンサ36、抵抗R0、電圧発生回路50、を備えている。コンデンサ36は、一端が接続点26に接続され、他端が基準電圧端子24に接続される。抵抗R0は、一端が接続点26に接続される。ダイオード52のアノードが、オペアンプ38を介して接続点26に接続される。抵抗R0の他端と中間接続点58とが接続される。オペアンプ30は、非反転入力端子30bが入力端子20に接続され、反転入力端子30aが接続点26に接続され、出力端子30cがダイオード32に接続される。電圧発生回路50は、ダイオード52に入力される出力電圧V22から変化させたオフセット電圧V23を生成して、中間接続点58から出力する。

(もっと読む)

出力回路、システム、及び出力回路の制御方法

【課題】信号波形の変異を抑制すること。

【解決手段】第1のトランジスタT1は、信号S3に応答してオンオフし、オンしたトランジスタT1は外部端子P2に接続された伝送路27をプルダウンする。伝送路27のレベルは、トランジスタT1のゲートと外部端子P2とをACカップリングするキャパシタC1により、キャパシタC1の容量値に応じた傾きで立ち下がる。プルダウン回路44は、外部端子P2の電位に応じて、トランジスタT1のゲート電圧をプルダウンする。

(もっと読む)

負荷駆動回路

【課題】複数の電源電圧条件に対して電流制限特性が追従し、負荷特性に適した電流制限を行なう負荷駆動回路を提供する。

【解決手段】図1に示す負荷駆動回路は、電源及び負荷に接続された出力MOSトランジスタと、出力MOSトランジスタの出力電圧に応じて、出力MOSトランジスタに流れる出力電流を複数段階の制限電流に制限すると共に、制限電流が切り替わる際の出力電圧を電源電圧の変化に基づいて切り替える電流制限値切り替え回路と、を備える。その結果、段階的に電流制限を行い、過剰な電流制限となることを妨げ、負荷条件の拡大を図る。さらに、電流制限値の切り替えを電源電圧に対応させて行なうため、当初の電源電圧条件とはことなる電源電圧で使用したとしても、電流制限特性が電源電圧の変動に追従し、全体として負荷特性に適した電流制限を行なうことができる。

(もっと読む)

誘導性負荷駆動装置

【課題】チャンネル毎に独立した駆動指令信号で誘導性負荷を駆動し、チャンネル数や駆動周波数にかかわらず各チャンネルのオフタイミングを自律的に調整する。

【解決手段】マスク信号生成回路3は、何れかのチャンネルの出力トランジスタTkがオフしたことを検出すると、当該オフした時点から、当該オフしたチャンネルの出力端子Pkの電圧Vkが所定のしきい値電圧Vtk以下に低下する時点まで、他のオンしているチャンネルのマスク信号ManをHレベルにし、当該オフ移行チャンネルおよび他のオフしているチャンネルのマスク信号ManをLレベルのまま保持する。その結果、他のオンしているチャンネルの駆動指令信号SnがLレベルに変化しても、駆動信号DnはHレベルのまま保持され、出力トランジスタTnのオフ移行動作が禁止される。

(もっと読む)

スイッチング素子駆動回路

【課題】スイッチング素子駆動回路において、スイッチング素子のスイッチング損失を抑制する。

【解決手段】 ゲート電圧検出回路201は、スイッチング素子11のゲート電圧Vgsを検出し、このゲート電圧がスイッチング素子11の閾値電圧未満に設定された所定電圧未満のとき、Hレベルの昇圧指示信号を出力する。電圧制御回路103は、前記昇圧指示信号がLレベルの間は、制御電源102の所定電圧V1をそのまま出力し、前記昇圧指示信号がHレベルの間は、前記所定電圧V1を昇圧した電圧V2を出力する。駆動信号出力回路104は、PWMパルス出力回路111から出力されるPWMパルスの電圧を電圧制御回路103から出力される電圧に増幅する。従って、駆動信号出力回路104からスイッチング素子11への駆動信号は、前記PWMパルスがHレベルになった時に、先ず昇圧された電圧V2となり、スイッチング素子11のゲート電圧Vgsが所定電圧にまで上昇すると、所定電圧V1となる。

(もっと読む)

スイッチング回路および試験方法

【課題】半導体スイッチングデバイスが完全な機能を維持していることを保証するために、サービス中にそれらを試験する方法を提供する。

【解決手段】負荷および電圧源2に接続するためのスイッチング回路1であって、負荷への電力をスイッチオンおよびスイッチオフするための1つまたは複数のスイッチングデバイス6、7、...、nと、負荷を短絡し、それにより負荷を電圧源から隔離するためのプルダウンデバイス4と、一度に複数のスイッチングデバイスのうちの少なくとも1つを起動するために、電圧源が負荷から隔離されている間に動作させることができるコントローラ3とを備え、起動された前記スイッチングデバイスまたは個々のスイッチングデバイスを通って電流が流れ、この電流を測定して、起動された前記スイッチングデバイスまたは個々のスイッチングデバイスが適切に動作しているかどうかを試験することができるスイッチング回路1が開示される。

(もっと読む)

半導体出力回路及び外部出力信号生成方法並びに半導体装置

【課題】電源電圧の低下による外部出力信号のばらつきを抑制する。

【解決手段】内部入力信号Aの電位がグランド側からVDD側、あるいはVDD側からグランド側へ変化するのに応じて、出力部1は外部出力信号EBの電位を変化させる。差動部2は、外部出力信号EBと、所定の基準信号VREFとに応じた出力信号を出力し、外部出力信号EBが所定の基準信号VREFに応じた電位となるようボルテージフォロアとして機能する。これにより、外部出力信号EBの低電圧側出力電圧VOLのばらつきを抑制する。

(もっと読む)

電源供給装置、情報処理装置

【課題】

サージ電圧を効果的に低減するとともに、簡易な回路構成で消費電力を低減した電源供給装置及び情報処理装置を提供する。

【解決手段】

電源供給装置は、交流電力が入力される入力端子と、前記入力端子に入力される交流電力を整流する整流回路と、前記整流回路で整流された電力を平滑化する平滑用キャパシタと、前記平滑用キャパシタの両端子間に直列に接続される、トランス用一次巻線及びスイッチング素子と、前記トランス用一次巻線に結合されるトランス用二次巻線と、前記トランス用二次巻線に接続される出力端子と、前記スイッチング素子に並列に接続されるスナバ回路であって、第1キャパシタ及び第2キャパシタの並列回路と、前記並列回路に直列に接続される抵抗器とを有するスナバ回路とを含む。

(もっと読む)

負荷駆動装置

【課題】スイッチング素子の立ち上がりの速度を高速に維持しつつ、スイッチング素子を駆動するドライバ回路の消費電流を削減することができる負荷駆動装置を提供する。

【解決手段】負荷10に接続されるスイッチング素子50と、定電流を生成する定電流生成部30と、定電流生成部30から流れ込む定電流の大きさに応じたオン時間でスイッチング素子50をオンするドライバ回路40と、を備えた構成とする。そして、定電流生成部30は、スイッチング素子50がオンするオン時間に達するまではドライバ回路40に第1電流量の大きさの定電流を流すことでスイッチング素子50の立ち上がりの速度を高速に維持する。また、定電流生成部30は、スイッチング素子50がオンするオン時間が経過した後はドライバ回路40に第1電流量よりも小さい第2電流量の定電流を流すことでドライバ回路40の消費電流を削減する。

(もっと読む)

内燃機関制御装置

【課題】電磁負荷を駆動する内燃機関制御装置において、電磁負荷の駆動周期が短い場合でも、該電磁負荷の故障診断精度を向上させ、ノイズに影響されない高速制御を安定して行う。

【解決手段】電磁負荷制御装置において、前記電圧異常を検出する手段をマスクするためのマスク手段を備え、前記マスク手段は、前記電圧異常の検出タイミングを、電磁負荷遮断と電磁負荷の通電とが繰り返される電磁負荷の通電開始タイミングに合わせて設定してあり、電磁負荷の通電遮断時より一定時間を内部タイマによってカウントすることにより、前記一定時間内に検出された電圧異常の誤検出をマスクするように構成する。

(もっと読む)

負荷駆動装置

【課題】より高速駆動に対応でき、かつ、消費電流を低減することができる負荷駆動装置を提供する。

【解決手段】ダーリントン回路によってスイッチングデバイス2を駆動するようにし、ダーリントン回路を構成する第1PchMOSFET5と第2PchMOSFET6のドレインを共にスイッチングデバイス2を構成するIGBTのゲートに接続する。これにより、第2PchMOSFET6の駆動電流もIGBTの駆動に用いることができるため、消費電流を低減できると共に、より大電流でのIGBT駆動が可能になるため高速駆動を行うことができる。また、第2抵抗4と並列的にスイッチ10を備え、このスイッチ10をプルアップ駆動時にオンさせる。これにより、プルアップ駆動時に第1PchMOSFET5のゲート−ソース間の抵抗値を低下させることが可能となり、駆動スピードが低下することを抑制することが可能となる。

(もっと読む)

ドライバ回路およびそれを用いた試験装置

【課題】ポジティブエッジの波形、ネガティブエッジの波形の少なくとも一方を調節可能なドライバ回路を提供する。

【解決手段】分岐回路10は、送信すべき入力信号SINを複数の経路12に分岐する。各タイミング調節回路20は、それぞれが対応する経路に分岐された送信すべき信号Saのポジティブエッジおよびネガティブエッジの少なくとも一方に遅延を与える。合成出力回路30は、複数のタイミング調節回路20の出力信号Sbを合成し、合成された信号SOUTを伝送線路3に出力する。

(もっと読む)

ゲート駆動回路及び半導体装置

【課題】応答性を損なうことなく能動クランプ素子の損失電力を低減できる能動クランプ回路を用いたゲート駆動回路及び半導体装置を提供する。

【解決手段】スイッチ素子Tr7のゲートを駆動するゲート駆動回路であって、制御信号に基づいてスイッチ素子Tr7を駆動する駆動部(トランジスタTr1,Tr2,Tr4,Tr5)と、スイッチ素子Tr7の第1主端子(ドレイン)と第2主端子(ソース)との間に印加される電圧が所定電圧以上の場合に、駆動部によるスイッチ素子Tr7に対する駆動動作を強制的に遮断して、スイッチ素子Tr7の第1主端子と第2主端子との間の電圧がクランプされるようにスイッチ素子Tr7を駆動するアクティブクランプ回路(ダイオードD1、ツェナーダイオードZD1、抵抗R1、トランジスタTr3,Tr6)とを備える。

(もっと読む)

反転電圧出力回路

【課題】入力信号の変化に応じて直流電源の非接地電圧と接地電圧の間で反転する電圧を出力する回路であり、非接地端子に接続されている電源線に生じる電圧変動を抑制する。

【解決手段】電流制限素子14とスイッチング回路16が直列に接続されており、電流制限素子とスイッチング回路の中間点22の電圧を出力する。スイッチング回路の導通時にスイッチング回路を流れる電流が電流制限素子によって制限される。直流電源の非接地端子に接続されている電源線12に生じる電圧変動が抑制され、電源線12に接続されているアナログ回路等の動作が安定する。

(もっと読む)

リセット回路およびシステム

【課題】 パワーオンまたはパワーダウンを検出するリセット回路を誤動作することなく動作させ、パワーオン時にリセット信号を正常に出力する。

【解決手段】 電源検出回路は、電源電圧が第1電圧を超えたときにパワーオン状態を示すパワーオン信号を活性化するとともに、初期化信号の活性化中に初期化される。スタータ回路は、電源電圧線と接地線の間に直列に配置された抵抗素子、遮断スイッチおよびキャパシタを有し、抵抗素子と遮断スイッチとを接続する第1接続ノードから初期化信号を出力する。遮断スイッチは、パワーオン信号の活性化中にオフする。このため、パワーオン状態中に、抵抗素子を介してキャパシタが充電されることを防止できる。この結果、キャパシタのTDDBの劣化を確実に防止でき、リセット回路を搭載する半導体装置およびシステムの誤動作を防止できる。

(もっと読む)

リセット回路

【課題】マイクロコンピュータとCPUを安全かつ確実にリセットして正常起動させる。

【解決手段】第1制御回路41は第2電圧が動作電圧に達したときにリセット信号が入力されていれば初期化後に起動し、レギュレータIC20は第1電圧をレギュレートして生成した第2電圧を第1制御回路41に供給し、第2制御回路42は第3電圧が動作電圧に達したときにリセット信号が入力されていれば初期化後に起動し、レギュレータIC30は、第3電圧をレギュレートして生成した第4電圧を第2制御回路42に供給する機器において、リセット回路100は、第1電圧が第5電圧を超えて150msが経過するまでリセット信号の出力を継続させ、第1電圧が第5電圧を超えてから150msが経過するとリセット信号の出力を停止する。(第1電圧≧第2電圧、第3電圧≧第4電圧、第1電圧>第3電圧、第5電圧>第2電圧)

(もっと読む)

通信ドライバ回路

【課題】外乱ノイズが侵入した場合でも、通信線の信号レベルの変動をより確実に防止できる通信ドライバ回路を提供する。

【解決手段】通信ドライバ部11は、信号バス17にノイズが印加されると、信号レベル変化阻止回路14が、出力段がオープンコレクタタイプで構成される反転増幅回路13の出力信号がローレベル側に変化することを阻止するように動作する。

(もっと読む)

駆動回路

【課題】電源部品を減らし、安価な構成の駆動回路。

【解決手段】一次巻線Npと第1の二次巻線S1と第1の二次巻線の極性とは逆極性を持つ第2の二次巻線を有する2以上の二次巻線とを有し一次巻線に駆動信号が印加されるトランスDT1、第1の二次巻線からの信号によりオンオフ制御される第1スイッチング素子Qh、第2の二次巻線からの信号によりオンオフ制御される第2スイッチング素子Ql、第1の二次巻線の一端と第1スイッチング素子の制御端子との間に接続され第1スイッチング素子を駆動する第1駆動部Q11,Q12、第2の二次巻線の一端と第2スイッチング素子の制御端子との間に接続され第2スイッチング素子を駆動する第2駆動部Q21,Q22、第1の二次巻線電圧を倍電圧整流平滑して第1駆動部に供給する倍電圧整流平滑回路D11,D12,C11,C12、第2の二次巻線電圧を倍電圧整流平滑して第2駆動部に供給する倍電圧整流平滑回路D21,D22,C21,C22を有する。

(もっと読む)

PWM制御のデューティ決定方法

【課題】通信周波数を微小変動させる技術よりも、ノイズレベルの低減を更に図ることができるPWM制御のデューティ決定方法を提供する。

【解決手段】制御IC63が、駆動回路に出力するPWM信号のデューティを、指令値を中心に、所定期間内における平均が前記指令値に一致するように微小変動させる場合、PC68のデータベース69に、実際にPWM信号を駆動回路に与えることで発生したノイズ成分のレベル測定結果を反映したデータを、そのデューティの変動態様と共に記憶する。そして、データベース69に記憶されているデータを参照し、与えられた動作環境や動作条件等に応じて抑圧対象となる周波数帯のノイズレベルを低減するように、制御IC63によるPWMデューティの変動態様を決定する。

(もっと読む)

61 - 80 / 525

[ Back to top ]