Fターム[5J055GX05]の内容

Fターム[5J055GX05]に分類される特許

21 - 40 / 525

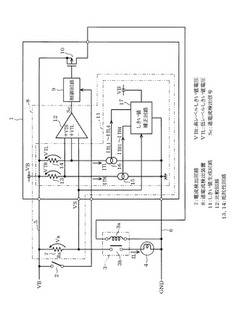

過電流検出装置

【課題】駆動に適した推奨値からずれた電気的特性を持つ負荷を駆動した場合でも誤検出を極力防止する。

【解決手段】しきい値生成回路11は、抵抗13、14にしきい値生成電流ITH、ITLを流してしきい値電圧VTH、VTLを生成し、コンパレータ12はシャント抵抗7の検出電圧Vaと比較して過電流検出信号Scを得る。しきい値補正回路17は、平均負荷電流、負荷電流の交流変化分、電源電圧VBが大きいほどしきい値電圧VTH、VTLを増やし、負荷4の温度が低いほどしきい値電圧VTH、VTLを増やす。

(もっと読む)

半導体スイッチ回路

【課題】簡易な構成によりスイッチ切替時間のさらなる高速化を図る。

【解決手段】外部から供給される外部制御信号に応じて、高周波スイッチ回路101のFET1,2のオン、オフ状態を制御する駆動制御信号を出力する論理制御回路104と、FET1,2が論理制御回路104によりオフ状態からオン状態とされる際にパルス電圧を出力する切替加速回路102,103とは、それぞれの出力信号が共にFET1,2の駆動制御信号として、それぞれへ印加可能に設けられ、論理制御回路104は、定常状態においてFET1,2をオン状態とする電源電圧とほぼ等しい駆動制御信号を出力するよう構成され、切替加速回路102,103は、ピークが電源電圧を超えるパルス電圧を出力する一方、そのパルス電圧が論理制御回路104の出力信号の電圧レベルを下回った際には、その出力が遮断されるよう構成されたものとなっている。

(もっと読む)

ゲート駆動回路および電力変換装置

【課題】P型電界効果トランジスタとN型電界効果トランジスタとが同時にオン状態になる期間内で発生する短絡電流に起因する消費電力の増大を抑制するともに、パワー素子を高速スイッチングさせることが可能なゲート駆動回路を提供する。

【解決手段】このゲート駆動回路11は、PchFET12と、NchFET13と、駆動信号が入力される入力側とPchFET12のゲート(G)およびNchFET13との間に設けられ、電源電位VCCに接続されているツェナーダイオード14およびツェナーダイオード15とを備え、ツェナーダイオード14および15は、PchFET12およびNchFET13のゲート(G)に印加される電圧を、PchFET12およびNchFET13のゲート(G)の閾値電圧側にシフトさせるように構成されている。

(もっと読む)

2線式交流スイッチ

【課題】2線式交流スイッチの低消費電力化を実現する。

【解決手段】

交流電源と負荷とを結ぶ電路に挿入される2線式交流スイッチであって、スイッチ端子S1、S2と、スイッチ端子間のオンオフを制御するためのゲート端子G1、G2と、基板端子Subとを有し、スイッチ端子間に双方向に電流を流すことができ、スイッチ端子S1が交流電源1に接続され、スイッチ端子S2が負荷2に接続される半導体スイッチからなるメインスイッチ3と、メインスイッチの基板端子Subを接地するかフローティングにするかを切り替えるサブスイッチ9と、を備える。

(もっと読む)

リセット回路

【課題】マイコンのリセット端子をトランジスタによってグランドに接続することによりマイコンにリセットをかけるリセット回路において、リセット動作不能な電源電圧の領域を無くす。

【解決手段】リセット回路10は、マイコン11のリセット端子13を電源電圧(以下、VM)にプルアップする抵抗R1と、VMが所定値未満のときにトランジスタT1をオンしてリセット端子13を0Vにするリセット信号出力回路15とに加え、オンすることで抵抗R1の上流側にVMを供給するトランジスタT2と、抵抗R1の上流側とグランドとの間に接続された抵抗R2と、トランジスタT1がオン可能なVMの最低値(Vbe)より高く、上記所定値よりは低い電圧(Vbe+ダイオードD1のVf)を動作閾値電圧とし、VMがその動作閾値電圧未満である場合にトランジスタT2をオフさせておいて、マイコン11のリセットを確保する回路T3,D1,R3,R4とを備える。

(もっと読む)

トランジスタ駆動回路

【課題】より簡単な構成で、出力トランジスタを確実にオフ状態に維持できるトランジスタ駆動回路を提供する。

【解決手段】NチャネルMOSFET5とコイル2との共通接続点;出力端子OUTとグランドとの間にフライホイールダイオード3を接続する。FET5のゲートには、NPNトランジスタ6及びPNPトランジスタ7のプッシュプル回路により制御信号を出力し、トランジスタ7のベースとグランドとの間にNPNトランジスタ11を接続し、トランジスタ11のベースとグランドとの間にNチャネルMOSFET14を接続して、FET14にPWM信号を入力する。ダイオード13は、FET14がオフ状態になるとトランジスタ11のベースにベース電流を供給し、ダイオード15をダイオード13のアノードとトランジスタ6及び7のベースとの間に接続する。NPNトランジスタ22をFET5のゲートと出力端子との間に接続し、トランジスタ22をPWM信号に応じてFET5がオフする際にオンさせる。

(もっと読む)

インターフェース回路

【課題】ノイズを低減することができるインターフェース回路を提供することを課題とする。

【解決手段】インターフェース回路は、電源電圧端子が第1の電源電圧ノードに接続され、入力信号を増幅する第1のバッファ(111)と、第2の電源電圧ノード及び前記第1のバッファの電源電圧端子間に接続されるスイッチ(124)と、前記第1のバッファの入力信号がローレベルからハイレベルに立ち上がると、遅延時間経過後に前記スイッチをオフからオンに切り換える第1の制御回路(127)とを有する。

(もっと読む)

半導体装置

【課題】体格及びコストの増大が抑制された半導体装置を提供する。

【解決手段】直流電源とグランドとの間に直列接続された2つの単位回路と、単位回路を制御する制御部と、を備え、2つの単位回路の中点に誘導性負荷が接続された半導体装置であって、2つの単位回路それぞれは、第1スイッチ素子と、第1スイッチ素子と逆並列接続された還流ダイオードと、還流ダイオードと第1スイッチ素子それぞれと並列接続されたバイパス部と、を有し、バイパス部は、直列接続された第2スイッチ素子及び抵抗を有し、制御部は、2つの単位回路の第1スイッチ素子をOFF状態にするデッド期間を挟んで、2つの第1スイッチ素子を交互にON状態とし、デッド期間において、一方の第1スイッチ素子がOFF状態からON状態に移行するまで、一方の第1スイッチ素子と並列接続された第2スイッチ素子をON状態にする。

(もっと読む)

半導体素子駆動装置及び方法

【課題】並列に駆動される複数の半導体素子の特性差によって生じる、ターンオンやターンオフ時のスイッチングにおける電流の偏りを緩和すること。

【解決手段】電圧変換器14は、IGBT13−1乃至13−3の各々のエミッタセンス電流を電圧信号に変換する。平均値演算器17や誤差演算器18等の演算器は、LPF15から出力される、IGBT13−1乃至13−3の各々に対応する電圧信号の平均値を求め、それぞれの電圧信号についての平均値に対する誤差を演算する。PWM波形生成部11は、IGBT13−1乃至13−3の各々を駆動するための駆動信号(パルス信号)を出力する。差動増幅器12の各々の駆動信号を、当該IGBT13−1乃至13−3の各々に対応する誤差に基づいて調整して、当該IGBT13−1乃至13−3の各々に供給する。

(もっと読む)

半導体スイッチ及びスイッチ装置

【課題】電流変動が大きな箇所の半導体スイッチにおいて耐電流と損失を最適化する。

【解決手段】電気的特性及び種類が互いに異なるFET11とIGBT12を並列接続することで半導体スイッチ1aを形成する。端子5及び6間を接続するとき、FET11及びIGBT12は同時にオンされる。端子5及び6間の電流が小電流であるときには、FET11の内部抵抗がIGBT12よりも小さいため、FET11側に優先的に電流が流れて低損失が実現される。端子5及び6間の電流が増大するにつれて、FET11では発熱が内部抵抗増大を招くがIGBT12では内部抵抗が殆ど変化しないため、或る電流値以上では、IGBT12側に優先的に電流が流れる。結果、大電流がFET11側に流れることによるFET11の劣化又は破損が回避される。

(もっと読む)

パワーMOSFETの駆動回路およびその素子値決定方法

【課題】パワーMOSFETを高速駆動する場合であっても、寄生インダクタンスに流れる電流の時間変化に応じて発生する電圧に起因したセルフターンオンの発生を防止できるようにしたパワーMOSFETの駆動回路、また、その素子値決定方法を提供する。

【解決手段】制御回路が、駆動回路によってスイッチを駆動制御することで、(2)区間においてスイッチS2HおよびS2Lをオンすると共にその他をオフとし、(3)区間においてスイッチS1LおよびS3Hをオンすると共にその他をオフとする。すると、(2)〜(3)区間にかけて、ハイサイド側のMOSFETのゲートソース間を所定のインピーダンスに切り替えることができ、リカバリー後半に至ったとしてもハイサイド側のMOSFETのゲートソース間電圧Vgs1を閾値電圧Vt未満に抑制できる。

(もっと読む)

負荷駆動回路

【課題】オン指令期間とオフ指令期間の両期間における電流を高精度に検出する。

【解決手段】制御装置13は、PWM駆動信号のオン指令期間において、電流検出回路14による検出電流と電源電圧検出回路15による検出電源電圧を電圧方程式に適用してオン期間電流経路の抵抗値とインダクタンス値を算出する。これらの値から還流経路12以外の経路の抵抗値とインダクタンス値を減算してオフ期間電流経路の抵抗値とインダクタンス値を求める。オフ指令期間において、オフ期間電流経路の抵抗値Rとインダクタンス値L、ダイオード7の順電圧Vfおよび前回の計算で求めた前回電流値を電圧方程式に適用し、リニアソレノイド2に流れる負荷電流を順次算出する。

(もっと読む)

ゲートドライブ回路

【課題】ターンオン時のスイッチング特性が変動せず、電力損失を発生せずにスイッチング素子を安定してターンオンさせることができるゲートドライブ回路。

【解決手段】ドレインとソースとゲートとを有し且つワイドバンドギャップ半導体かなるスイッチグ素子Q1のゲートに制御回路からの制御信号を印加することによりスイッチング素子をオンオフ駆動させるゲートドライブ回路であって、制御回路とスイッチング素子のゲートとの間に接続され、第1のコンデンサC1と第1の抵抗R1とからなる並列回路と、スイッチング素子のゲートとソースとの間に接続され、制御信号のオフ信号に対して遅延させてゲートとソースとの間を短絡する短絡手段S4とを備える。

(もっと読む)

ゲートドライブ回路

【課題】ワイドバンドギャップ半導体からなるスイッチング素子の回生動作時の電力損失を抑制し、かつ、安定してターンオン/オフさせることができるゲートドライブ回路。

【解決手段】制御回路とスイッチング素子Q1のゲートとの間に接続され、コンデンサC1と抵抗R1とダイオードD1からなる直列回路と、スイッチング素子のゲートとソースとの間にPNP型トランジスタQ2が抵抗R2を介して接続され、トランジスタQ2のコレクタ・ベース間にダイオードD2が接続され、さらにトランジスタQ2のベースはダイオードD1のアノードに接続され、制御回路からのオフ信号が入力されると、トランジスタの接合電圧とダイオードD2との順方向電圧との差分電圧を残してゲートとソースとの間を短絡する。

(もっと読む)

半導体素子制御装置

【課題】駆動用半導体素子が意図せずに導通することを防止できる半導体素子制御装置を提供する。

【解決手段】駆動用トランジスタTr11は、一対の直流電源線13、14間に直流モータ12とともに直列に接続される。抵抗素子R13は、直流電源線13と駆動用トランジスタTr11のゲート端子との間に接続される。コンデンサC11および開路用トランジスタTr14の直列回路は、駆動用トランジスタTr11のゲート端子と直流電源線14との間に接続される。駆動制御回路15は、通常状態に設定されると、開路用トランジスタTr14をオンし、制御用トランジスタTr12、Tr13を通じて駆動用トランジスタTr11の導通状態を制御する。駆動制御回路15は、制御用トランジスタTr12、Tr13の双方がオフのとき、開路用トランジスタTr14をオフする。

(もっと読む)

電源回路

【課題】高速スイッチング素子である電圧駆動型トランジスタ(MOSFET)のターンオン・オフ時の電圧変化(dV/dt)と電流変化(di/dt)を緩和して、ノイズとサージ電圧の発生を抑制する電源回路を提供する。

【解決手段】トランス2に流れる電流をスイッチングさせるためのMOSFET1のゲート抵抗値を、スイッチング期間内で、MOSFET1のドレイン電圧Vdsの変化の検出と共に切り替える、MOSFET1のゲート電圧Vgは、MOSFET1のゲート電圧の最大定格Vgmax以下とする。

(もっと読む)

CMOSインバータを用いたマルチプレクサ、デマルチプレクサ、ルックアップテーブルおよび集積回路

【課題】CMOSインバータのP形MOSトランジスタのボディバイアスを変化させても、入力信号の立ち上がりと立ち下がりの伝搬遅延時間の差を、従来のものより小さく保てるマルチプレクサ、デマルチプレクサ、ルックアップテーブルおよび集積回路を提供する。

【解決手段】パスゲートM1、M2の出力に初段出力バッファとして低しきい値CMOSインバータINV1を接続したセレクター回路を基本構成とし、それを用いたマルチプレクサ、デマルチプレクサ、ルックアップテーブルおよび集積回路であって、パスゲートはそのボディ端子が可変電位をとるボディバイアス電源VBNに接続し、INV1のP形MOSトランジスタM3のしきい値電圧を可変にできるようにそのボディ端子は可変電位をとるボディバイアス電源VBPに接続し、そのN形MOSトランジスタM4はそのしきい値電圧を固定するためにそのボディ端子が固定電位をとる電源VSSに接続する。

(もっと読む)

リンギング抑制回路

【課題】より簡単な構成で波形歪みのエネルギーを消費させ、リンギングを確実に抑制できるリンギング抑制回路を提供する。

【解決手段】一対の信号線3P,3N間に、NチャネルMOSFET7を接続し、制御回路14は、伝送線路3を介して伝送される差動信号のレベルがハイからローに変化したことを検出すると、NチャネルMOSFET7を一定期間オンさせる。すなわち、差動信号のレベルが遷移する期間にNチャネルMOSFET7が導通することで信号線3P,3N間のインピーダンスを大きく低下させ、差動信号波形の歪みエネルギーを吸収させてリンギングの発生を確実に抑制する。

(もっと読む)

スイッチング回路

【課題】大電流を制御可能なスイッチング回路において、部品点数を少なくしたコンパクトな構成にて、スイッチング損失を低減するとともにサージ電圧を抑制することができるスイッチング回路を提供する。

【解決手段】高電圧ラインL1と低電圧ラインL2との間においてMOSFET30,31,32,33が並列接続され、ゲート抵抗50,51,52,53の第1の端子がMOSFET30〜33のゲート電極に接続されている。MOSFET30,31,32,33毎に設けられたゲート抵抗50,51,52,53の第2の端子がゲート電圧印加ラインL3を介してパルス発生回路60と接続されている。パルス発生回路60により、ゲート抵抗50〜53を介してMOSFET30〜33のゲート電極にパルス状のゲート電圧が印加される。ゲート電圧印加ラインL3と高電圧ラインL1との間の1箇所にコンデンサ70が接続されている。

(もっと読む)

半導体装置及びその駆動方法

【課題】信号処理回路に対する電源電圧の供給及び遮断を選択することができるスイッチとして機能する回路(電源供給制御回路)として好ましい回路を提供する。

【解決手段】信号処理回路に対する電源電位の供給を担う第1の配線と、電源電位を供給する第2の配線との電気的な接続を制御するトランジスタ、及び、信号処理回路に対する電源電位の供給を担う第1の配線を接地させるか否かを制御するトランジスタとを設け、当該2つのトランジスタの少なくとも一方として、チャネルが酸化物半導体層に形成されるトランジスタを適用する。これにより、2つのトランジスタの少なくとも一のカットオフ電流に起因する消費電力を低減することが可能となる。

(もっと読む)

21 - 40 / 525

[ Back to top ]