Fターム[5J056CC06]の内容

Fターム[5J056CC06]に分類される特許

1 - 20 / 82

複数の集積回路にインタフェース信号を供給する方法および回路

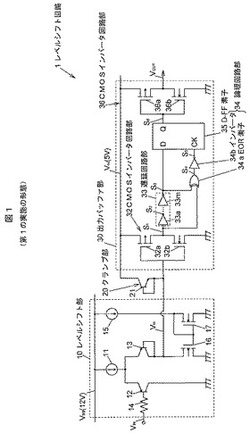

レベルシフト回路

【課題】占有面積が小さく、温度変化や素子のバラツキの影響を受け難く、さらに、ノイズを低減することで高品位のレベルシフトを実現することができるレベルシフト回路を提供する。

【解決手段】レベルシフト回路1は、主に、第1の信号(VIN)をレベルシフトして第2の信号(Vm)を出力するレベルシフト部10と、pMOSトランジスタ32aとnMOSトランジスタ32bを含み、第2の信号を反転させた第3の信号(S1)を出力するCMOSインバータ回路部32、偶数個のインバータ素子(第1のインバータ33a〜第mのインバータ33m)を含み、第3の信号を遅延させた第4の信号(S3)を生成する遅延回路部33、論理素子を含み、第3の信号及び第4の信号が入力して第5の信号(S5)を出力する論理回路部34、及び第4の信号と第5の信号が入力するD−FF素子35、を含む出力バッファ部30と、を備える。

(もっと読む)

受信回路、半導体装置、センサ装置

【課題】受信動作への切換時に発生するノイズを抑制する。

【解決手段】受信回路10は、圧電センサ2の受信信号SP及びSNを増幅するアンプ15と、圧電センサ2の一端とアンプ15の一端との間に並列接続されて受信動作への切換時に位相をずらしてオンされる複数のトランジスタ11a及び11b(ないしは12a及び12b)と、を有する。

(もっと読む)

半導体集積回路

【課題】外部から印加された電圧のノイズを減少させて電圧を安定化させる半導体集積回路を提供する。

【解決手段】本発明は、電圧ノイズを減少させて電圧を安定化させる半導体集積回路において、第1電流が流れる第1内部回路と、第2電流が流れる第2内部回路と、前記第1電流のうちの一部と前記第2電流のうちの一部は第1接地パッドに流れ、残りの前記第1電流と残りの前記第2電流は第2接地パッドに流れるように構成された電圧安定化部とを含むことを特徴とする。

(もっと読む)

通信システム

【課題】通信線に現れるリンギング現象を効果的に抑制することができる通信システムを得る。

【解決手段】NPNバイポーラトランジスタT11のエミッタは抵抗R11の一端に接続されるとともに接地レベルに接続され、コレクタは抵抗R12の一端及びコンデンサC12の一方電極に接続され、ベースは抵抗R11の他端及びコンデンサC11の一方電極に接続される。コンデンサC11の他方電極はLライン通信線10Lに接続される。PNPバイポーラトランジスタT12のエミッタは電源電圧V11を受け、コレクタはNMOSトランジスタQ11のゲートに接続される。NMOSトランジスタQ11のドレインはHライン通信線10Hに接続され、ソースがLライン通信線10Lに接続され、ゲートは抵抗R14を介して接地される。

(もっと読む)

電源回路、回路装置及び電子機器

【課題】安定な断熱的回路動作を実現し、消費電力を抑制することができる電源回路、回路装置及び電子機器等を提供すること。

【解決手段】電源回路200は、第1の基準電圧を基準として電圧が周期的に変化する、断熱的回路動作用の第1の電源電圧VPと、第2の基準電圧を基準として電圧が周期的に変化する、断熱的回路動作用の第2の電源電圧VMとを出力する電圧出力回路100と、制御信号SCに基づいて電圧出力回路100を制御する制御回路210と、第1の電源電圧VP及び第2の電源電圧VMに基づいて制御信号SCを生成して制御回路210に出力する制御信号生成回路240とを含み、制御回路210は、制御信号SCに基づいて、電圧出力回路100から出力される第1の電源電圧VP及び第2の電源電圧VMの振幅を可変に制御する。

(もっと読む)

スルーレートコントロール装置、スルーレートコントロール方法

【課題】クロック信号の出力バッファにおいて、クロック信号の周波数に応じたスルーレートの調整を行うことによりEMIノイズを抑制することが可能なスルーレートコントロール装置、およびスルーレートコントロール方法を提供すること。

【解決手段】変換ゲインGiに応じて、入力されるVCO入力電圧Viをクロック信号CKoに変換する電圧制御発振器15aを有するPLL回路24aと、VCO入力電圧Viおよび変換ゲインGiの各々に対して正の相関関係を有する制御電流Ibを出力する電圧電流変換器19aと、制御電流Ibに応じてドライブ電流を設定するバッファ制御回路21aと、ドライブ電流で、クロック信号CKoを出力する出力回路22aとを備える。よって、クロック信号CKoの周波数fに比例して出力回路22aのドライブ能力が大きくなる関係を有し、周波数fに応じて好適なスルーレートが決定することができる。

(もっと読む)

リンギング抑制回路

【課題】より簡単な構成で波形歪みのエネルギーを消費させ、リンギングを確実に抑制できるリンギング抑制回路を提供する。

【解決手段】一対の信号線3P,3N間に、NチャネルMOSFET7を接続し、制御回路14は、伝送線路3を介して伝送される差動信号のレベルがハイからローに変化したことを検出すると、NチャネルMOSFET7を一定期間オンさせる。すなわち、差動信号のレベルが遷移する期間にNチャネルMOSFET7が導通することで信号線3P,3N間のインピーダンスを大きく低下させ、差動信号波形の歪みエネルギーを吸収させてリンギングの発生を確実に抑制する。

(もっと読む)

プリエンファシス電圧ジッターを減少させる装置および方法

【課題】データ送信における電圧ジッターを減少させる送信器回路を提供すること。

【解決手段】第一の電流源と、該第一の電流源と第一のノードとの間に結合されている第一のフィルタと、該第一の電流源と第二のノードとの間に結合されている第二のフィルタと、第二の電流源と、該第二の電流源と第三のノードとの間に結合されている第三のフィルタと、該第二の電流源と第四のノードとの間に結合されている第四のフィルタと、該第一のノード、該第二のノード、該第三のノードおよび該第四のノードに結合されているドライバースイッチ回路などを含む、送信器回路。

(もっと読む)

半導体集積回路装置

【課題】回路動作速度を犠牲にすることなく、待機時の消費電力を小さくすることが可能な半導体集積回路装置を提供する。

【解決手段】同一Si基板上に少なくともソース・ゲート間又はドレイン・ゲート間に流れるトンネル電流の大きさが異なる複数種類のMOSトランジスタを設け、当該複数種類のMOSトランジスタの内、トンネル電流が大きい少なくとも1つのMOSトランジスタで構成された主回路と、トンネル電流が小さい少なくとも1つのMOSトランジスタで構成され、主回路と2つの電源の少なくとも一方の間に挿入した制御回路を有し、制御回路に供給する制御信号で主回路を構成するソース・ゲート間又はドレイン・ゲート間に電流が流れることの許容/不許容を制御し、待機時間中に主回路のINとOUTの論理レベルが異なる際のIN−OUT間リーク電流を防止するスイッチを主回路のIN又はOUTに設ける。

(もっと読む)

信号伝達回路及びこれを用いたスイッチ駆動装置

【課題】入力信号をレベルシフトして出力するレベルシフト回路を有しながらも、電源の電圧変動等による誤信号の出力を抑えることが可能となる信号伝達回路を提供する。

【解決手段】第1入力信号および第2入力信号の各々をレベルシフトし、それぞれ第1シフト済み信号および第2シフト済み信号として出力する、レベルシフト回路を備え、レベルシフト回路は、第1入力信号に応じて開閉するスイッチング素子と抵抗を有する第1直列回路、および、第2入力信号に応じて開閉するスイッチング素子と抵抗を有する第2直列回路が、電源と接地端との間において互いに並列に設けられており、第1直列回路上の電圧を第1シフト済み信号として、第2直列回路上の電圧を第2シフト済み信号として、それぞれ出力するようになっており、接地端から第1直列回路および第2直列回路に向かって逆電流が流れることを防止する、逆流防止部を備えた信号伝達回路とする。

(もっと読む)

通信モジュール、リーダライタ

【課題】部品を内蔵できる配線板を有する通信モジュールであって、アンテナの特性に応じて整合の調整が可能な通信モジュールおよびこれを用いたリーダライタを提供すること。

【解決手段】配線板と、配線板に備えられた通信処理用ICと、通信処理用ICに電気的に接続されて配線板に備えられた、外部に設けられるアンテナとの整合をとる整合回路と、を具備し、整合回路が、キャパシタまたはインダクタを少なくとも含む受動素子回路網の回路であり、該受動素子回路網を構成する回路エレメントのうちの少なくともひとつが、配線板に内蔵された第1の受動素子部品と、配線板の面上に実装された、該第1の受動素子部品と同じ種の受動素子部品である第2の受動素子部品との並列接続または直列接続でできた回路エレメントである。

(もっと読む)

レベルシフト回路並びにレベルシフト回路を備えたインバータ装置

【課題】VM電位のdv/dtに起因する上アーム電力用スイッチング素子の誤動作を抑制できるレベルシフト回路並びにこれを備えたインバータ装置を提供する。

【解決手段】支持体Si基板上にBOX酸化膜を介しN型Si活性層を形成したSOI基板により構成し、分離酸化膜により分離されN型MOSFETを形成する第1のN型Si活性層、分離酸化膜により分離されP型拡散層による拡散抵抗を形成する第2のN型Si活性層、分離酸化膜により分離され上アーム制御電源の一端側に接続する第4のN型Si活性層から構成され、第1のN型Si活性層を形成する分離酸化膜と第4のN型Si活性層を形成する分離酸化膜は、隣接配置されるとともに、N型MOSFETのドレイン電極と拡散抵抗の第一の電極を接続し、拡散抵抗の第2の電極を上アーム制御電源の他端側に接続した。

(もっと読む)

集積回路装置及び電子機器

【課題】センサーデバイスからの検出信号の精度の高いA/D変換を実現できる集積回路装置及び電子機器等の提供。

【解決手段】集積回路装置は、電源電圧VDDAを生成する電源回路60と、電源回路60から電源電圧VDDAが供給され、供給された電源電圧VDDAに基づいて動作し、電源電圧VDDAにより規定されるA/D変換範囲で、センサーデバイス30からの検出信号に対応する信号についてのA/D変換を行うA/D変換器ADCと、電源回路60から電源電圧VDDAが供給され、供給された電源電圧VDDAをセンサーデバイス30に供給する電源端子PVDAを含む。

(もっと読む)

スイッチ回路装置

【課題】従来技術によるスイッチ回路装置では、ドライバ回路がアンテナ端子とポートとの間に振幅の大きい高周波信号を入力した際に、ドライバ回路内部でリーク電流が発生し、スイッチ回路装置の消費電力が増大する、という問題がある。

【解決手段】ドライバ回路の出力部に、リーク電流抑制回路部を設ける。本発明のスイッチ回路装置によれば、リーク電流抑制回路部が高周波信号の侵入を抑制するので、ドライバ回路は出力状態を保持することが出来て、リーク電流の問題が解決される。

(もっと読む)

信号変換装置、波形測定装置および半導体試験装置

【課題】シングルエンド信号および差動信号を入力してシングルエンド信号を出力するときに、広帯域でノイズや歪みが少ない高品質なシングルエンド信号を出力することを目的とする。

【解決手段】信号変換装置3にパルストランス12を用い、シングルエンド信号を入力したときには、パルストランス12の1次入力側と2次入力側とのうちシングルエンド信号を入力した入力側および1次出力側と2次出力側とのうち何れか一方の出力側をパルストランス12に接続し、差動信号を入力したときには、1次入力側および2次入力側との両方の入力側および1次出力側と2次出力側とのうち何れか一方の出力側をパルストランス12に接続する制御を行っている。

(もっと読む)

レベルシフト回路及びスイッチング電源装置

【課題】dv/dt印加時に誤動作を防止し且つローサイド側からハイサイド側へ信号を伝達し低電圧でも広い範囲で動作するレベルシフト回路。

【解決手段】dv/dt過渡信号が印加され且つ入力信号が入力されないとき第1抵抗R1を含むセット側負荷抵抗R1,R9,MP1のオン抵抗及び第2抵抗R2を含むリセット側負荷抵抗R2,R10,MP2のオン抵抗を第1抵抗及び第2抵抗よりも小さくし、トランジスタMN3がオンである場合にセット信号を生成し且つセット側負荷抵抗をリセット側負荷抵抗よりも大きくし、トランジスタMN4がオンである場合にリセット信号を生成し且つリセット側負荷抵抗をセット側負荷抵抗よりも大きくする制御部MN1,MN2,MP1,MP2,R1,R2,R9,R10、セット信号とリセット信号とに基づいて入力信号をレベルシフトした出力信号を出力するフリップフロップ12を備える。

(もっと読む)

レベルシフト回路及びスイッチング電源装置

【課題】dv/dt印加時に誤動作を防止し且つローサイド側からハイサイド側へ信号を伝達し低電圧でも広い範囲で動作するレベルシフト回路。

【解決手段】トランジスタMN3とトランジスタMN4とをオン/オフさせるパルス発生回路10、第1抵抗R1の両端に第3抵抗R9と非線形特性を有し且つ一定以上のdv/dt過渡信号が印加された場合にオンするダイオードD3〜D6とが接続された直列回路、第2抵抗R2の両端に第3抵抗と同じ抵抗値を有する第4抵抗R10とダイオードとが接続された直列回路、MN3がオンである場合にセット信号、MN4がオンである場合にリセット信号を生成し、MN3のドレインにおける電位とMN4のドレインにおける電位との間において電圧差が生じていない場合にはいずれの信号も生成しない制御部、セット信号とリセット信号とに基づいて入力信号をレベルシフトした出力信号を出力するフリップフロップ12を備える。

(もっと読む)

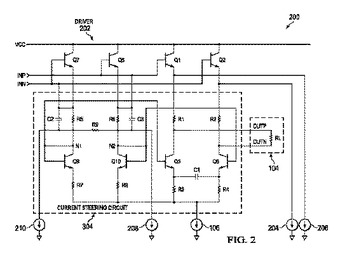

正確な電流ステアリングを備えた低電力高速差動ドライバ

BiCMOSプロセストランジスタを用いる混合又はハイブリッドモードドライバが、ドライバのプルアップ部の電圧に調和するプルダウン電流を生成するため電流ステアリング回路(電圧駆動差動対の代わりに)を有する。ドライバは、速度を速め、生成する出力同相電圧ゆらぎが一層小さい。回路200が、出力端子(OUTP、OUTN)を介して電流を供給して負荷104を駆動するドライバ202(これは、電圧モードと電流モードの組み合わせを用いる)を有する。ドライバ202は、NPNトランジスタ(Q1、Q2、Q7、Q8)、電流源(106、204、206)、及び電流ステアリング回路304を有する。電流ステアリング回路304は、フィードフォワード・レジスタ・キャパシタ(RC)ネットワーク(R5、R6、C2、C3)、入力NPNトランジスタ(Q9、Q10)、出力NPNトランジスタ(Q5、Q6)、電流源(208、210)、レジスタ(Rl〜R4及びR7〜R8)、及びバイパスキャパシタC1を有する。NPNトランジスタはPNPトランジスタで置き換えてもよい。  (もっと読む)

(もっと読む)

PLD回路、集積回路装置及び電子機器

【課題】消費電力を低減できるPLD回路、集積回路装置及び電子機器等を提供すること。

【解決手段】PLD回路は、各トランジスター列が直列接続されたプログラマブルな複数のトランジスターを有する第1〜第m(mは2以上の整数)のトランジスター列TA1〜TAmを含む。第1〜第mのトランジスター列TA1〜TAmの一端に第1の非直流電源VS1が供給される。第1〜第mのトランジスター列TA1〜TAmの各トランジスター列は、複数の入力信号XP(X1P〜XiP)、XN(X1N〜XiN)によってオン・オフされる。第1の非直流電源VS1の電圧により規定される第1のホールド期間に、第1〜第mのトランジスター列TA1〜TAmの他端のノードである第1〜第mのノードNA1〜NAmの電圧レベルを各々出力する。

(もっと読む)

1 - 20 / 82

[ Back to top ]