Fターム[5J081DD24]の内容

LC分布定数、CR発振器 (9,854) | 発振用能動素子とその接続 (1,031) | 素子の接地(高周波接地を含む) (115) | エミッタ・ソース・カソード接地 (61)

Fターム[5J081DD24]に分類される特許

1 - 20 / 61

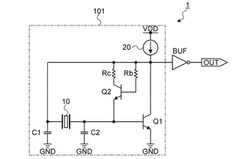

圧電発振器

【課題】ピアース型圧電発振器で高い周波数出力を可能にする。

【解決手段】圧電振動子10の一方の端子と接地電位線GNDとの間に接続された第1の容量素子C1と、圧電振動子10の他方の端子と接地電位線GNDとの間に接続された第2の容量素子C2と、コレクタ端子が圧電振動子10の一方の端子に接続されベース端子が圧電振動子10の他方の端子と電流源20とに接続されエミッタ端子が接地電位線GNDに接続された発振用トランジスタQ1と、ベース端子が発振用トランジスタQ1のコレクタ端子に第1の抵抗Rbを介して接続されコレクタ端子が発振用トランジスタQ1のコレクタ端子に第2の抵抗Rcを介して接続されエミッタ端子が発振用トランジスタQ1のベース端子に接続された発振補助用トランジスタQ2と、を含んで構成される発振回路101と、発振用トランジスタQ1のコレクタ端子に接続されたバッファ回路BUFと、を含む圧電発振器1。

(もっと読む)

高周波発振器

【課題】安定発振、コンパクトなパッケージを実現したSHF帯に好適な高周波発振器を提供する。

【解決手段】低誘電率、低損失の基板材料として水晶板等の耐熱材を最小限の厚さとした基板を主基板2とし、一次実装する能動素子7とIDT3やデスクリート部品8などを主基板2の表裏にそれぞれ配置し、貫通電極6で両面側の間を接続することで配線長を最短とした。LTCCなどの従来の本体基板に代えて薄い水晶等を要部構成部品を実装する主基板とすることにより、薄型化と小型化を実現した。外力・応力に対する脆弱性を、主面側の保護カバーに加えて裏面にも補強カバーを設け、あるいはモールド構造とすることで補強した。

(もっと読む)

電圧制御発振器

【課題】増幅用のトランジスタに帰還容量成分C1及び結合容量成分C2の直列回路を接続したコルピッツ発振回路を用いた電圧制御発振器において、部品点数の削減に寄与できる技術を提供すること。

【解決手段】トランジスタ21のベースに接続された第1の伝送線路41とトランジスタ21のエミッタとアースとの間に接続された第2の伝送線路42と、を備え、第1の伝送線路41及び第2の伝送線路42を互いに接近させて両者の間に線路間容量成分を形成する。この線路間容量成分を前記帰還容量成分C1として利用すると共に第2の伝送線路42とアースとの間に形成される寄生容量成分を前記結合容量成分C2として利用する

(もっと読む)

帰還型発振装置

【課題】設計および製造が容易で、装置のサイズが小さい帰還型発振装置を提供すること。

【解決手段】帰還型発振装置1において、入力端子から入力された信号を増幅して出力端子から出力するバイポーラトランジスタ10と、マイクロストリップラインによって構成され、バイポーラトランジスタの出力端子と入力端子とを結合して出力端子から入力端子に所定の周波数の信号を帰還してバイポーラトランジスタを発振させる結合回路15と、を有する。

(もっと読む)

半導体装置

【課題】CMOSトランジスタによって構成されたVCOを備えた半導体装置において、発振信号の発振振幅のばらつきの抑制および低消費電力化を実現する。

【解決手段】VCO30は、CMOSトランジスタによって構成されたLCタンクVCOと、VCOの発振周波数帯域から一の発振周波数を選択するための周波数選択信号を生成する自動周波数選択回路42と、VCOの制御電圧を生成するPLL32と、周波数選択信号に基づいて差動型のMOSトランジスタのゲートに供給するバイアス電圧を調整するバイアス回路50とを備える。

(もっと読む)

センサのモニタリング装置

【課題】高温環境下でも正常に動作してセンサの測定値を正確に求めることができるようにする。

【解決手段】本発明のモニタリング装置1は、センサ2と、このセンサ2が接続され且つワイドバンドギャップ半導体を使用した発振器を備えたインタフェース3と、インターフェース3とは別に配置され且つインターフェース3から出力された発振信号を処理する演算装置4とを備えている。発振器は、基準となる発振信号を出力する第1発振器6aと、センサ2の出力に基づいて発振信号を出力する第2発振器6bとから構成されている。第演算装置4は、第1発振器6aからの発振信号と第2発振器6bからの発振信号とに基づいてセンサ2で測定した測定値を算出する演算部15とを備えている。

(もっと読む)

発振回路

【課題】小型かつノイズ抑制に優れる発振回路を提供すること。

【解決手段】本発明にかかる発振回路100は、インバータ1及び2、タンク回路3を有する。タンク回路3は、出力ノードOUTTと出力ノードOUTBとの間に並列に接続される。インバータ1は、ドレインが出力ノードOUTBに接続されたn型MISトランジスタM1及びp型MISトランジスタM3を有する。インバータ2は、ドレインが出力ノードOUTTに接続されたn型MISトランジスタM2及びp型MISトランジスタM4を有する。p型MISトランジスタM3及びM4のゲート端子は、それぞれ出力ノードOUTT及びOUTBと直接的に接続される。n型MISトランジスタM1及びM2のゲート端子は、それぞれ結合容量CG1及びCG2を介して出力ノードOUTT及びOUTBと接続され、抵抗CG1及びCG2を介してバイアス電圧VBIASが印加される。

(もっと読む)

高周波二倍波発振器

【課題】本発明は、位相雑音の劣化原因によらず位相雑音を低減できる高周波二倍波発振器を提供することを目的とする。

【解決手段】トランジスタと、該トランジスタのベース側に接続された第一電気信号線路と、該第一電気信号線路に接続され他の端は接地された第一シャントキャパシタと、該トランジスタのコレクタ側に接続された第二電気信号線路と、該第二電気信号線路に接続され他の端は接地された第二シャントキャパシタと、該第一電気信号線路と該第二電気信号線路を接続する大容量キャパシタとを備える。該第一電気信号線路の線路長は、基本波信号の波長の1/4の値を奇数倍した長さから基本波信号の波長の1/16の長さを減算した長さと、基本波信号の波長の1/4の値を奇数倍した長さに基本波信号の波長の1/16の長さを加算した長さとの間の値である。

(もっと読む)

発振器複合回路と半導体装置並びに電流再利用方法

【課題】発振器の不安定動作を回避し低消費電力化を実現する発振器複合装置と方法の提供。

【解決手段】インダクタ(111)と容量(112)を含む共振回路(110)を備えた発振器(100)と、前記発振器の発振出力信号を入力し、且つ、電源側からの電流パスを構成し前記電流パスの前記第1の電源と反対側の一端が前記発振器の前記インダクタ(111)の中点に接続された差動対を含む分周器(200)とを、グランドと電源間に縦積みに配置し、分周器(200)の直流供給電流端子(230)からグランド側に流れる直流電源電流を、発振器(100)の電源電流として再利用する。

(もっと読む)

MOSFETのソースバルク電圧を用いた信号処理ASIC用の温度補償RC発振器

温度補償CMOS RC発振回路は、抵抗と温度相関バイアス電流とを用いてソースバルク電圧を変化させて、温度に対するMOSFETの閾値電圧の変動を安定させる。この温度層間バイアス電流はまた、抵抗を流れる。温度が上昇すると、バイアス電流も増え、MOSFETのソースバルク電圧を上昇させる。上昇したソースバルク電圧は、高い温度にてMOSFETの閾値電圧を安定させるのを補助する。この発振器には省電力ロジックも組み込まれており、低い電力消費で高い周波数が得られる。本発明では、得られる発振器が低出力設計となってしまう高利得オペアンプや高速比較器はなく、他のシステムとともにシングルチップに組み込むことができる。 (もっと読む)

切り替え可能インダクタネットワーク

制御信号に応じて設定可能インダクタンスを有する切換可能インダクタネットワークを提供するための技術。前記切り替え可能インダクタネットワークは、差動モード動作の寄生素子の影響を低減するために完全に対称的なアーキテクチャを採用することができる。前記切り替え可能インダクタネットワークは、特に、マルチモード通信回路への用途、例えば、電圧制御発振器(VCO)またはそのような回路におけるアンプもしくはバッファに適している。 (もっと読む)

発振回路

【課題】高周波発振であっても安定した発振を行なえる。

【解決手段】発振回路1は、圧電振動子を所定の周波数で励振させる発振回路部を備え、発振回路部の等価回路ECは、負性抵抗RLと容量性リアクタンスCLが直接接続された直列モデルで構成されている。発振回路部の一方の端子ECAにコイルLSの一方の端子が直列接続され、発振回路部の他方の端子ECBとコイルLSの他方の端子との間に抵抗RPが並列接続されている。コイルLSの他方の端子と抵抗RPの一方の端子との接続点が、圧電振動子との接続を行う一方の圧電振動子接続用端子Aとされ、抵抗RPの他方の端子と発振回路部の他方の端子ECBとの接続点が、圧電振動子との接続を行う他方の圧電振動子接続用端子Bとされている。また、抵抗RPの絶対値は、負性抵抗RLの絶対値よりも大きい。

(もっと読む)

高周波発振器

【課題】高価な誘電体共振器やバラクタダイオードを使用することなく、廉価に制作することができ、また回路面積が小さく小型化が可能となるようにする。

【解決手段】誘電体基板1上に形成されたマイクロストリップ線路2において、増幅素子3の入力端のゲートが入力端側線路2aに接続され、出力端のドレインが出力端側線路2bに接続され、ソースが接地電極5を介して基板裏面の接地面7に接続される。そして、上記増幅素子3の上面に、例えば棒状の金属体10を絶縁性接着剤9によって接着し、この金属体10をマイクロストリップ線路2の伝送線路方向に配置することで、この金属体10の一方端を入力端側線路2a、他方端を出力端側線路2bに容量性結合する。この金属体の結合は、一端のみでもよい。これによれば、増幅素子3からの出力が、容量C12、インダクタンスL、容量C11を通って入力端へ帰還し、発振が行われる。

(もっと読む)

発振回路及び、その発振回路を用いた無線機

【課題】 信号振幅が大きい高調波信号を提供することができる発振器を提供する。

【解決手段】 一導電型又は逆導電型の第1のMOSトランジスタ20と、第1のMOSトランジスタ20のドレイン端子に接続された負荷素子30と、第1のMOSトランジスタ20のソース端子に接続され、高調波信号を出力する基本発振器40とを備え、第1のMOSトランジスタ20のドレイン端子から、基本発振器40から出力される高調波信号の増幅信号を出力することを特徴とする発振回路。

(もっと読む)

発振回路

【課題】従来の発振回路は、発振信号を増幅させる電流等の影響で発振周波数の高速化が制限されるという問題があった。

【解決手段】本発明にかかる差動発振回路は、帰還ループ回路を備えた差動型の発振回路であって、帰還ループ回路上に縦続接続され、入力された一対の差動入力信号を遅延させて一対の差動出力信号として出力する遅延回路2〜5と、発振回路が発振起動状態か安定状態のいずれかにあるかを検出し、検出結果を示す検出信号VSTPを出力する発振起動検出回路7と、を備える。さらに遅延回路2〜5は、発振起動検出回路7から出力された検出信号VSTPに基づいて、差動出力信号の出力電流値を制御する。このような回路構成により、発振周波数の高速化が可能である。

(もっと読む)

発振器

【課題】周波数を高くしても分布定数線路の線路長を長くできてQ値を向上できるとともに、製造誤差を小さく抑えることができる発振器を提供する。

【解決手段】1波長の線路長であって、両端をグランドに接地した分布定数線路16を有し、この分布定数線路16の一端から1/4波長の位置に設けた第1の中間タップに発振トランジスタ27のべースを接続するようにした。これにより、分布定数線路16の線路長が従来の1/4波長の線路長の分布定数線路より長くなり、その分Q値の向上が図れるとともに、製造誤差を小さく抑えることが可能となる。分布定数線路16の長さを1/2波長としても従来の1/4波長の長さの分布定数線路に比べて2倍長くできる。このようにしてもQ値の向上が図れ、また製造誤差を小さく抑えることが可能となる。

(もっと読む)

コレクタ同調発振器

【課題】 構成が簡単で、高安定で、歪の小さな正弦波を出力するコレクタ同調発振器を提供する。

【解決手段】 トランス1次巻線のインダクタンスをコレクタ同調回路の同調インダクタンスとし、該トランスに出力取り出し用の二次巻線のほかに第3と第4の巻線を設け、第3巻線の電圧はトランジスタのベースに、第4の巻線の電圧はトランジスタのエミッタにそれぞれ正帰還し、ベース・エミッタ間をプッシュプル動作させる。

2つのトランジスタを用いるプッシュプル構成のコレクタ同調発振器では、トランスによる自己帰還はトランジスタのエミッタに、一方、トランジスタのベースには他方のトランジスタのコレクタからそれぞれ帰還し、ベース・エミッタ間をプッシュプル動作させる。

(もっと読む)

フィルタ回路及び電圧制御発振回路

【課題】双方の信号線路の遅延を容易に一致させることができると共に、不要信号を相殺することができる。

【解決手段】この電圧制御発振回路は、発振回路部1と、発振信号を分岐すると共に互いに位相の反転した第1及び第2の信号を別々に出力する出力分波回路2と、出力分波回路2の出力段に並列に接続され同一構成を有し、トラップ周波数が異なるトラップ回路3、4と、トラップ回路の出力を合成する出力再合成回路とを備える。発振回路部1の電圧制御信号をトラップ回路3、4のバラクタダイオード32,34に印加してトラップ回路3、4のトラップ周波数を発振周波数に連動させる。

(もっと読む)

低雑音電圧制御発振器

【課題】 位相雑音特性を改善すると共に周波数可変幅を広くすることができる低雑音電圧制御発振器を提供する。

【解決手段】 振動素子とコンデンサ2がトランジスタ1のコレクタCとエミッタEとの間に直列に接続され、コレクタCとエミッタEとの間にコンデンサ3,4が直列に接続され、コンデンサ3,4の間の電位がトランジスタ1のベースBに印加され、コレクタCとコンデンサ4との間に1ポート回路6が設けられ、コンデンサ3,4に並列に補正用コンデンサ5を接続し、1ポート回路6が、容量を小さく設定できる可変キャパシタと、インダクタンスの値を大きく設定できるインダクタとを備えてインピーダンスの値を比較的大きく設定する同調回路である低雑音電圧制御発振器である。

(もっと読む)

電圧制御発振器、MMIC、および高周波無線装置

【課題】低位相雑音の電圧制御発振器を実現する。

【解決手段】バラクタ2および制御電圧端子3を含む可変共振器を備えた電圧制御発振器であって、当該可変共振器に対して、並列に、長くとも高調波信号の波長の1/4の奇数倍に高調波信号の波長の1/16を加算した長さであり、短くとも高調波信号の波長の1/4の奇数倍に高調波信号の波長の1/16を減算した長さを有する先端開放スタブ5を接続している。この構成により、基本波周波数においては、基本波信号は先端開放スタブ5およびバラクタ2の両者へ伝播するため、高いQ値を実現でき、一方、高調波周波数において、先端開放スタブ5は短絡負荷を有し、高調波信号は全て先端開放スタブ5へと伝播するため、高調波信号による制御電圧Vtの変動が抑制される。

(もっと読む)

1 - 20 / 61

[ Back to top ]