Fターム[5J081EE03]の内容

LC分布定数、CR発振器 (9,854) | 周波数決定素子 (1,325) | 集中定数 (802) | C (374)

Fターム[5J081EE03]に分類される特許

141 - 160 / 374

集積回路

【課題】CR発振回路を構成するコンデンサの充放電切換りタイミングと、論理回路を構成するCMOSインバータに貫通電流が流れるタイミングとをずらすことで、周波数が安定した発振信号を発生する集積回路を提供する。

【解決手段】複数のCMOS素子によって構成された論理回路と、論理回路に、容量素子と抵抗素子の時定数に依存する周波数の発振信号を出力するCR発振回路と、論理回路に入力される発振信号を遅延する遅延回路と、を備え、CR発振回路と電源とを接続する電源配線が、論理回路と電源とを接続する電源配線と接続されている。

(もっと読む)

発振回路

【課題】MOS容量を用いて構成される発振回路において、低電圧動作の場合であっても、電圧変動に対する容量値の変動幅を小さくすることができる発振回路を提供する。

【解決手段】発振回路の負荷容量は、少なくとも1つのPMOSと、少なくとも1つのNMOSとを含むMOS容量を用いて構成されている。PMOSおよびNMOSのゲートは発振回路の発振ノードに接続されている。PMOSのソース、ドレインおよび基板は電源に接続され、NMOSのソース、ドレインおよび基板はグランドに接続されている。

(もっと読む)

正確で安定したLC型基準発振器のための方法、システム、および装置

【課題】周波数の安定性およびジッタの要件を満たしつつ、CMOS技術における既存の最適化プロセスの手順に依拠した集積化の解決手法を利用した、温度に対して非依存型のLC型発振器を提供する。

【解決手段】実質的に温度に非依存のLC型発振器は、温度ヌル位相に実質的に等しい位相でタンク発振を生成するLC発振器タンク10を用いて達成される。該温度ヌル位相は、LC型発振器の出力発振の周波数の温度変化に伴う変動が最小化されるときの、LC発振器タンク10の位相である。該LC型発振器はさらに、該LC発振器タンク10に接続されて、該温度ヌル位相に実質的に等しい位相で該LC発振器タンク10を発振させる周波数安定化回路を含む。

(もっと読む)

半導体集積回路装置

【課題】差動構成のゲートとドレインとのクロスカップリングのための配線の寄生抵抗を低減する。

【解決手段】第1のアクティブ領域から突出した第1の突出部を夫々有する複数の第1のゲートと、第1のアクティブ領域に隣接した第2のアクティブ領域から、第1の突出部の突出方向とは反対の方向に突出した第2の突出部を夫々有する複数の第2のゲートと、複数の第1のゲートの第1の突出部上及び第2のアクティブ領域の全てのドレイン上に形成されて複数の第1のゲートと第2のアクティブ領域の全てのドレインとを接続する第2の共通配線と、複数の第2のゲートの第2の突出部上及び第1のアクティブ領域の全てのドレイン上に形成されて複数の第2のゲートと第1のアクティブ領域の全てのドレインとを接続する第3の共通配線とを具備したことを特徴とする。

(もっと読む)

発振回路

【課題】特にLC発振回路において、インダクタをトランス構造とし、1次側の発振による交流信号を2次側より効率的に取り出し、整流した後に、発振回路の電源に帰還させ、省電力化及び電源を供給しない発振継続を可能とする発振回路を提供する。

【解決手段】所定の飽和時の共振条件を満たし、逆流防止回路を通して直流電源に接続され、第一のインダクタL1とトランス構造を構成する第二のインダクタL2と、第一のインダクタL1と直列に接続された第一のコンデンサC1と、第二のインダクタL2と直列に接続された第二のコンデンサC2と、を備え、第二のインダクタL2から出力された交流電流を整流し発振回路の電源に帰還させ省電力化及び発振継続を可能とする発振増幅器を提供する。これにより、LC発振回路において、電源を切断した後の発振回路の発振継続、あるいは発振回路の低消費電力化、あるいは外部への電力供給が可能となる。

(もっと読む)

半導体装置

【課題】温度信号の製造バラツキが小さく、高精度の温度信号を生成可能な電子回路を提供すること。

【解決手段】本発明は、ピンチオフ状態にせしめられる第1FET(FET1)と、第1FETのソース端子S1に接続されてなる温度信号Vtempを出力する温度信号出力端子と、を具備する電子回路である。本発明によれば、ピンチオフ状態のFETのソース端子から出力される温度信号を用いることにより。製造ばらつきの小さい温度信号を得ることができる。

である。

(もっと読む)

PLL回路

【課題】回路や制御を複雑にすることなく、電圧制御発振回路の発振周波数レンジを広く保持しつつ出力クロックのジッターを低減可能なPLL回路を提供すること。

【解決手段】前段のLPF3から入力される制御電圧信号VCTRLの電位に応じた周波数を有する出力クロックを、制御端子に入力される制御電圧に応じて遅延時間が変化する遅延回路のM個を環状に接続したリングオシレータを用いて発生するVCO回路4aを備えるPLL回路において、VCO回路4aは、制御電圧信号VCTRLから低周波帯域の制御電圧信号VCTRLを抽出する低域通過フィルタを備え、前記リングオシレータは、前記M個の遅延回路のうち、m個(m<M)の各遅延回路の制御端子に制御電圧信号VCTRLが入力され、(M−m)個の各遅延回路の制御端子に制御電圧信号VCTRL2が入力される。

(もっと読む)

発振器の設計方法

【課題】フリッカノイズの影響を考慮し消費電力も考慮して、位相ノイズを低減した発振器を設計する。

【解決手段】発振周波数をfo、規格化周波数をfn、オフセット周波数をΔf、位相ノイズ特性の傾きをNとするとき、オフセット周波数Δfでの目標となる位相ノイズL{Δf}と消費電力Pdとから、(a)式により、目標となる第1の性能指数FOMconを求めておき、シミュレーション、計算、又は実際の測定で求めた位相ノイズL{Δf}と消費電力Pdとから、(b)式により第2の性能指数FOMgenを求め、FOMcom≦FOMgenとなるように発振器を設計する。 (もっと読む)

(もっと読む)

発振器

【課題】内蔵するICチップの内容を外部から設定し、書き換えることで回路定数や回路方式あるいは分周数を実装機器の仕様に合せて切り換え可能とした融通性の高い発振器を提供する。

【解決手段】内蔵するICチップ3に発振回路と共に複数の回路定数や回路方式の回路、あるいは複数の分周数の分周回路を備えると共に、該ICチップに不揮発メモリの領域、あるいは分周回路領域を設け、発振器の回路定数や回路方式を当該不揮発メモリに外部から書き込んだデータで切り換える構成とした。

(もっと読む)

電圧制御発振器

【課題】VCO利得の変動を抑圧した簡易な構成のVCOの提供。

【解決手段】二つの周波数可変手段を具備することでマルチバンド動作を行なう電圧制御発振器(VCO)において、可変容量素子11iaと12ia及び11ibと12ib(i=1、2、3)をそれぞれ互いに極性が逆になる向きに並列接続可能とし、可変容量素子対を形成する。一般に、可変容量素子11iaと12ia、11ibと12ib(i=1、2、3)の容量値は異なる値に設定される。これらの可変容量素子対は、ループコントロール端子3に印加されるコントロール電圧VCNTにより制御されると同時に、帯域設定信号VSW1、VSW2、VSW3によってオンオフされるスイッチ素子であるトランジスタ101a、102a、103a、101b、102b、103bの切替により、VCO本体に電気的に分離・接続される。

(もっと読む)

発振回路装置

【課題】 この発明は、負性抵抗を示す帯域が広くして、使用できる発振周波数を多くすることを目的とするものである。

【解決手段】 この発明の発振回路装置は、相互接続された一対のトランジスタ1、2と抵抗・容量の回路網で構成された発振部100と、発振部100に接続されるループ状の伝送線路で構成された共振部200と、を備え、前記抵抗・容量の回路網の抵抗値及び容量値を前記発振部が第1の周波数帯で負性抵抗となり、その第1の周波数帯より高い周波数帯においてフラットな負性抵抗を示すように設定したことを特徴とする。

(もっと読む)

デジタル制御発振器及びこれを用いた位相同期回路

【課題】発振周波数を線形に近くかつきめ細やかに制御可能なデジタル制御発振器を提供する。

【解決手段】正相発振信号を出力する正端子213と、逆相発振信号を出力する負端子214と、センタータップ210とを有し、正端子とセンタータップとの間の任意の位置に第1の接点211を備え、負端子とセンタータップとの間の第1の接点に対応する位置に第2の接点212を備える差動インダクタ200と、正端子と負端子との間に接続され、第1のデジタル制御コードによってキャパシタンスを2値に変化させる第1の可変キャパシタを複数含む第1の可変キャパシタバンク220と、第1の接点と第2の接点との間に接続され、第2のデジタル制御コードによってキャパシタンスを2値に変化させる第2の可変キャパシタを複数含む第2の可変キャパシタバンク240と、正端子と負端子との間に接続される負性抵抗230とを具備する

(もっと読む)

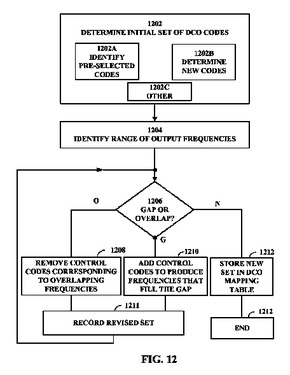

デジタル制御発振器のためのダイナミック較正技法

デジタル制御発振器(DCO)を較正するための技法を開示する。本開示の一態様では、DCOを動作させるための制御コードの初期セットを判断する。初期セットから生成された出力周波数レンジを識別する。周波数レンジにおけるギャップまたはオーバーラップインスタンスを識別する。オーバーラップの場合、修正されたセットを確立するためにオーバーラップインスタンスに対応する制御コードを初期セットから除去する。ギャップの場合、ギャップを充填する周波数値を生成するために、制御コードを初期セットに追加する。同じことを実行するための装置も開示する。  (もっと読む)

(もっと読む)

低雑音電圧制御発振回路

【課題】 出力レベルを低下させることなく、電源雑音の影響を受けないようにして位相雑音の劣化を防止できる低雑音電圧制御発振回路を提供する。

【解決手段】 バッファ段1の増幅用トランジスタTr2と発振段2の発振用トランジスタTr1とをカスケード接続し、Tr2のコレクタには、コイルL1を介して電源電圧Vccが印加されると共に、出力端子Foutが導き出され、Tr2のベースには、抵抗R1と抵抗R2で電源電圧を分圧した電圧が印加されると共に、コンデンサC1の一端が接続され、他端が接地され、Tr1のコレクタには、Tr2のエミッタが接続され、Tr1のベースには、共振回路2aからの出力信号が入力されると共に、抵抗R3と抵抗R4でTr2のエミッタの電圧を分圧した電圧が印加され、Tr1のエミッタには、抵抗R5とコイルL2を介して接地される。

(もっと読む)

発振回路、及びこれを用いた無線受信回路、スイッチ装置

【課題】消費電力の増大と発振周波数調整に要する時間の増大とを低減しつつ、従来よりも発振周波数の調整精度を向上させることが容易な発振回路、及びこれを用いた無線受信回路、スイッチ装置を提供する。

【解決手段】パルス信号PWM1を出力すると共にパルス幅の設定を受け付けるパルス生成部PWMG1と、パルス信号PWM1を平滑して得られた直流電圧Vdc1を出力するローパスフィルタLPF1と、Vdc1を接続点P1に印加する配線25と、パルス信号PWM2を出力すると共にパルス幅の設定を受け付けるパルス生成部PWMG2と、PWM2を平滑して得られた電圧VLP2を出力するローパスフィルタLPF2と、VLP2を所定の比率に変換して直流電圧Vdc2として接続点P2に印加する電圧変換部CNV2と、接続点P1,P2間の電圧に応じた周波数の発振信号を生成する並列共振回路23を備えた。

(もっと読む)

搬送波発振器

【課題】低消費電力および低コストへの要求に応える通信装置を提供する。

【解決手段】任意の周波数の搬送波を生成する搬送波発振器であって、周期信号を生成するエネルギー貯蔵タンク21−1とエネルギー貯蔵タンク21−1に合体され前記周期信号の振幅を増幅するように構成された増幅器21−2とを有し、第1のインピーダンスを示す発振器21と、前記第1のインピーダンスより小さい第2のインピーダンスを示すアンテナ23と、前記発振器21と前記アンテナ23の間に接続され、第3のインピーダンスを提供するように構成されて、前記発振器から前記アンテナに向けて見た場合の前記第2及び第3のインピーダンスの合成インピーダンスが、任意の周波数で前記搬送波を生成するよう前記発振器21を促進するのに充分な大きさとなるようにしたネットワーク22とを備える。

(もっと読む)

半導体集積回路装置

【課題】十分な発振余裕を維持しながら、位相雑音を低減した発振出力を得る。

【解決手段】発振周波数を決定する共振回路(12,L1,Cv)と、前記共振回路に接続されて前記発振周波数の発振出力を出力する発振部を構成する第1のMOSトランジスタM1,M2と、前記第1のMOSトランジスタに並列に接続される第2のMOSトランジスタM3,M4と、前記発振周波数に応じて前記第2のMOSトランジスタをオン,オフさせて前記第1及び第2のMOSトランジスタによる等価的なゲート幅を増減可能とする制御部SW1とを具備したことを特徴とする。

(もっと読む)

電圧制御発振器、並びにそれを用いたPLL回路及び無線通信機器

【課題】C結型の可変容量回路と直結型の可変容量回路とを上手く混在させて構成し、発振周波数の線形性及び可変範囲のバランスがとれた電圧制御発振器を提供する。

【解決手段】本発明の電圧制御発振器は、並列接続されたインダクタ回路110、C結型可変容量回路120及び140、直結型可変容量回路130、及び負性抵抗回路160と、基準電位Vref1及びVref2を生成する基準電位発生部180とを備える。各可変容量回路120、130、及び140の可変容量素子121、122、131、132、141、及び142のバックゲート端子には、発振周波数をフィードバック制御するための制御電位Vtが印加される。C結型可変容量回路120及び140の可変容量素子121、122、141及び142のゲート端子には、基準電位Vref1及びVref2がそれぞれ印加される。

(もっと読む)

VCOのキャパシタバンクのトリミングとキャリブレーション

技法は、電圧制御発振器(VCO)で使用されるキャパシタバンクに関連するキャパシタンスをトリミングするために開示される。実施例では、キャパシタンスはそれぞれ複数の構成要素のキャパシタンスへサブ分割される。実施例では、キャパシタンスはそれぞれ複数の構成要素のキャパシタンスへサブ分割される。構成要素のキャパシタンスは、キャパシタバンクのステップのサイズをトリミングするために選択的にイネーブルされ、またはディスイネーブルされ得る。さらなる技法は、キャパシタバンクについてステップのサイズの誤差を最小化するためにトリミング可能なキャパシタンスをキャリブレートするために開示される。  (もっと読む)

(もっと読む)

インピーダンス変換回路、高周波回路、及びインピーダンス変換回路のインピーダンス変換特性調整方法

【課題】誘電体チップ等の付加や、スタブ長の長いオープンスタブを用いることなく、インピーダンス変換の特性調整を可逆的に且つ微調整可能なようにしたインピーダンス変換回路及びそれを備えた高周波回路を構成する。

【解決手段】スタブST2の長さを固定したままスタブST1の長さを短くすると、インピーダンスZbはアドミッタンスチャート上を矢印A1で代表する方向に移動する。また、スタブST1の長さを固定したままスタブST2の長さを短くすると、インピーダンスZbはアドミッタンスチャート上の等コンダクタンス円上を矢印A2で代表して示すように移動する。したがって図中スミスチャートの中心とショート点とを直径とする円内では、インピーダンス軌跡は、スタブST1,ST2のトリミングによってインピーダンスは互いに可逆的に調整できることになる。

(もっと読む)

141 - 160 / 374

[ Back to top ]