Fターム[5J081FF21]の内容

LC分布定数、CR発振器 (9,854) | 構成要素(発振用能動素子、周波数決定素子以外) (1,204) | 回路素子 (660) | コンデンサ (120)

Fターム[5J081FF21]の下位に属するFターム

温度係数コンデンサ

Fターム[5J081FF21]に分類される特許

41 - 60 / 120

CR発振クロック内蔵マイクロコンピュータ

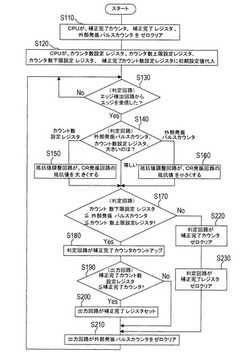

【課題】CR発振クロックの周期調整が完了したかを判定できるCR発振クロック内蔵マイクロコンピュータの提供。

【解決手段】判定回路は、カウント数下限設定レジスタが示す値とカウント数上限設定レジスタが示す値との間に、外部発振パルスカウンタが示す値が収まっているかを判定する(S170)。収まっていると判定すると(S170でYes)、判定回路は、補正完了カウンタに格納されている値に1を足してカウントアップする(S180)。その後、出力回路が、補正完了カウンタのカウント数が補正完了カウント数設定レジスタに格納された値以上であるかを判断する(S190)。以上であると判断すると(S190でYes)、出力回路は、補正完了レジスタに「1」(周期調整が完了したことを示す情報)を入力する(S200)。そして、これらのステップを繰り返す。

(もっと読む)

集積回路

【課題】CR発振回路を構成するコンデンサの充放電切換りタイミングと、論理回路を構成するCMOSインバータに貫通電流が流れるタイミングとをずらすことで、周波数が安定した発振信号を発生する集積回路を提供する。

【解決手段】複数のCMOS素子によって構成された論理回路と、論理回路に、容量素子と抵抗素子の時定数に依存する周波数の発振信号を出力するCR発振回路と、論理回路に入力される発振信号を遅延する遅延回路と、を備え、CR発振回路と電源とを接続する電源配線が、論理回路と電源とを接続する電源配線と接続されている。

(もっと読む)

半導体装置

【課題】温度信号の製造バラツキが小さく、高精度の温度信号を生成可能な電子回路を提供すること。

【解決手段】本発明は、ピンチオフ状態にせしめられる第1FET(FET1)と、第1FETのソース端子S1に接続されてなる温度信号Vtempを出力する温度信号出力端子と、を具備する電子回路である。本発明によれば、ピンチオフ状態のFETのソース端子から出力される温度信号を用いることにより。製造ばらつきの小さい温度信号を得ることができる。

である。

(もっと読む)

高周波発振器

【課題】 低位相雑音の高周波発振器を提供すること。

【解決手段】 能動素子11により増幅された高周波発振源内の雑音電力の一部は、能動素子11の各端子に接続されたリアクタンス回路21、22および共振器31によって能動素子11に戻され、能動素子11によってさらに電力が増幅される。これを繰り返すことで安定した発振波が負荷抵抗41から出力される。

能動素子11のエミッタ端子とリアクタンス回路21との間に装荷された帯域通過フィルタ61の位相特性はリアクタンス回路21の位相特性に加え合わされ、リアクタンス回路21の位相特性を急峻にしたことになる。このため、能動回路51と共振器31を往復したときの位相の傾きが大きくなり周波数選択性が強くなるので、位相雑音は低減する。

(もっと読む)

水晶発振器

【課題】 電源立ち上がり直後にCMOSインバータICの自励発振によって発生する不要波を出力しないようにして、安定した発振器出力を得ることができる水晶発振器を提供する。

【解決手段】 発振部10のCMOSインバータICの後段にNANDゲートIC11を備え、発振部10の出力をNANDゲートIC11の入力端子Aに入力すると共に、入力端子Bに電源電圧を入力し、電源電圧端子と入力端子Bとの間に抵抗R4を直列接続し、抵抗R4と入力端子Bとの間に、一端が接続され他端が接地されたコンデンサC4を設け、電源投入後、CMOSインバータICからの自励発振に由来する不要波が出力されている間は、NANDゲートICに入力される電源電圧がハイレベルとならないよう、抵抗R4及びコンデンサC4による時定数が設定されている水晶発振器としている。

(もっと読む)

低雑音電圧制御発振回路

【課題】 出力レベルを低下させることなく、電源雑音の影響を受けないようにして位相雑音の劣化を防止できる低雑音電圧制御発振回路を提供する。

【解決手段】 バッファ段1の増幅用トランジスタTr2と発振段2の発振用トランジスタTr1とをカスケード接続し、Tr2のコレクタには、コイルL1を介して電源電圧Vccが印加されると共に、出力端子Foutが導き出され、Tr2のベースには、抵抗R1と抵抗R2で電源電圧を分圧した電圧が印加されると共に、コンデンサC1の一端が接続され、他端が接地され、Tr1のコレクタには、Tr2のエミッタが接続され、Tr1のベースには、共振回路2aからの出力信号が入力されると共に、抵抗R3と抵抗R4でTr2のエミッタの電圧を分圧した電圧が印加され、Tr1のエミッタには、抵抗R5とコイルL2を介して接地される。

(もっと読む)

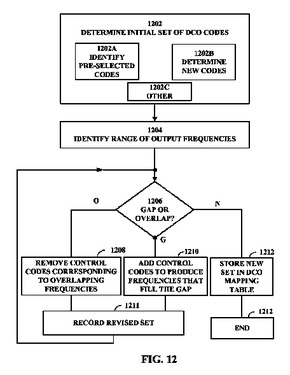

デジタル制御発振器のためのダイナミック較正技法

デジタル制御発振器(DCO)を較正するための技法を開示する。本開示の一態様では、DCOを動作させるための制御コードの初期セットを判断する。初期セットから生成された出力周波数レンジを識別する。周波数レンジにおけるギャップまたはオーバーラップインスタンスを識別する。オーバーラップの場合、修正されたセットを確立するためにオーバーラップインスタンスに対応する制御コードを初期セットから除去する。ギャップの場合、ギャップを充填する周波数値を生成するために、制御コードを初期セットに追加する。同じことを実行するための装置も開示する。  (もっと読む)

(もっと読む)

搬送波発振器

【課題】低消費電力および低コストへの要求に応える通信装置を提供する。

【解決手段】任意の周波数の搬送波を生成する搬送波発振器であって、周期信号を生成するエネルギー貯蔵タンク21−1とエネルギー貯蔵タンク21−1に合体され前記周期信号の振幅を増幅するように構成された増幅器21−2とを有し、第1のインピーダンスを示す発振器21と、前記第1のインピーダンスより小さい第2のインピーダンスを示すアンテナ23と、前記発振器21と前記アンテナ23の間に接続され、第3のインピーダンスを提供するように構成されて、前記発振器から前記アンテナに向けて見た場合の前記第2及び第3のインピーダンスの合成インピーダンスが、任意の周波数で前記搬送波を生成するよう前記発振器21を促進するのに充分な大きさとなるようにしたネットワーク22とを備える。

(もっと読む)

電圧制御発振装置

【課題】高いC/N及び周波数安定度を確保できると共に、周波数可変幅を広くしても帯域外の不要信号の漏れ出しを抑制でき、かつ同時にインピーダンスマッチングもとることができるようにすること。

【解決手段】この電圧制御発振装置は、制御電圧信号に応じて発振周波数が制御される電圧制御発振回路1と、電圧制御発振回路に供給する制御電圧信号を生成するPLL回路2と、電圧制御発振回路1の出力する発振信号を逓倍する逓倍回路3と、逓倍回路3の出力する逓倍信号のうち所定逓倍数の信号を通過させる通過帯域と逓倍回路3に入力した発振信号と同一周波数をトラップするトラップ周波数とが設定された帯域通過フィルタ兼トラップ回路4とを備える。制御電圧信号を分岐して段間結合兼トラップ回路15へ入力し、発振周波数に同期させて段間結合兼トラップ回路15の通過帯域及びトラップ周波数を可変させると共に段間結合量を調整する。

(もっと読む)

インピーダンス変換回路、高周波回路、及びインピーダンス変換回路のインピーダンス変換特性調整方法

【課題】誘電体チップ等の付加や、スタブ長の長いオープンスタブを用いることなく、インピーダンス変換の特性調整を可逆的に且つ微調整可能なようにしたインピーダンス変換回路及びそれを備えた高周波回路を構成する。

【解決手段】スタブST2の長さを固定したままスタブST1の長さを短くすると、インピーダンスZbはアドミッタンスチャート上を矢印A1で代表する方向に移動する。また、スタブST1の長さを固定したままスタブST2の長さを短くすると、インピーダンスZbはアドミッタンスチャート上の等コンダクタンス円上を矢印A2で代表して示すように移動する。したがって図中スミスチャートの中心とショート点とを直径とする円内では、インピーダンス軌跡は、スタブST1,ST2のトリミングによってインピーダンスは互いに可逆的に調整できることになる。

(もっと読む)

マイクロ波発振器

【課題】90度ハイブリッド回路を用いて、低周波の基本周波数から位相雑音特性に優れた高周波出力信号を効率よく取り出すことができるマイクロ波発振器を提供する。

【解決手段】第1の発振器1から基本周波数の第1の発振信号を出力し、第2の発振器2から第1の発振信号に対して逆位相となる基本周波数の第2の発振信号を出力する。90度ハイブリット回路HYB1が、第1の発振器1から出力された第1の発振信号と第2の発振器2から出力された第2の発振信号とを同位相で合成し、出力ポートP5から基本周波数f1の4倍周波数の高周波信号を出力する。このとき、基本周波数f1、2倍の周波数f2、及び3倍の周波数f3の振幅はゼロとなって出力されない。よって、基本周波数f1の4倍周波数の高周波信号は低位相雑音となって出力される。

(もっと読む)

圧電発振器およびリアルタイムクロック

【課題】消費電力を低減すると共に、外部へ出力する発振信号の周波数安定性を良好にした圧電発振器およびリアルタイムクロックを提供する。

【解決手段】圧電発振器10は、圧電振動子12に接続し、発振信号を出力する発振回路14と、発振信号を入力し、且つ、発振信号を外部に出力するか否かを選択する制御信号に基づいて、発振信号を外部に出力するか否かを切り替える出力切替部16と、発振回路14に接続し、発振信号を外部出力しない制御信号を入力すると、発振信号を外部出力するときに比べて負荷容量を小さくする負荷容量可変回路20とを備えた構成である。

(もっと読む)

発振器制御装置

【課題】安定した位相雑音特性を高速に得ることができる発振器制御装置を提供する。

【解決手段】動作電流制御信号に基づく動作電流を供給する可変電流源14を含み、発振器調整ワードに応じた発振周波数の発振信号を出力するデジタル制御発振器1と、前記発振信号と基準信号との間の位相差を算出し、位相差信号を出力する位相差算出部(2,3,4)と、前記デジタル制御発振器の発振周波数を設定するための周波数命令ワードと前記位相差信号との差分を平滑化して、前記発振器調整ワードを出力するフィルタ6と、前記発振器調整ワードを測定し、前記動作電流制御信号を出力する制御部7と、を備え、前記制御部は、前記動作電流の値を変化させるように前記動作電流制御信号を出力し、前記発振器調整ワードが極大値となる前記動作電流の値を抽出し、前記可変電流源が供給する動作電流がこの抽出した値となるように前記動作電流制御信号を出力する。

(もっと読む)

PLL回路

【課題】複数のVCOを切り替えて使用するPLL回路において、VCOの位相雑音を最適化することである。

【解決手段】PLL回路11の複数のVCO12−1〜12−nの内の1つの選択は、VCO選択データにより行われ、キャパシタの選択はVSBデータにより行われる。バイアス電流設定回路25は、VCO選択データとVSBデータと制御電圧のデジタル変換値VTDをデコードして、予め定めたバイアス設定値を可変電流源I1に出力する。

(もっと読む)

発振回路及びテレビジョン信号受信用チューナ

【課題】特別の部品を追加することなく、平衡型の発振回路のC/N特性を改善すること。

【解決手段】VHFローバンド及びVHFハイバンドのテレビジョン信号を受信するための局部発振器を不平衡型の発振回路11,12で構成し、UHFのテレビジョン信号を受信するための局部発振器を平衡型の発振回路13で構成し、VHFバンド用発振回路11,12のC/N特性改善のために設けている抵抗R2の接続点を、UHF用発振回路13に接続した共振回路23のインダクタンス素子23aの一端に接続し、平衡型のUHF用発振回路13に対してラインフィルタ31,32を両側に配置する。

(もっと読む)

発振器

【課題】発振器において、発振周波数可変範囲を狭めることなく位相雑音を低減する。

【解決手段】バイポーラトランジスタTr1のコレクタとベース間にバイアス回路を備える発振器において、電源Vccとコレクタとの間に発振周波数よりも低いベースバンド周波数帯域において十分に高いインピーダンスを示す素子や回路、例えばベースバンドチョークコイル16を接続する。ベースバンド周波数帯域のノイズ信号はチョークコイル16により電源側に漏れることなくバイアス回路を介して負帰還される。チョークコイル16の代わりにカレントミラー回路を設けてもよい。

(もっと読む)

遅延素子、可変遅延線及び電圧制御発振器並びにそれを備えた表示装置及びシステム

【課題】温度が変化しても中心発振周波数が安定している電圧制御発振器等を、簡単な構成で提供する。

【解決手段】入力信号Viに遅延量τdを加えて出力信号Voとする遅延発生部11と、遅延τdを制御する遅延制御部12とを備えている。遅延制御部12は、遅延量τdを調節する第一の制御信号としての制御信号S1を出力する遅延調節回路13と、温度による特性変化を補償する第二の制御信号としての制御信号S2を出力する温度補償回路14とを有し、制御信号S1と制御信号S2とを合成して得た第三の制御信号としての制御信号S3を遅延発生部11へ出力することにより遅延量τdを制御する。遅延制御部12は、遅延調節回路13と温度補償回路14とを直列に接続することにより、制御信号S3を得ている。

(もっと読む)

電圧制御発振器

【課題】同調範囲と位相雑音とは、線路共振器への能動回路と同調回路の接続位置に関する値δで関連づけられており、それぞれの特性がトレードオフの関係にあり、設定の自由度が小さい。そこで、同調範囲と位相雑音の設定の自由度を高めた電圧制御発振器を得ることを目的とする。

【解決手段】線路長が基本波周波数において1/2波長となる両端開放線路からなる線路共振器と、反射利得を有する能動回路と、制御電圧によってリアクタンス値が可変である同調回路と、を備え、前記能動回路を前記両端開放線路の前記基本波周波数におけるショート位置から所定の位相雑音に基づいて選定された波長分θ1隔てた位置で前記両端開放線路に接続し、前記同調回路を前記両端開放線路の前記基本波周波数におけるショート位置から所定の周波数同調範囲に基づいて選定された波長分θ2隔てた位置で前記両端開放線路に接続した。

(もっと読む)

電気的に制御される磁気回路を備えた装置の駆動回路

【課題】

部品の着脱作業を要することなく、簡単に、発振器等磁気回路を備えた装置単体での、周波数特性の検査を可能とした電気的に制御される磁気回路を備えた装置の駆動回路を提供する。

【解決手段】

信号レベル調整部14と積分回路部15とを具備する電気的に制御される磁気回路を備えた装置の駆動回路であって、前記積分回路部がOPアンプ23と、該OPアンプに対して並列に接続されたコンデンサ27と、並列に接続された負帰還用の抵抗28と、該抵抗を前記OPアンプに対して継断するスイッチング手段33,32とを有し、該スイッチング手段が前記抵抗を断状態とすることで、前記積分回路部が積分回路として動作し、前記スイッチング手段が前記抵抗を継状態とすることで、前記積分回路部が増幅回路として動作する様構成した。

(もっと読む)

デュアルバンド結合VCO

2つの電圧制御発信部VCO1、VCO2を備えるデュアルバンド可能電圧制御発振VCO回路において、電圧制御発振部VCO1、VCO2は、少なくとも2つの結合伝送線TL1、TL2を介して同調および接続され、伝送線[TL1、TL2)は、2つの形態のうち1つにしたがって動作して、同調された発振部(VCO1、VCO2)の組み合わせたインダクタンスと電圧制御発振回路(VCO)の発振周波数とを変動させる。 (もっと読む)

41 - 60 / 120

[ Back to top ]