Fターム[5J081FF21]の内容

LC分布定数、CR発振器 (9,854) | 構成要素(発振用能動素子、周波数決定素子以外) (1,204) | 回路素子 (660) | コンデンサ (120)

Fターム[5J081FF21]の下位に属するFターム

温度係数コンデンサ

Fターム[5J081FF21]に分類される特許

21 - 40 / 120

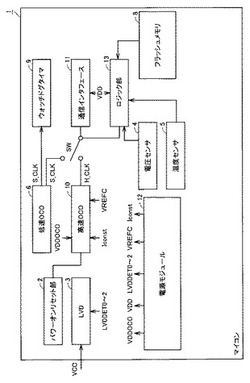

半導体装置

【課題】周囲温度や外部電源電圧の変化による高速OCOに与える参照電圧および参照電流の変動を防止し、電源モジュールの回路面積が小さい半導体装置を提供する。

【解決手段】高速OCO10は、参照電流および参照電圧で定まる大きさの高速クロックを出力する。温度センサ5は、高速OCO10の周囲温度を検出し、電圧センサ4は、高速OCO10の動作電圧を検出する。電源モジュール12は、BGRを含み、BGRが出力する基準電圧に基づいて、参照電圧、参照電流、高速OCOの動作電圧を生成する。フラッシュメモリ8は、高速OCO10の周囲温度および動作電圧に対応する、参照電圧および参照電流のトリミングコードを定めたテーブルを記憶する。ロジック部13は、検出された周囲温度および動作電圧に対応する参照電圧および参照電流のトリミングコードに基づいて、参照電流および参照電圧の値を調整する。

(もっと読む)

周波数逓倍器装置及びその操作方法

【課題】本発明は、従来の周波数逓倍器による悪い高調波抑圧比を改善し、又、周波数逓倍器からの発振周波数は、他の高調波に妨害されにくいため、周波数逓倍器装置及びその操作方法を提供することを目的とする。

【解決手段】本発明の周波数逓倍器装置は、高調波発生器、高調波抑制器及び特定高調波応用装置を含んでいる。前記高調波発生器は、基本周波数を有する入力信号を受信して、第一高調波信号成分及び第二高調波信号成分を含む高調波信号を発生させる。前記高調波抑制器は、前記高調波信号を受信して、前記第一高調波信号成分を抑制し、前記第二高調波信号成分を高める。前記周波数逓倍器装置は、高められた前記第二高調波信号成分を受信する。

(もっと読む)

高周波二倍波発振器

【課題】本発明は、位相雑音の劣化原因によらず位相雑音を低減できる高周波二倍波発振器を提供することを目的とする。

【解決手段】トランジスタと、該トランジスタのベース側に接続された第一電気信号線路と、該第一電気信号線路に接続され他の端は接地された第一シャントキャパシタと、該トランジスタのコレクタ側に接続された第二電気信号線路と、該第二電気信号線路に接続され他の端は接地された第二シャントキャパシタと、該第一電気信号線路と該第二電気信号線路を接続する大容量キャパシタとを備える。該第一電気信号線路の線路長は、基本波信号の波長の1/4の値を奇数倍した長さから基本波信号の波長の1/16の長さを減算した長さと、基本波信号の波長の1/4の値を奇数倍した長さに基本波信号の波長の1/16の長さを加算した長さとの間の値である。

(もっと読む)

電圧制御発振回路

【課題】電圧制御発振回路の回路規模の増大を抑制する。

【解決手段】電圧制御発振回路は、発振信号を増幅する発振アンプ部32と、発振信号の発振周波数を制御するLC共振部33と、負性抵抗成分を有する負性抵抗部34と、を備える。LC共振部33は、ループ状に接続されたgmセル25,26と、ループ上のノードに一端が接続された容量28〜31と、を有し、gmセル25,26と容量28,29とに基づくインダクタンス値と、容量30,31の容量値と、に基づいて発振周波数を制御する。

(もっと読む)

電圧制御発振器

【課題】マイクロストリップラインのトリミングによってQ値の劣化を招くことなく、各種の周波数帯への調整を可能とする。

【解決手段】電圧制御発振器は、発振用トランジスタのベースに接続された共振回路を有しており、この共振回路には、バラクタダイオードとともにマイクロストリップライン10が設けられている。マイクロストリップライン10は、その一端が制御端子に接続されており、他端がビア7を介してグランド電極に接続されている。またマイクロストリップライン10は、その一端に位置する入力導体部10bから他端に位置する接地導体部10eに至る導電路がスパイラル形状をなしており、導電路の途中が粗調用導電体10aを介してグランドに接続されている。

(もっと読む)

高周波発振回路

【課題】発振回路の発振周波数を広帯域に制御可能でIC化に適した比較的小規模な発振回路を提供する。

【解決手段】一方の電源に接続される電流源と、他方の電源に接続されて誘導起電力によって電流を変動させる1組の負荷インダクタと、前記電流源と前記負荷インダクタとそれぞれに結合する1組の差動回路と、前記一方の差動回路の入力と前記他方の差動回路の出力との間に抵抗値を制御可能な可変抵抗を備えて正帰還が掛るように構成されて、前記可変抵抗の抵抗値に対応して発振周波数が定まる高周波発振回路である。

(もっと読む)

電圧制御発振器

【課題】電源電圧に重畳されたノイズにより発生する発振器の位相雑音を低減することができ、しかも簡単な回路構成で実現でき、発振器の小型化を図ることのできる電圧制御発振器を提供すること。

【解決手段】この電圧制御発振器1は、直流電源端子16にコレクタが接続された発振用トランジスタ11と、発振用トランジスタ11のエミッタ・接地間に接続された第1の抵抗21と、発振用トランジスタ11のベース・接地間に接続された共振回路27と、発振用トランジスタ11のエミッタと第1の抵抗21との接続点と直流電源端子16とを接続する結合ラインL1上に設けられた第1のキャパシタ22とを具備することを特徴とする。

(もっと読む)

低雑音電圧制御発振回路

【課題】 電源雑音を除去し、低周波雑音の特性を良好にできる低雑音電圧制御発振回路を提供する。

【解決手段】 駆動用トランジスタQ1 のベースとGNDの間にコンデンサC11を設けることで、そのベースに入力される低周波ノイズを除去でき、駆動用トランジスタQ1 をhFEの低いトランジスタとすることで、電源から入力される低周波ノイズを除去することができ、発振用トランジスタQ2 のエミッタ側に、コイルL3 を設けることで、周波数特性を広域化して位相雑音の周波数特性を良好にでき、発振用トランジスタQ2 のエミッタ側に、コンデンサC7 とコイルL3 で構成される共振回路における共振周波数をVCOの発振周波数帯域の中心辺りに設定することで、ノイズの影響を受けにくい発振周波数にすることができる低雑音電圧制御発振回路である。

(もっと読む)

電圧制御発振器

【課題】電源ラインなどから入力する外来ノイズの影響を低減できる電圧制御発振器を提供すること。

【解決手段】

発振トランジスタ11のベース・エミッタ間に第1の帰還コンデンサ12を接続し、発振トランジスタ11のエミッタ・コレクタ間に第2の帰還コンデンサ13を接続し、発振トランジスタ11のベース・コレクタ間にインダクタ14を接続してコルピッツ発振回路を構成する。発振トランジスタ11のコレクタと直流電源端子18との間にコレクタバイアス抵抗30を接続し、コンデンサ19を介してコレクタバイアス抵抗30の一端を接地する。発振トランジス11のコレクタとベースとの間にチョークインダクタ31とコンデンサ32とが直列に接続されたフィルタ回路を接続する。

(もっと読む)

発振回路

【課題】コンデンサへの充放電及び差動対を使用した発振回路において、回路規模や消費電力の増大を抑制しつつ安定した発振を可能とする。

【解決手段】トランジスタM10は、トランジスタM1,M2からなる差動対に定電流i1を供給する。M1には直列に抵抗R1が接続され、M1とR1との接続点の電位VBがM2のゲートに印加される。一方、M1のゲートには、定電流i2を生じるトランジスタM4と抵抗R2及びコンデンサC1の並列接続体との接続点の電位VAが印加される。M4は、M2のオフ期間に定電流i2を供給し、オン期間に定電流の供給を停止する。抵抗R2,R1それぞれの抵抗値をr2,r1として、(r1・i1)=(r2・i2)を満たすように設定する。

(もっと読む)

ウイーンブリッジ発振回路の自動利得制御回路

【課題】ウイーンブリッジ発振回路の自動利得制御回路を、低コストで実現する。

【解決手段】ウイーンブリッジ発振回路を構成するオペアンプの出力を、抵抗3により電流に変換してNPN型バイポーラトランジスタ1のベースに入力し、NPN型バイポーラトランジスタ1のコレクタとエミッタ間の抵抗値を増減することにより、抵抗2と抵抗4とNPN型バイポーラトランジスタ1による合成抵抗を増減し、オペアンプの利得を増減する。

(もっと読む)

自動調整発振器

【課題】チャージポンプを用いずに、出力周波数の精度を高くすることのできる自動調整発振器を提供する。

【解決手段】発振器10は、発振回路11、第1電圧供給回路13、第2電圧供給回路14及び調整値生成回路16を備えている。第1電圧供給回路13は、基準時間で第1電圧V1が基準電圧Vrefに到達するような時定数となる抵抗値の抵抗器R1とキャパシタン

スのキャパシタC1とを備える。第2電圧供給回路14は、発振回路11の周波数に応じたパルス信号S1,S2によってスイッチングを行なう第1及び第2スイッチング手段SW1,SW2によって第2電圧V2を上昇させる。調整値生成回路16は、第2電圧V2が第1電圧V1よりも先に基準電圧Vrefになった場合には、周波数を低くする調整値を

発振回路11に供給し、第2電圧V2が第1電圧V1よりも遅れて基準電圧Vrefになっ

た場合には、周波数を高くする調整値を発振回路11に供給する。

(もっと読む)

高周波発振器

【課題】高価な誘電体共振器やバラクタダイオードを使用することなく、廉価に制作することができ、また回路面積が小さく小型化が可能となるようにする。

【解決手段】誘電体基板1上に形成されたマイクロストリップ線路2において、増幅素子3の入力端のゲートが入力端側線路2aに接続され、出力端のドレインが出力端側線路2bに接続され、ソースが接地電極5を介して基板裏面の接地面7に接続される。そして、上記増幅素子3の上面に、例えば棒状の金属体10を絶縁性接着剤9によって接着し、この金属体10をマイクロストリップ線路2の伝送線路方向に配置することで、この金属体10の一方端を入力端側線路2a、他方端を出力端側線路2bに容量性結合する。この金属体の結合は、一端のみでもよい。これによれば、増幅素子3からの出力が、容量C12、インダクタンスL、容量C11を通って入力端へ帰還し、発振が行われる。

(もっと読む)

スプリット遅延ライン発振器における装置、システム及び方法

【課題】安全なデータ伝送を行うスプリット遅延ライン発振器における装置、システム及び方法を提供すること。

【解決手段】安全なデータ伝送を行うスプリット遅延ライン発振器における本装置は、第1装置における第1の変調/復調ブロックを有し、その第1の変調/復調ブロックは、第1の可変遅延を設定し、第1の変調/復調ブロックを通過する共有キャリア信号の周波数を変調し、第2装置における第2の変調/復調ブロックは、第2の可変遅延を設定し、第2の変調/復調ブロックを通過する共有キャリア信号の周波数を変調し、第1及び第2装置は、周波数変調された共有キャリア信号にデータを与えることで、共有する秘密情報を作成する。

(もっと読む)

発振回路及び、その発振回路を用いた無線機

【課題】 信号振幅が大きい高調波信号を提供することができる発振器を提供する。

【解決手段】 一導電型又は逆導電型の第1のMOSトランジスタ20と、第1のMOSトランジスタ20のドレイン端子に接続された負荷素子30と、第1のMOSトランジスタ20のソース端子に接続され、高調波信号を出力する基本発振器40とを備え、第1のMOSトランジスタ20のドレイン端子から、基本発振器40から出力される高調波信号の増幅信号を出力することを特徴とする発振回路。

(もっと読む)

発振器

【課題】高い発振周波数で動作する場合であっても、十分なストリップライン長を確保することができ、製造誤差によるバラつきを防止すると共に、Qの低下を防止すること。

【解決手段】発振器10は、発振トランジスタ2と、前記発振トランジスタ2のベース−エミッタ間に設けられる第1の帰還コンデンサ4と、前記発振トランジスタ2のコレクタ−エミッタ間に設けられる第2の帰還コンデンサ5と、前記発振トランジスタ2のベースに一端が接続される共振用ストリップライン13と、前記発振トランジスタ2のエミッタ−グラウンド間に設けられるトラップ回路20と、を備え、前記共振用ストリップライン13は、発振周波数において高次共振モードとなる長さを有し、前記トラップ回路20は、前記高次共振モードより低次側の低次共振モードに相当する周波数の信号を減衰させるものである。

(もっと読む)

コレクタ同調発振器

【課題】 構成が簡単で、高安定で、歪の小さな正弦波を出力するコレクタ同調発振器を提供する。

【解決手段】 トランス1次巻線のインダクタンスをコレクタ同調回路の同調インダクタンスとし、該トランスに出力取り出し用の二次巻線のほかに第3と第4の巻線を設け、第3巻線の電圧はトランジスタのベースに、第4の巻線の電圧はトランジスタのエミッタにそれぞれ正帰還し、ベース・エミッタ間をプッシュプル動作させる。

2つのトランジスタを用いるプッシュプル構成のコレクタ同調発振器では、トランスによる自己帰還はトランジスタのエミッタに、一方、トランジスタのベースには他方のトランジスタのコレクタからそれぞれ帰還し、ベース・エミッタ間をプッシュプル動作させる。

(もっと読む)

電圧制御発振回路

【課題】発振周波数を制御するPLL回路で生成可能な制御電圧の最大値を低電圧化しても、可変容量ダイオードに印加される電圧の可変範囲を広げることができ、しかも簡単な回路構成で実現でき、発振器の小型化を図ること。

【解決手段】この電圧制御発振回路1は、発振用トランジスタ2と、可変容量ダイオード16を有し発振用トランジスタ2に接続された共振回路13と、電源電圧が印加される電源端子T2とグラウンドとの間に介挿されると共に可変容量ダイオード16に対して並列に接続されたコレクタ抵抗RCと、コレクタ抵抗RCのグラウンド側の端部とグラウンドとの間に介挿され発振周波数を制御する制御電圧が印加される制御用トランジスタ21とを具備する。

(もっと読む)

PLL回路

【課題】PLL回路において、アナログ回路のデジタル化によって生じる量子化雑音を抑制することができる技術を提供する。

【解決手段】基準信号REFと分周後の信号DIVとの位相及び周波数を比較してデジタル値に変換するデジタル位相周波数比較器(DPFD)101と、デジタル位相周波数比較器101の出力から高周波雑音成分を除去するデジタルループフィルタ(DLF)102と、デジタルループフィルタ102の出力のデジタル値をアナログ値に変換するデジタルアナログ変換器(DAC)105と、デジタルアナログ変換器105の出力から高周波雑音成分を除去するアナログフィルタ(AnF)106と、アナログフィルタ106の出力に基づいて周波数が制御される電圧制御発振器(VCO)103と、電圧制御発振器103の出力を分周し、分周後の信号DIVを出力する分周器(DIV)104とを備える。

(もっと読む)

フィルタ回路及び電圧制御発振回路

【課題】双方の信号線路の遅延を容易に一致させることができると共に、不要信号を相殺することができる。

【解決手段】この電圧制御発振回路は、発振回路部1と、発振信号を分岐すると共に互いに位相の反転した第1及び第2の信号を別々に出力する出力分波回路2と、出力分波回路2の出力段に並列に接続され同一構成を有し、トラップ周波数が異なるトラップ回路3、4と、トラップ回路の出力を合成する出力再合成回路とを備える。発振回路部1の電圧制御信号をトラップ回路3、4のバラクタダイオード32,34に印加してトラップ回路3、4のトラップ周波数を発振周波数に連動させる。

(もっと読む)

21 - 40 / 120

[ Back to top ]