Fターム[5J081FF21]の内容

LC分布定数、CR発振器 (9,854) | 構成要素(発振用能動素子、周波数決定素子以外) (1,204) | 回路素子 (660) | コンデンサ (120)

Fターム[5J081FF21]の下位に属するFターム

温度係数コンデンサ

Fターム[5J081FF21]に分類される特許

61 - 80 / 120

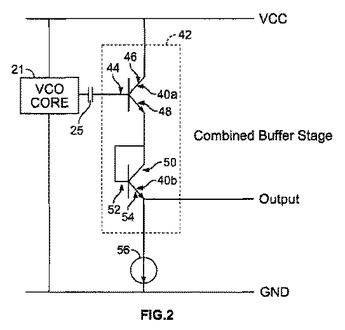

カスケード接続されたエミッタフォロワバッファ段を有する電圧制御発振器

電圧制御発振器(VCO)は出力バッファを有し、これは、第1のトランジスタを含む第1のバッファ段と、第2のトランジスタを含む第2のバッファ段とを備えている。第1および第2のトランジスタはカスケード接続されたエミッタフォロワバッファ回路として配置されている。  (もっと読む)

(もっと読む)

電圧制御発振器

【課題】広い周波数範囲で安定して動作する電圧制御発振器を提供する。

【解決手段】電圧制御発振器11の差動増幅器12の出力を入力側に帰還する帰還キャパシタC1と、帰還キャパシタC1と差動増幅器12の入力端子の接続点に一端が接続され、他端が接地された可変容量素子VCを有する。電圧制御発振器11の発振周波数が変更されると、制御部13は、可変容量素子VCに印加する電圧を制御してその容量値を変化させ、電圧制御発振器11のオープンループゲインがほぼ一定になるようにする。

(もっと読む)

半導体集積回路

【課題】チップ占有面積が小さく低消費電力の広帯域RF信号処理回路を提供すること。

【解決手段】半導体集積回路は、第1制御端子101の第1制御信号Vc1により制御可能なキャパシタンスCRを有する第1キャパシタ1と、第2制御端子102の第2制御信号Vc2により制御可能なキャパシタンスCLを有する第2キャパシタ3を含み等価的にインダクタLをエミュレートするジャイレータ2、5とからなる共振回路を半導体チップに具備する。キャパシタンスCRとインダクタLは、並列共振回路を構成する。並列共振周波数を変更する際に、第1と第2のキャパシタ1、3のキャパシタンスを協調的に変更する。並列共振回路は増幅素子Q1の出力電極に接続されるアクティブ負荷に好適である。

(もっと読む)

誘電体共振器型発振器及びそれを用いたレーダシステム

【課題】誘電体共振器型発振器(DRO)の量産においては、誘電体共振器を設置する位置を高い精度で調節する必要があり、組立作業に要する時間が増大してしまう。また、誘電体共振器と電磁的に結合させ、共振器を構成する伝送線路の先端の終端抵抗および接地手段を誘電体基板上に形成すると製造コストが高くなる。

【解決手段】DROの構成部品のうち、伝送線路のみを誘電体基板上に形成し、MMICチップ上の発振用能動素子、終端抵抗および接地手段を伝送線路と金属ワイヤ、金属リボン等で接続する。また、誘電体共振器から見て発振用能動素子側の伝送線路の中途に、オープンスタブを形成する。

(もっと読む)

温度安定化発振器及び同発振器を含む近接スイッチ

【課題】発振器の温度依存性を簡単に安定化すると共に、大きな切換え距離を有して広い温度範囲に渡って安全に機能する近接スイッチの簡単で低コストの製造を可能にする。

【解決手段】共振回路L,C,RCUと仮想負性抵抗として接続される増幅器回路V,R1,R2,R3を含む発振器において、直流電流源I1は、共振回路L,C,RCUと直列に接続されている。こうして、発振器回路コイルLの抵抗の尺度である電流UCUがもたらされる。この信号UCUを使用することによって、制御回路V1,Mは、発振器回路コイルLの抵抗RCUに逆比例する仮想負性抵抗を制御する。

(もっと読む)

発振器

【課題】発振器を構成するMOSトランジスタのソース側に生じる熱雑音を低減できるようにする。

【解決手段】増幅用トランジスタM1,M2のソースとゲートとの間に帰還ルートを設け、当該帰還ルート上に帰還用トランジスタM3,M4を接続することにより、増幅用トランジスタM1,M2のソース側に生じるノイズが、帰還用トランジスタM3,M4によって位相が反転した信号とされ、位相反転した状態で増幅用トランジスタM1,M2のゲートに帰還されるようにして、増幅用トランジスタM1,M2のソースに発生するノイズを、これと略反転した位相の信号によって打ち消すことができるようにする。

(もっと読む)

制御装置

【課題】低電力損失、低ノイズで被制御信号に対する制御ができる。

【解決手段】制御入力端子8に入力された制御信号17による+電位及び制御出力端子9に制御信号18による−電位が、電圧制御可変コンデンサ21の電圧制御可変コンデンサ1(C1〜C4)の各電極に抵抗器Rを介して供給される。すると、電圧制御可変コンデンサ21(C1〜C4)の各電極間の+電位及び−電位による制御信号により、各電極間の電圧制御可変コンデンサ21の容量が変化する。従って、この変化した容量及びAC入力15による電位に応じた電界が制御信号の電圧に影響なく発生する。

(もっと読む)

発振回路

【課題】発振周波数精度が高い発振回路を提供する。

【解決手段】発振回路1は、基準電流を発生する基準抵抗RE1と、基準抵抗RE1と別個に設けられ、基準抵抗RE1に電流を供給するオペアンプAMP1と、基準抵抗RE1に印加する基準電圧VREFを決定する基準電圧発生回路24と、定電圧VREGを発生する定電圧回路21とを有し、基準電流と定電圧VREGとに基づいて発振周波数を定める集積回路2と、基準抵抗RE1の温度依存性と同じ温度依存性となるように、基準電圧発生回路24の出力する基準電圧VREFの温度依存性を設定する設定レジスタ25と、を有する。

(もっと読む)

電圧制御発振器、並びにそれを用いたPLL回路及び無線通信機器

【課題】より容易に広い制御電位の範囲にわたって発振周波数の線形性が高い電圧制御発振器を提供する。

【解決手段】本発明の電圧制御発振器は、並列接続されたインダクタ回路、n個の可変容量回路、及び負性抵抗回路と、電源電位からn個の基準電位を生成する基準電位発生部114とを備える。n個の可変容量回路の可変容量素子の一方端子には、n個の基準電位のいずれかがそれぞれ入力される。n個の可変容量回路の可変容量素子の他方端子には、発振周波数をフィードバック制御するための制御電位Vtが共通入力される。そして、第1〜第3の可変容量回路A〜Cの一方端子には、第1〜第3の基準電位Vref1〜3がそれぞれ入力される。この第1〜第3の基準電位Vref1〜3はそれぞれ固定で、かつ、第1の基準電位Vref1と第2の基準電位Vref2の電位差と、第2の基準電位Vref2と第3の基準電位Vref3との電位差が異なっている。

(もっと読む)

発振信号出力回路

【課題】低消費電力化を行っても出力部のトランジスタを確実に動作させ、出力信号を確実に出力させる発振信号出力回路を提供する。

【解決手段】バイアス回路110からバイアス電圧を増幅部130、発振部120に印加して発振信号を出力し、発振信号の出力信号XTBを容量結合し、出力信号XTBをバイアス電圧でかさ上げし、出力信号XTP、XTNを生成する。生成された出力信号XTP、XTNを出力段150のPMOSトランジスタMP4A、NMOSトランジスタMN4Aに入力し、稼動させる。出力信号XTP、XTNの電圧が同時に下がれば、電圧が下がり、電流も下がるのでH側が出力され、出力信号XTP、XTNの電圧が同時に上がれば、電圧が上がり、電流も上がるのでL側が出力される。従って、出力段150は大きな利得を得て確実に動作し、閾値電圧がばらついても、バイアス電圧が変化し、確実に出力信号を出力する。

(もっと読む)

発振器

【課題】小型で低コストであり、かつ負荷変動、高調波レベルおよびC/N比を改善することが可能な発振器を提供する。

【解決手段】発振器は、第1発振周波数の第1発振信号を第1中間ノードN1を介し出力端子Toutに出力する第1発振部10と、絶縁層を有し、第1発振部10を実装する実装部と、絶縁層に設けられ、第1中間ノードN1とグランドとの間に結合された第1線路S11と、絶縁層に設けられ、第1中間ノードN1と電源端子Tbとの間に結合された第2線路S21と、絶縁層に設けられ、第1中間ノードN1と出力端子Toutとの間に結合された第3線路S31と、を具備する。

(もっと読む)

位相ノイズを制御する電圧制御発振器及びその利用方法

【課題】位相ノイズを制御する電圧制御発振器及びその利用方法を提供する。

【解決手段】電源電圧に対応する発振周波数を持つ第1出力信号を生成する電圧制御発振部と、それぞれの第1出力信号の伝達コンダクタンス成分をn(nは自然数)次微分した値を増幅する増幅部と、を備え、電圧制御発振部の出力端及び増幅部の出力端は連結されており、それぞれの出力端に、それぞれの第1出力信号が増幅された第2出力信号が出力される電圧制御発振器。これにより、矩形波と類似した形態の波形を持つ出力信号を出力することによって、電圧制御発振器の出力信号の位相ノイズを効率的に減少させることができる。

(もっと読む)

自動式の自己トリミングを有する聴取装置及び対応する方法

【課題】聴取装置のLC共振回路を所望の周波数範囲で持続的に作動させる。

【解決手段】発振器L、Cresと発振器の発振周波数をトリミングするためのトリミング装置11、12とを有する聴取装置において、予め与えられた目標値に依存してトリミング装置11、12を用い発振器の発振周波数を自動的に調節するための調節装置17、18、19を有する。

(もっと読む)

発振器

【課題】消費電力が小さく、C/N特性を向上させた電圧制御発振器を提供する。

【解決手段】発振器は、制御端子Taにチョーク用インダクタL1を介しカソードが結合した第1可変容量ダイオードD11と、第1可変容量ダイオードのアノードとグランドとの間に接続された第1キャパシタC31および線路S4(第1インダクタ)を有する第1共振回路10と、制御端子にチョーク用インダクタL1を介しカソードが結合した第2可変容量ダイオードD12と、第2可変容量ダイオードのアノードとグランドとの間に接続された第2キャパシタC42および第2インダクタL42と、を有する第2共振回路20と、第1共振回路および第2共振回路に結合され、発振信号を出力する発振回路30と、を具備し、第1共振回路により共振周波数をほぼ決定し、第2共振回路で、C/N特性が向上するように調整する。

(もっと読む)

発振器

【課題】発振周波数毎の出力信号の電力及びC/N比の変動を抑制する発振器を提供すること。

【解決手段】

本発明は、それぞれ異なる発振周波数の発振信号を出力する複数の発振部11〜1nと、複数の発振部11〜1nのそれぞれの出力が結合し、出力端子Toutの出力インピーダンスに対応する特性インピーダンスを有する伝送線路15と、伝送線路15と出力端子Toutとの間に接続されているローパスフィルタ18と、を具備する発振器である。

(もっと読む)

高周波発振器

【課題】高周波発振器全体の物理的サイズを変えることなく、且つ位相雑音特性を劣化せずに出力電力が増大する高周波発振器を提供する。

【解決手段】高周波発振器は、能動素子(5)の出力側の信号線路に基本波反射スタブ(9)を取り付けた高調波取り出し型の高周波発振器において、上記基本波反射スタブ(9)と出力端子(4)の間に介設され、高調波出力端子側負荷インピーダンスを高調波出力電力が最大になる予め求められた最適値に変換する高調波インピーダンス変換回路(3)を備える。

(もっと読む)

電圧制御発振器、並びにそれを用いたPLL回路及び無線通信機器

【課題】複数の可変容量回路を用いることなく、広い制御電位の範囲で制御電位に対する発振周波数の変化割合の線形性が高い電圧制御発振器を提供する。

【解決手段】電圧制御発振器100は、インダクタ101及び102を含むインダクタ回路と、両端子の電位差によって容量値を変化させる可変容量素子111及び112と直流成分を遮断するための容量性素子113及び114とを含み、インダクタ回路と並列に接続される可変容量回路110と、発振トランジスタ103及び104がクロスカップリング接続された負性抵抗回路と、出力する基準電位を時間に応じて異なる2つ以上のレベルにシフトさせる時間切換えレベルシフト回路108とを備える。接続点Aには発振周波数を制御するための制御電位Vtが印加され、接続点B及びCには時間切換えレベルシフト回路108が出力する基準電位Vrefが抵抗115及び116を介して印加される。

(もっと読む)

電圧制御発振器、電圧制御発振器用のバイアス装置、電圧制御発振器のバイアス調整プログラム

【課題】定常時の位相雑音を抑制しかつその抑制状態への移行を速やかに行うことが可能な電圧制御発振器、並びに電圧制御発振器用のバイアス装置およびバイアス調整プログラムを提供すること。

【解決手段】外部からの制御で電流調整を行い得る第1の素子および第2の素子と、バイアス電流が流されることにより発振動作し、かつ第1の素子によってバイアス電流が調整されている第1の状態および第2の素子によってバイアス電流が調整されている第2の状態において発振動作が可能な発振回路と、第1の状態と第2の状態とを切り替え可能な切り替え回路と、第1の状態におけるバイアス電流を第1の電流として推定する電流推定回路と、第1の電流に応じた第2の電流を第2の状態における発振回路のバイアス電流として流すように第2の素子を制御する制御回路とを具備する。

(もっと読む)

電圧制御発振器

【課題】本発明の課題は、残留位相雑音特性を劣化させることなく、発振周波数の広帯域化を可能とする電圧制御発振器を提供することにある。

【解決手段】本発明は、第1の制御電圧印加端子11に所定の電圧Vc1を印加することにより、所望の周波数を発振する能動回路を備えた電圧制御発振器において、前記能動回路に第2の制御電圧印加端子13から所望の制御電圧Vc2を印加することにより、当該能動回路の自己共振周波数を可変(又は広帯域化)することを特徴とするものである。

(もっと読む)

出力回路を備えた発振回路

【課題】電源電圧を低電圧化した場合においても、発振回路の最終出力波形のデューティー比を50%に調整し易く、且つ、種々の外乱要因によってもデューティー比の変動を少なく抑えることが可能な発振回路を提供する。

【解決手段】振動子、増幅回路及び出力回路を含む発振回路であって、前記増幅回路の入力端子に接続される側の前記振動子の端子と、前記出力回路の入力端子とが接続され、振動子の前記端子と、増幅回路の前記入力端子とが容量を介して接続され、さらに、振動子の前記端子側に、所定の電位をバイアスするためのバイアス回路が接続されている。

(もっと読む)

61 - 80 / 120

[ Back to top ]