Fターム[5J081FF23]の内容

LC分布定数、CR発振器 (9,854) | 構成要素(発振用能動素子、周波数決定素子以外) (1,204) | 回路素子 (660) | 抵抗・サーミスタ・ポジスタ (88)

Fターム[5J081FF23]に分類される特許

21 - 40 / 88

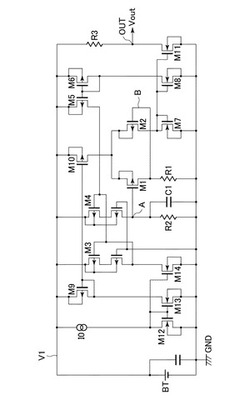

発振回路

【課題】コンデンサへの充放電及び差動対を使用した発振回路において、回路規模や消費電力の増大を抑制しつつ安定した発振を可能とする。

【解決手段】トランジスタM10は、トランジスタM1,M2からなる差動対に定電流i1を供給する。M1には直列に抵抗R1が接続され、M1とR1との接続点の電位VBがM2のゲートに印加される。一方、M1のゲートには、定電流i2を生じるトランジスタM4と抵抗R2及びコンデンサC1の並列接続体との接続点の電位VAが印加される。M4は、M2のオフ期間に定電流i2を供給し、オン期間に定電流の供給を停止する。抵抗R2,R1それぞれの抵抗値をr2,r1として、(r1・i1)=(r2・i2)を満たすように設定する。

(もっと読む)

スプリット遅延ライン発振器における装置、システム及び方法

【課題】安全なデータ伝送を行うスプリット遅延ライン発振器における装置、システム及び方法を提供すること。

【解決手段】安全なデータ伝送を行うスプリット遅延ライン発振器における本装置は、第1装置における第1の変調/復調ブロックを有し、その第1の変調/復調ブロックは、第1の可変遅延を設定し、第1の変調/復調ブロックを通過する共有キャリア信号の周波数を変調し、第2装置における第2の変調/復調ブロックは、第2の可変遅延を設定し、第2の変調/復調ブロックを通過する共有キャリア信号の周波数を変調し、第1及び第2装置は、周波数変調された共有キャリア信号にデータを与えることで、共有する秘密情報を作成する。

(もっと読む)

発振回路及び、その発振回路を用いた無線機

【課題】 信号振幅が大きい高調波信号を提供することができる発振器を提供する。

【解決手段】 一導電型又は逆導電型の第1のMOSトランジスタ20と、第1のMOSトランジスタ20のドレイン端子に接続された負荷素子30と、第1のMOSトランジスタ20のソース端子に接続され、高調波信号を出力する基本発振器40とを備え、第1のMOSトランジスタ20のドレイン端子から、基本発振器40から出力される高調波信号の増幅信号を出力することを特徴とする発振回路。

(もっと読む)

電圧制御発振回路およびクロック信号生成回路

【課題】制御電圧に対する可変容量の容量値の変化の線形性を向上して位相ノイズを低減した電圧制御発振回路の実現。

【解決手段】制御電圧に応じて発振周波数が変化する発振信号OUT,OUTXを出力する電圧制御発振回路において、印加電圧に応じて容量値が変化する複数の可変容量VAC1-VAC4と、制御電圧を分圧して複数の可変容量に印加する分圧電圧VT,VT1-VT3を生成する分圧電圧生成部R1-R4と、を備える。

(もっと読む)

電圧制御発振回路

【課題】発振周波数を制御するPLL回路で生成可能な制御電圧の最大値を低電圧化しても、可変容量ダイオードに印加される電圧の可変範囲を広げることができ、しかも簡単な回路構成で実現でき、発振器の小型化を図ること。

【解決手段】この電圧制御発振回路1は、発振用トランジスタ2と、可変容量ダイオード16を有し発振用トランジスタ2に接続された共振回路13と、電源電圧が印加される電源端子T2とグラウンドとの間に介挿されると共に可変容量ダイオード16に対して並列に接続されたコレクタ抵抗RCと、コレクタ抵抗RCのグラウンド側の端部とグラウンドとの間に介挿され発振周波数を制御する制御電圧が印加される制御用トランジスタ21とを具備する。

(もっと読む)

CR発振クロック内蔵マイクロコンピュータ

【課題】CR発振クロックの周期調整が完了したかを判定できるCR発振クロック内蔵マイクロコンピュータの提供。

【解決手段】判定回路は、カウント数下限設定レジスタが示す値とカウント数上限設定レジスタが示す値との間に、外部発振パルスカウンタが示す値が収まっているかを判定する(S170)。収まっていると判定すると(S170でYes)、判定回路は、補正完了カウンタに格納されている値に1を足してカウントアップする(S180)。その後、出力回路が、補正完了カウンタのカウント数が補正完了カウント数設定レジスタに格納された値以上であるかを判断する(S190)。以上であると判断すると(S190でYes)、出力回路は、補正完了レジスタに「1」(周期調整が完了したことを示す情報)を入力する(S200)。そして、これらのステップを繰り返す。

(もっと読む)

電圧制御発振器

【課題】VCO利得の変動を抑圧した簡易な構成のVCOの提供。

【解決手段】二つの周波数可変手段を具備することでマルチバンド動作を行なう電圧制御発振器(VCO)において、可変容量素子11iaと12ia及び11ibと12ib(i=1、2、3)をそれぞれ互いに極性が逆になる向きに並列接続可能とし、可変容量素子対を形成する。一般に、可変容量素子11iaと12ia、11ibと12ib(i=1、2、3)の容量値は異なる値に設定される。これらの可変容量素子対は、ループコントロール端子3に印加されるコントロール電圧VCNTにより制御されると同時に、帯域設定信号VSW1、VSW2、VSW3によってオンオフされるスイッチ素子であるトランジスタ101a、102a、103a、101b、102b、103bの切替により、VCO本体に電気的に分離・接続される。

(もっと読む)

水晶発振器

【課題】 電源立ち上がり直後にCMOSインバータICの自励発振によって発生する不要波を出力しないようにして、安定した発振器出力を得ることができる水晶発振器を提供する。

【解決手段】 発振部10のCMOSインバータICの後段にNANDゲートIC11を備え、発振部10の出力をNANDゲートIC11の入力端子Aに入力すると共に、入力端子Bに電源電圧を入力し、電源電圧端子と入力端子Bとの間に抵抗R4を直列接続し、抵抗R4と入力端子Bとの間に、一端が接続され他端が接地されたコンデンサC4を設け、電源投入後、CMOSインバータICからの自励発振に由来する不要波が出力されている間は、NANDゲートICに入力される電源電圧がハイレベルとならないよう、抵抗R4及びコンデンサC4による時定数が設定されている水晶発振器としている。

(もっと読む)

振幅一定回路

【課題】本発明の課題は、周波数選択特性を有する回路の出力の振幅をほぼ一定にすることである。

【解決手段】制御回路12は、インダクタL0とキャパシタC0と抵抗R0からなる共振回路にキャパシタC1を並列に接続した場合の共振周波数を予め算出し、その共振周波数において、インピーダンスZがほぼ一定値になるような抵抗値を算出しておく。そして、その抵抗値となるようにスイッチSW3とSW4を切り換えて、抵抗R1、可変抵抗R2を選択する。

(もっと読む)

電圧制御型可変周波数発振回路および信号処理回路

【課題】可変容量素子の容量可変域に応じた広い周波数可変域を確保することができる電圧制御型可変周波数発振回路を提供する。

【解決手段】コイルL1,L2および可変容量素子111,112を有する共振回路101と、負性抵抗回路102とを含む発振回路部103を備える電圧制御型可変周波数発振回路である。発振回路部103と電源電位VDDとの間に第1の抵抗301を設ける。また、発振回路部と接地電位端との間には第2の抵抗302を接続するとよい。

(もっと読む)

電圧制御発振器

【課題】定電流源が有する雑音、電流の増幅及び折り返しのために使用するカレントミラー回路で発生するトランジスタのショット雑音並びにフリッカー雑音の影響を排除することができる共振型の電圧制御発振器を得る。

【解決手段】可変抵抗制御回路12の第1制御回路部21で生成された第1制御信号SR[n−1:0]を可変抵抗7に出力すると共に、可変抵抗制御回路12の第2制御回路部22で生成された第2制御信号DR[m−1:0]を可変抵抗8に出力することにより、発振回路11は、定電流源を有することなく消費電流が一定になり、所望の動作点を得ることができ、定電流源が有する雑音、電流の増幅及び折り返しのために使用するカレントミラー回路で発生するトランジスタのショット雑音並びにフリッカー雑音の影響を排除することができるようにした。

(もっと読む)

電流源回路

【課題】プロセスによる抵抗のバラツキの影響を受けにくい電流源回路を提供する。

【解決手段】上記課題を解決するために、電流源回路100に、MOSトランジスタQ6とQ7のドレイン電圧を入力としそれらの比較の結果を制御部104に出力するコンパレータ103と、コンパレータ103の出力に応じたデジタル制御信号を可変抵抗R1およびR2に出力して両抵抗値を変更する制御部104と、を有する抵抗値制御回路101を備える。

(もっと読む)

発振器

【課題】発振器において、発振周波数可変範囲を狭めることなく位相雑音を低減する。

【解決手段】バイポーラトランジスタTr1のコレクタとベース間にバイアス回路を備える発振器において、電源Vccとコレクタとの間に発振周波数よりも低いベースバンド周波数帯域において十分に高いインピーダンスを示す素子や回路、例えばベースバンドチョークコイル16を接続する。ベースバンド周波数帯域のノイズ信号はチョークコイル16により電源側に漏れることなくバイアス回路を介して負帰還される。チョークコイル16の代わりにカレントミラー回路を設けてもよい。

(もっと読む)

遅延素子、可変遅延線及び電圧制御発振器並びにそれを備えた表示装置及びシステム

【課題】温度が変化しても中心発振周波数が安定している電圧制御発振器等を、簡単な構成で提供する。

【解決手段】入力信号Viに遅延量τdを加えて出力信号Voとする遅延発生部11と、遅延τdを制御する遅延制御部12とを備えている。遅延制御部12は、遅延量τdを調節する第一の制御信号としての制御信号S1を出力する遅延調節回路13と、温度による特性変化を補償する第二の制御信号としての制御信号S2を出力する温度補償回路14とを有し、制御信号S1と制御信号S2とを合成して得た第三の制御信号としての制御信号S3を遅延発生部11へ出力することにより遅延量τdを制御する。遅延制御部12は、遅延調節回路13と温度補償回路14とを直列に接続することにより、制御信号S3を得ている。

(もっと読む)

電圧電流変換回路、及び電圧制御発振回路

【課題】入力電圧に対する出力精度の高い電圧電流変換回路、及び電圧制御発振回路を提供する。

【解決手段】電圧電流変換回路は、入力端子1に入力された入力電圧を電流に変換して、出力する電圧電流変換回路であって、入力端子1に接続されたゲートを有するNMOS4を含み、NMOS4に流れる電流に応じた出力電流を発生する第一電流発生回路11と、ソース、及びドレインと異なる電位となるゲートを有するNMOS8を含み、NMOS8に流れる電流に応じた重畳電流を発生して、NMOS4に供給する第二電流発生回路と、を備えたものである。

(もっと読む)

電気的に制御される磁気回路を備えた装置の駆動回路

【課題】

部品の着脱作業を要することなく、簡単に、発振器等磁気回路を備えた装置単体での、周波数特性の検査を可能とした電気的に制御される磁気回路を備えた装置の駆動回路を提供する。

【解決手段】

信号レベル調整部14と積分回路部15とを具備する電気的に制御される磁気回路を備えた装置の駆動回路であって、前記積分回路部がOPアンプ23と、該OPアンプに対して並列に接続されたコンデンサ27と、並列に接続された負帰還用の抵抗28と、該抵抗を前記OPアンプに対して継断するスイッチング手段33,32とを有し、該スイッチング手段が前記抵抗を断状態とすることで、前記積分回路部が積分回路として動作し、前記スイッチング手段が前記抵抗を継状態とすることで、前記積分回路部が増幅回路として動作する様構成した。

(もっと読む)

センサモジュール、およびセンサモジュールの間欠動作周期の調整方法

【課題】高い周波数精度と安定度を備えた水晶発振子、あるいはセラミック発振子等を用いることなく、消費電流を抑え、電池により長時間稼動するセンサモジュールを実現する。

【解決手段】センサ回路16を搭載したセンサモジュール1は、センサ回路16を間欠的に動作させる間欠動作周期発生回路11と、間欠動作周期発生回路11を動作させる基本クロック発振回路12と、動作プログラムを実行するCPU14と、外部機器30と通信する通信回路18と、間欠動作周期発生回路11を用いて発生した間欠動作周期をパルス信号として外部機器30へ出力する外部出力回路19と、周期偏差が書き込まれる周期偏差格納不揮発性メモリ20と、を備え、周期偏差は、間欠動作周期発生回路11に所定周期の信号を発生させる設定値と、外部機器30により計測され、通信回路18を通じてCPU14へ送信される間欠動作周期とに基づいて、CPU14により算出される。

(もっと読む)

電圧制御発振器

【課題】広い周波数範囲で安定して動作する電圧制御発振器を提供する。

【解決手段】電圧制御発振器11の差動増幅器12の出力を入力側に帰還する帰還キャパシタC1と、帰還キャパシタC1と差動増幅器12の入力端子の接続点に一端が接続され、他端が接地された可変容量素子VCを有する。電圧制御発振器11の発振周波数が変更されると、制御部13は、可変容量素子VCに印加する電圧を制御してその容量値を変化させ、電圧制御発振器11のオープンループゲインがほぼ一定になるようにする。

(もっと読む)

温度安定化発振器及び同発振器を含む近接スイッチ

【課題】発振器の温度依存性を簡単に安定化すると共に、大きな切換え距離を有して広い温度範囲に渡って安全に機能する近接スイッチの簡単で低コストの製造を可能にする。

【解決手段】共振回路L,C,RCUと仮想負性抵抗として接続される増幅器回路V,R1,R2,R3を含む発振器において、直流電流源I1は、共振回路L,C,RCUと直列に接続されている。こうして、発振器回路コイルLの抵抗の尺度である電流UCUがもたらされる。この信号UCUを使用することによって、制御回路V1,Mは、発振器回路コイルLの抵抗RCUに逆比例する仮想負性抵抗を制御する。

(もっと読む)

制御装置

【課題】低電力損失、低ノイズで被制御信号に対する制御ができる。

【解決手段】制御入力端子8に入力された制御信号17による+電位及び制御出力端子9に制御信号18による−電位が、電圧制御可変コンデンサ21の電圧制御可変コンデンサ1(C1〜C4)の各電極に抵抗器Rを介して供給される。すると、電圧制御可変コンデンサ21(C1〜C4)の各電極間の+電位及び−電位による制御信号により、各電極間の電圧制御可変コンデンサ21の容量が変化する。従って、この変化した容量及びAC入力15による電位に応じた電界が制御信号の電圧に影響なく発生する。

(もっと読む)

21 - 40 / 88

[ Back to top ]