Fターム[5J081LL08]の内容

LC分布定数、CR発振器 (9,854) | 改善手段(発明内容) (679) | 接続の変更 (102) | 切換え (84)

Fターム[5J081LL08]に分類される特許

21 - 40 / 84

オーム調節可能な発振周波数を有する発振器

調節可能な発振周波数を有する発振器は、端子で負性入力抵抗を示している能動素子、負性入力抵抗を示しているその能動素子の端子と連結した発振回路、および、その発振器の発振周波数が調節可能である調節可能なオーム抵抗を有する素子を含む。 (もっと読む)

電圧制御発振回路

【課題】製造コストの追加なく一般的に用いられる可変容量素子を利用し、位相雑音特性に優れたRTW形式の電圧制御発振回路を実現できるようにする。

【解決手段】電圧制御発振回路は、ループ状の伝送線路15と、信号線路と接続されたアクティブ回路17と、信号線路と接続され複数の可変容量ユニット23を有する可変容量部21とを備えている。各可変容量ユニット23は、可変容量素子31と、可変容量素子31に制御電位を印加する制御端子41と、可変容量素子31に基準電位を印加する基準電位端子43とを有している。少なくとも2つの可変容量ユニット23は、基準電位が互いに異なっている。

(もっと読む)

発振回路内で構成要素を接続するオプションコンダクタを提供する技術

発振回路は、第1の伝導層内でルーティングコンダクタを介して相互結合されるトランジスタを含む。発振回路はまた、第2の伝導層内に、バラクタ、コンデンサ、およびオプションコンダクタも含む。オプションコンダクタは、トランジスタのうちの1つとコンデンサまたはバラクタとの間の接続の少なくとも一部を形成する。上記発振回路は、第1の伝導層内のルーティングコンダクタを介して前記複数の第1のトランジスタのうちの1つに結合されるインダクタと、該インダクタの第1の部分を形成する、前記第2の伝導層内の第2のオプションコンダクタとをさらに備え得る。  (もっと読む)

(もっと読む)

信号処理装置及び信号処理方法

【課題】最大の周波数マージンで、発生させる発振周波数をロック状態にする。

【解決手段】ループフィルタ23は、発振周波数における所定の特性に基づいて、入力される制御電圧に対応して発振周波数を発生させるVCO63であって、所定の特性が粗調整されるVCO63に、制御電圧を入力し、VCO粗調整回路135は、制御電圧が所定の設定範囲を超えた場合に、VCOによる所定の特性を、複数の特性のうちのいずれかに粗調整し、DAC133は、制御電圧が所定の設定範囲内で変化する場合に、発振周波数がロック状態とならないとき、所定の設定範囲を広げる方向に更新する。本発明は、例えばPLL回路やCDR回路に適用することができる。

(もっと読む)

発振器およびMMIC

【課題】 高周波の発振器において、プロセスバラツキにより発振周波数が仕様範囲から外れてしまう問題がある。通常はトリミング等により周波数調整を行う方法がある。しかし、高周波発振器を樹脂で封止するトリミングを行うことはできない。さらに、樹脂により寄生容量が変化してしまうため樹脂封止前後で発振周波数が変化してしまうため、別の方法による周波数調整方法が必要となる。

【解決手段】 同一基板上に発振器を複数設けて、それぞれの発振周波数が異なるようにする。また、各発振器を外部からの印加電圧によって発振/停止を制御できるようにして、複数の発振器の中から最適な発振器一台のみを発振させる。

(もっと読む)

PLL周波数シンセサイザ回路及びその制御方法

【課題】信号に対するノイズの増加がなく安定したPLL周波数シンセサイザ回路及びその制御方法を提供する。

【解決手段】電圧制御発振器の制御電圧をモニタし、制御電圧に応じて前記電圧制御発振器の変調感度との間で安定に動作するように設定されたループフィルタを切り替えるようにした。

(もっと読む)

無線装置

【課題】

簡単な回路構成で2つの周波数帯域を出力可能とし、無線装置の小型化及びコストの低減を図る。

【解決手段】

発振回路部26から発せられる基本周波数を逓倍回路部27を介して出力する様にし、該逓倍回路部に給電する電圧を2つの異なる電圧に切換え可能とし、1つの電圧では前記逓倍回路部が増幅作動する様にし、他の電圧では該逓倍回路部が逓倍作動する様構成し、2つの周波数帯を択一的に発信可能とした。

(もっと読む)

発振器

【課題】内蔵するICチップの内容を外部から設定し、書き換えることで回路定数や回路方式あるいは分周数を実装機器の仕様に合せて切り換え可能とした融通性の高い発振器を提供する。

【解決手段】内蔵するICチップ3に発振回路と共に複数の回路定数や回路方式の回路、あるいは複数の分周数の分周回路を備えると共に、該ICチップに不揮発メモリの領域、あるいは分周回路領域を設け、発振器の回路定数や回路方式を当該不揮発メモリに外部から書き込んだデータで切り換える構成とした。

(もっと読む)

発振回路装置

【課題】 この発明は、負性抵抗を示す帯域が広くして、使用できる発振周波数を多くすることを目的とするものである。

【解決手段】 この発明の発振回路装置は、相互接続された一対のトランジスタ1、2と抵抗・容量の回路網で構成された発振部100と、発振部100に接続されるループ状の伝送線路で構成された共振部200と、を備え、前記抵抗・容量の回路網の抵抗値及び容量値を前記発振部が第1の周波数帯で負性抵抗となり、その第1の周波数帯より高い周波数帯においてフラットな負性抵抗を示すように設定したことを特徴とする。

(もっと読む)

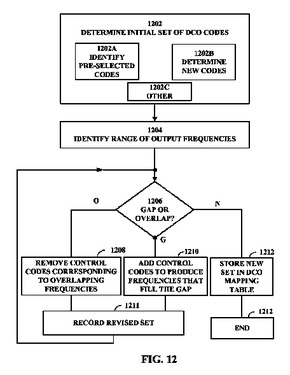

デジタル制御発振器のためのダイナミック較正技法

デジタル制御発振器(DCO)を較正するための技法を開示する。本開示の一態様では、DCOを動作させるための制御コードの初期セットを判断する。初期セットから生成された出力周波数レンジを識別する。周波数レンジにおけるギャップまたはオーバーラップインスタンスを識別する。オーバーラップの場合、修正されたセットを確立するためにオーバーラップインスタンスに対応する制御コードを初期セットから除去する。ギャップの場合、ギャップを充填する周波数値を生成するために、制御コードを初期セットに追加する。同じことを実行するための装置も開示する。  (もっと読む)

(もっと読む)

デジタル制御発振器及びこれを用いた位相同期回路

【課題】発振周波数を線形に近くかつきめ細やかに制御可能なデジタル制御発振器を提供する。

【解決手段】正相発振信号を出力する正端子213と、逆相発振信号を出力する負端子214と、センタータップ210とを有し、正端子とセンタータップとの間の任意の位置に第1の接点211を備え、負端子とセンタータップとの間の第1の接点に対応する位置に第2の接点212を備える差動インダクタ200と、正端子と負端子との間に接続され、第1のデジタル制御コードによってキャパシタンスを2値に変化させる第1の可変キャパシタを複数含む第1の可変キャパシタバンク220と、第1の接点と第2の接点との間に接続され、第2のデジタル制御コードによってキャパシタンスを2値に変化させる第2の可変キャパシタを複数含む第2の可変キャパシタバンク240と、正端子と負端子との間に接続される負性抵抗230とを具備する

(もっと読む)

VCOのキャパシタバンクのトリミングとキャリブレーション

技法は、電圧制御発振器(VCO)で使用されるキャパシタバンクに関連するキャパシタンスをトリミングするために開示される。実施例では、キャパシタンスはそれぞれ複数の構成要素のキャパシタンスへサブ分割される。実施例では、キャパシタンスはそれぞれ複数の構成要素のキャパシタンスへサブ分割される。構成要素のキャパシタンスは、キャパシタバンクのステップのサイズをトリミングするために選択的にイネーブルされ、またはディスイネーブルされ得る。さらなる技法は、キャパシタバンクについてステップのサイズの誤差を最小化するためにトリミング可能なキャパシタンスをキャリブレートするために開示される。  (もっと読む)

(もっと読む)

温度補償型水晶発振器

【課題】 出力信号の測定の作業性を容易にする。

【解決手段】 温度補償回路部と水晶振動子が接続された発振回路部から2つの出力端子が設けられた温度補償型水晶発振器にであって、発振回路と2つの出力端子とに接続するスイッチ部を備え、スイッチ部が、2つの出力端子のうち一方の出力端子と発振回路との間に設けられる第一のスイッチ部と、発振回路と前記第一のスイッチ部との間と2つの出力端子のうち他方の出力端子とを結ぶ経路において、第一のスイッチ部と前記一方の出力端子との間と経路との間に設けられる第二のスイッチ部と、を備えて構成されることを特徴とする。

(もっと読む)

振幅一定回路

【課題】本発明の課題は、周波数選択特性を有する回路の出力の振幅をほぼ一定にすることである。

【解決手段】制御回路12は、インダクタL0とキャパシタC0と抵抗R0からなる共振回路にキャパシタC1を並列に接続した場合の共振周波数を予め算出し、その共振周波数において、インピーダンスZがほぼ一定値になるような抵抗値を算出しておく。そして、その抵抗値となるようにスイッチSW3とSW4を切り換えて、抵抗R1、可変抵抗R2を選択する。

(もっと読む)

圧電発振器およびリアルタイムクロック

【課題】消費電力を低減すると共に、外部へ出力する発振信号の周波数安定性を良好にした圧電発振器およびリアルタイムクロックを提供する。

【解決手段】圧電発振器10は、圧電振動子12に接続し、発振信号を出力する発振回路14と、発振信号を入力し、且つ、発振信号を外部に出力するか否かを選択する制御信号に基づいて、発振信号を外部に出力するか否かを切り替える出力切替部16と、発振回路14に接続し、発振信号を外部出力しない制御信号を入力すると、発振信号を外部出力するときに比べて負荷容量を小さくする負荷容量可変回路20とを備えた構成である。

(もっと読む)

発振回路

【課題】温度補償回路に発振部の出力がノイズとして入力しない発振回路を提供する。

【課題の解決手段】周囲温度に応じた制御信号によって出力周波数が制御される発振部1と、この発振部1に制御信号を供給する温度補償回路2と、発振部1の発振出力と温度補償回路2の温度センサ出力のいずれかを出力するようオンオフ制御される出力バッファ4と温度センサ出力スイッチ3からなる切換スイッチ回路とを備え、温度センサ出力スイッチ3は、トランスファーゲートスイッチ301,302を2段直列に接続し、この接続点に固定電位に接続した第3のスイッチ303を介在させてなり、発振出力を出力する時はトランスファーゲートスイッチ301,302をオフとして、第3のスイッチ303をオンとし、温度センサ出力を出力する時はトランスファーゲートスイッチ301,302をオンとして、第3のスイッチ303をオフとする。

(もっと読む)

電圧制御発振回路

【課題】発振信号の周波数帯域を広くさせつつ、位相雑音を低減することが可能な電圧制御発振回路を提供することを目的とする。

【解決手段】電圧制御発振器7〜10と、選択信号Vout_SELに対応する発振信号を選択するセレクタ11と、セレクタ11により選択された発振信号の振幅値Vout_Levを検出する検出回路12と、スイッチ13、14と、スイッチ13を介して入力される電圧Vtuneに対応するデジタル値Daを出力するとともに、スイッチ14を介して入力される振幅値Vout_Levに対応するデジタル値Dbを出力するADC回路15と、選択信号Vout_SEL及び選択信号Vout_CAPをデジタル値Daに基づいて出力するとともに、電圧制御発振器に流れる電流値をデジタル値Dbに基づいて制御する制御回路16とを備えて電圧制御発振回路2を構成する。

(もっと読む)

発振回路および発振器

【課題】低消費電流化した発振回路および発振器を提供すると共に、外部との通信による誤動作の防止および高精度な発振回路および発振器を提供する。

【解決手段】発振回路10は、外部との通信を行うインターフェース回路12と、発振段20とを備えたものであって、インターフェース回路12に接続し、インターフェース回路12に入力または出力する通信信号の外部通信端子40と、インターフェース回路12の制御信号入力端子に接続し、インターフェース回路12をアクティブ状態またはスリープ状態に切り替える制御信号を入力する外部制御端子38とを備えた構成である。そしてインターフェース回路12は、外部制御端子38および制御信号入力端子を介してインターフェース回路12に入力した制御信号にしたがってアクティブまたはスリープのいずれかの状態になる。

(もっと読む)

シンセサイザまたは発振器モジュールと、このシンセサイザを用いたシンセサイザモジュール、受信装置、及び電子機器、ならびに分周器の分周比の制御方法

【課題】制御部による分周器の制御に起因したノイズの発生を抑え、受信特性の良好な受信機を実現可能なシンセサイザを提供することを目的とする。

【解決手段】制御部7は、温度を検出する温度検出部8の出力信号に基づいて第2の分周器6へ適当な整数分周数Mや分数分周数Nの制御信号を送り、第2の分周器6の分周比を変化させる。つまり、第2の分周器6は、分周数Mが入力される整数部分と、分周数Nが入力される分数部分により構成される。制御部7は、温度を検出する温度検出部8の温度信号に基づいて第2分周器6の分周比を不均一な時間間隔で変化させる。これにより、第2分周器6の制御に伴い特定周波数に多数発生するノイズを抑圧することができ、シンセサイザの位相雑音を低減することができる。

(もっと読む)

発振回路、異常発振検査方法、高周波受信機、及び高周波送信機

【課題】複数の電圧制御発振器を有するにもかかわらず異常発振の有無検査の検査時間を短縮することができる発振回路を提供する。

【解決手段】動作電流がそれぞれ異なる値である第1から第n(nは2以上の自然数)の電圧制御発振器VCO1〜VCOnと、1つの基準電圧生成回路RV0と、第1から第n(nは2以上の自然数)のスイッチSW1〜SWnとを備え、すべてのk(k=1〜n)について、第kの電圧制御発振器VCOkの直流バイアス入力端子T_kと基準電圧生成回路RV0の直流バイアス出力端子T_0との間に第kのスイッチSWkが設けられており、第kのスイッチSWkがオン状態のときに基準電圧生成回路RV0から第kの電圧制御発振器VCOkの差動トランジスタにベースバイアス電圧が供給される発振回路。

(もっと読む)

21 - 40 / 84

[ Back to top ]