Fターム[5J098AA04]の内容

能動素子を用いた回路網 (5,588) | 回路素子 (1,159) | 半導体素子 (443) | ダイオード (35)

Fターム[5J098AA04]の下位に属するFターム

可変容量ダイオード (7)

Fターム[5J098AA04]に分類される特許

1 - 20 / 28

ポジショナ

【課題】低周波のノイズの影響に強いポジショナを提供する。

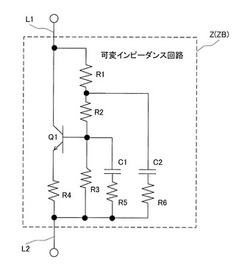

【解決手段】入力ラインL1と出力ラインL2との間に能動負荷Zとして可変インピーダンス回路ZBを設ける。可変インピーダンス回路ZBは、直流の電流信号に対するインピーダンスが低く、交流の電流信号に対するインピーダンスが高いという特性を有し、ラインL1,L2間に接続された抵抗R1とR2とR3との直列回路と、ラインL1にそのコレクタが接続され、そのベースが抵抗R2とR3との接続点に接続されたトランジスタQ1と、トランジスタQ1のエミッタとラインL2との間に接続された抵抗R4と、抵抗R2とR3との接続点にその一端が接続されたコンデンサC1と、コンデンサC1の他端とラインL2との間に接続された抵抗R5と、抵抗R1とR2との接続点にその一端が接続されたコンデンサC2と、コンデンサC2の他端とラインL2との間に接続された抵抗R2とから構成されている。

(もっと読む)

積分回路および電圧検出装置

【課題】カットオフ周波数が入力抵抗と帰還コンデンサとで規定される目標とする積分特性を確保しつつ、積分信号の振動を防止する。

【解決手段】非反転入力端子がグランド電位Vgに規定された演算増幅器34aと、演算増幅器34aの反転入力端子に接続された入力抵抗34bと、演算増幅器34aの反転入力端子に一端が接続されると共に演算増幅器34aの出力端子に他端が接続された帰還コンデンサ34cと、演算増幅器34aの反転入力端子に一端が接続されると共に演算増幅器34aの出力端子に他端が接続され、かつ接続点Bが交流的にグランド電位Vgに短絡可能に構成された帰還抵抗34d,34eとを備え、接続点Bとグランド電位Vgとの間に接続されて、接続点Bのグランド電位Vgへの交流的な短絡をオン・オフさせる短絡用スイッチ34gを備えている。

(もっと読む)

電磁誘導型埋設物探査装置

【課題】デジタル信号処理装置(略称「DSP」)による電磁誘導型埋設物探査装置では、デジタル化時の量子化レベル等の制約によって十分な感度が得られず、非金属管路に収容される光ファイバーケーブルを、手軽な間接法によって検出することが難しかった。

【解決手段】本発明の水晶アクティブフィルタは中心周波数の調整機能と水晶振動子の破損防護機能を有しており、多段接続により超狭帯域かつ高DU比のフィルタを容易に構成することができ、高感度の電磁誘導型埋設物探査装置を実現することができる。これによって、非金属管に収容される光ファイバーケーブルを、間接法によって検出することが可能となる。

(もっと読む)

アクティブポリフェーズフィルタ

【課題】大電力を入力しても歪の小さいアクティブポリフェーズフィルタを提供する。

【解決手段】npnトランジスタQ1、Q2、Q4及びQ5と、npnトランジスタQ6、Q7、Q4及びQ5は、各々トランスリニアループを形成している。また、npnトランジスタQ2及びQ3と、npnトランジスタQ7及びQ8は各々カレントミラー回路を形成している。こうして、npnトランジスタQ1とQ3の各々のコレクタ電流の差と、npnトランジスタQ6とQ8の各々のコレクタ電流の差とが、いずれも、平衡な高周波入力の電流に等しくなる。このような2組の差動入力を、ポリフェーズフィルタ部10の4入力とすることで、ポリフェーズフィルタ部10の4出力から、偶数次成分の抑制された、位相がπ/2異なる差動出力を得ることができる。

(もっと読む)

容量増倍回路

【課題】半導体材料に起因するhfeのばらつきなどに影響されることなく、安定した増倍率を確保する。

【解決手段】カレントミラー比が共に1:Nに設定された第1及び第2のカレントミラー回路21,22の各々の入力段の間に、第1及び第2のトランジスタ1,13がトーテムポール接続により直列接続されて設けられ、この第1及び第2のトランジスタ1,13の相互の接続点に容量3の一端が接続され、容量3の他端は、入力信号が印加可能とされ、第1及び第2のカレントミラー回路21,22の出力段は、相互に接続されて信号出力可能とされると共に、容量3の他端に接続されて、信号入力端子8から見た容量3の見かけ上の容量値が(1+N)倍に見えるものとなっている。

(もっと読む)

寄生容量により誘導される誤差が減少されたセンサデバイス

デバイス110は、駆動ノード34,36および感知ノード42,44を有する感知素子26を備えている。駆動ノード34および感知ノード42との間には寄生容量22が存在する。同様に、駆動ノード36と感知ノード44との間には寄生容量24が存在する。駆動信号56が駆動ノード34、36との間に印加されると、駆動ノード34と感知ノード42との間の寄生電流70および駆動ノード36と感知ノード44との間の寄生電流72が寄生容量22,24のおかげで生成される。容量性ネットワーク112を介して寄生電流70を打ち消す補正電流134を生成するために、駆動ノード36と感知ノード42との間に容量ネットワーク112が接続される。同様に、容量性ネットワーク112を介して寄生電流72を打ち消す補正電流138を生成するために、駆動ノード34と感知ノード44との間に容量性ネットワーク114が接続される。  (もっと読む)

(もっと読む)

位相同期回路におけるループフィルタ

【課題】C/Nを改善することができる位相同期回路におけるループフィルタを提供する。

【解決手段】本発明の位相同期回路におけるループフィルタ1は、増幅回路2、第1のローパスフィルタ3、第2のローパスフィルタ4、電圧供給回路17、スイッチング素子5を備える。第2のローパスフィルタ4は、増幅回路2の出力端子2aと第1のローパスフィルタ3との間に接続され、バイアス電圧を供給する電圧供給回路17にも接続される。スイッチング素子5は、第2のローパスフィルタ4の接続状態を制御し、増幅回路2から出力された制御電圧が所定の電圧以下に降下したときに自動的にオンとなるように形成される。

(もっと読む)

半導体集積回路

【課題】電源電圧の変化に依存する内蔵フィルタの周波数特性の不所望な変化を軽減すること。

【解決手段】半導体集積回路は校正回路200を具備し、内蔵容量70:151は容量とスイッチを有する。V・I変換器30、20は基準電圧を電流に変換して、電流に応答する時間積分器40、50は容量70の時間積分を実行して、電圧比較器80は基準電圧と内蔵容量70の端子電圧を比較する。校正動作の間に時間積分と電圧比較が実行され、その結果はラッチ90に格納される。校正動作の完了時のラッチ90の格納結果に従って、内蔵フィルタ150の周波数特性が決定される。V・I変換器30、20のスイッチ素子SW0のNチャンネルMOSトランジスタのゲートに、校正動作の間に安定化電圧VREFが供給される。

(もっと読む)

移相回路

【課題】低損失化を図ることができるとともに、小形化を図ることができる移相回路を得る。

【解決手段】第1の入出力端子1aと、第2の入出力端子1bと、第1の入出力端子1aと第2の入出力端子1bの間に接続された第1のスイッチング素子2aと、第1の入出力端子1aに一端が接続された第1のキャパシタ3aと、第2の入出力端子1bに一端が接続された第2のキャパシタ3bと、第1及び第2のキャパシタ3a、3bの他端とグランド4の間に接続された第2のスイッチング素子2bとを設けた。

(もっと読む)

電流方式ローパスフィルタ

【課題】回路規模の小さい電流方式ローパスフィルタを提供する。

【解決手段】ローパスフィルタ10は、入力端子12と、出力電圧発生ノード16と、電源Vccから入力端子12に定電流Iconst1を供給する定電流源48と、電源Vccから出力電圧発生ノード16に定電流Iconst2を供給する定電流源50と、出力電圧発生ノード16に接続された入力を有するボルテージフォロワ回路34と、ボルテージフォロワ回路34の出力と入力端子12との間に接続された抵抗36と、出力電圧発生ノード16に接続された容量20と、ベース接地トランジスタ62と、カレントミラー回路28と、ボルテージフォロワ回路34の出力に接続された出力端子14とを備える。

(もっと読む)

無限移相器及び移相器

【課題】ICチップ化が可能な無限移相器。

【解決手段】1.Aの無限移相器100においては、位相調整回路10に高周波が入力され、位相が0以上π/4未満の任意量で変化される。4相発生回路20では入力された高周波に対し、位相が一致した高周波、位相がπ/2、π及び3π/2進んだ高周波の4つが同時に生成される。ベクトル合成回路30では、入力された4つの高周波のうちの1つが利得調整回路40に出力されるか、位相がπ/2異なる2つの高周波のベクトル和が利得調整回路40に出力される。利得調整回路40では、ベクトル合成回路30に入力された4つの高周波のうちの1つが出力された場合の利得を基準として、ベクトル合成回路30に入力された4つの高周波のうちの2つの高周波の和が出力された場合の利得を1.5dB低くする。1.Bの無限移相器150は接続順序を替えたものである。

(もっと読む)

フィルタ回路及びこれを用いたテレビチューナ回路

【課題】広い周波数レンジでフィルタのQ値を所望の値に設定する。

【解決手段】フィルタ回路1は、入力電圧信号を電流信号に変換する可変トランスコンダクタンスgm1と、可変トランスコンダクタンスgm1の後段に結合されたRLCタンクと3aを備え、RLCタンク3aは、互いに並列に結合された可変キャパシタC1と可変抵抗R1とインダクタL1とを有し、可変キャパシタC1のキャパシタンス値を、フィルタ回路1の周波数特性を示す中心周波数またはカットオフ周波数の2乗に反比例して設定する周波数チューニング回路7と、可変抵抗R1の抵抗値を、可変トランスコンダクタンスgm1のトランスコンダクタンス値に反比例して設定するゲインチューニング回路8とをさらに備え、可変トランスコンダクタンスgm1のトランスコンダクタンス値は、中心周波数またはカットオフ周波数に依存した値に設定される。

(もっと読む)

入力回路付き電子部品回路

【課題】 電子部品の入力端子に入力される入力電圧を制限しながらも、部品点数を少なく、簡易な回路とした入力回路付き電子部品回路を提供する。

【解決手段】 入力回路付き電子部品回路10は、入力端子INA等を有する電子部品2と、入力回路4A等と、入力電圧制限回路9とを備える。入力電圧制限回路9は、定電圧ノード5を所定の定電圧Vcとする定電圧回路3、定電圧ノード5と入力回路4Aとの間に介在し、アノード6Aaを入力回路4Aに、カソード6Acを定電圧ノード5にそれぞれ接続した複数のダイオード6A,6B,6Cを含み、ダイオード6A,6B,6Cの順方向電圧降下をVfとしたとき、定電圧ノード5における定電圧Vcを、最大許容電圧Vmaxから順方向電圧降下Vfを差し引いた値より小さくしてなる(Vc<Vmax−Vf)。

(もっと読む)

ハイパスフィルタ

【課題】コンデンサの容量を小さくしてカットオフ周波数の低いフィルタを実現する。

【解決手段】コンデンサC1は、一端に入力信号を受け、他端側から出力信号を出力する。このコンデンサC1の他端側に接続され、電源との間で抵抗として機能する抵抗回路が設けられる。この抵抗回路は、ベースが前記コンデンサの他端に接続されたPNPトランジスタTr1と、ベースが前記コンデンサの他端に接続されたNPNトランジスタTr2を含む。そして、これらPNPトランジスタおよびNPNトランジスタのそれぞれに差動アンプ2が相補的電流を供給する。また、前記差動アンプに前記コンデンサの他端側の信号を負帰還する。

(もっと読む)

マルチバイブレータ型発振回路

【課題】2次以降の高調波を低減させた低歪の正弦波出力が得られ、また発振周波数を変えた場合でも、基本波を減衰させることなく、低歪の正弦波出力が得られるようにする。

【解決手段】マルチバイブレータ回路10を有するマルチバイブレータ型発振回路で、マルチバイブレータ回路10の出力側に、その出力電圧波形の高調波を低減する第1及び第2の電流可変(n次)フィルタ回路20,22を接続し、このフィルタ回路20,22により、高調波を減衰させた低歪の正弦波出力を得る。また、マルチバイブレータ回路10の発振周波数設定用のバイアス電流Ix2,Ix3と連動する連動電流をトランジスタQ17,Q18にて抽出し、この連動電流によって、上記フィルタ回路20,22のカットオフ周波数を変化させ、基本波の減衰をなくす。

(もっと読む)

アッテネータ

【課題】通過状態及び減衰状態において同程度の歪み特性を同程度の送信電力まで許容することができ、かつ通過状態において電力増幅器の利得圧縮特性を補償することができるアッテネータを得る。

【解決手段】リニアライザは、第5ダイオードD51〜D5nと、第3抵抗RLT1と、第6ダイオードD61〜D6nと、第1のnチャネルMOSトランジスタTr1とを有する。そして、第1,第4制御電圧端子Vc1,Vc4にロウレベルの電圧が印加され、かつ第2,第3制御電圧端子Vc2,Vc3にハイレベルの電圧が印加される場合に、第5制御電圧端子Vc5にロウレベルの電圧が印加され、第1,第4制御電圧端子Vc1,Vc4にハイレベルの電圧が印加され、かつ第2,第3制御電圧端子Vc2,Vc3にロウレベルの電圧が印加される場合に、第5制御電圧端子Vc5にハイレベルの電圧が印加される。

(もっと読む)

高周波回路

【課題】広帯域増幅器とバイパス回路とを併設し、それらを切り替える切替回路を備えた高周波回路において、前記バイパス回路が作動するときにフィルタ作用を発揮させて、バイパス回路による受信帯域より低い帯域の信号をより減衰させることができる高周波回路を提供すること。

【解決手段】入力された高周波信号を増幅する広帯域増幅器2と、コンデンサCを有するとともに、前記広帯域増幅器2に並列に接続されたバイパス回路4と、インダクタLを有するとともに、信号経路を前記広帯域増幅器2または前記バイパス回路4に切り替えるための切替回路5とを備え、前記切替回路5により前記信号経路を前記バイパス回路4側に切り替えた時、前記コンデンサCと前記インダクタLとでハイパスフィルタを構成するように形成したことを特徴とする。

(もっと読む)

フィルタ回路

【課題】電源投入時の起動時間を短縮することが可能なフィルタ回路を提供する。

【解決手段】電源投入時には各スイッチSW1,SW2をオフ動作させてキャパシタCfcをオペアンプAMPから切り離すことにより、出力端子OUTの電圧を急峻に立ち上げ、電源投入時の起動時間を短縮させる。そして、出力端子OUTの電圧が完全に安定した時点で各トランジスタSW1,SW2をオン動作させる。すると、フィルタ回路10はキャパシタCfcに抵抗Rfcが並列接続された不完全積分回路を構成するため、キャパシタCfcおよび各抵抗Ra,Rfcによって規定されるフィルタ特性を確保できる。

(もっと読む)

フィルタの自動調整装置

【課題】ダミーフィルタの次数とメインフィルタの次数とが異なっていても、メインフィルタの周波数特性を所望の特性に調整することができるようにする。

【解決手段】ダミーフィルタ2の制御電圧Vcdを出力する第1のオペアンプ5とメインフィルタ1との間にインタフェース回路6として第2のオペアンプ7を配置し、第2のオペアンプ7の基準電圧Vrを最適化することにより、ダミーフィルタ2を用いて得られた制御電圧Vcdがインタフェース回路6によってメインフィルタ1に最適な制御電圧Vcmに変換されるようにして、メインフィルタ1の周波数特性を所望の特性に調整するのに必要な最適な制御電圧Vcmを得ることができようにする。

(もっと読む)

ミュート回路

【課題】入出力インターフェースにおいてミューティング用MOSトランジスタの耐圧により制限される電源電圧範囲を拡大できるミュート回路を提供することを目的とする。

【解決手段】正負の信号が出力される出力端子10のミューティング用NchMOSトランジスタ1と、このトランジスタ1のゲートに印加される電圧を切換え、トランジスタ1のオン/オフを制御するミュート切換回路3を備え、トランジスタ1のバックゲートを、出力端子10と所定のマイナス電位VSSとの間に直列に接続される抵抗R1と抵抗R2の抵抗分割でバイアスする。この回路構成によれば、トランジスタ1がオフされることによるミュートオフ時に、トランジスタ1のバックゲート電圧が、出力端子10に出力される信号の変動に伴い変動され電源電位VCCの範囲に抑えられることにより、トランジスタ1の耐圧を電源電位VCCの範囲に抑えることができる。

(もっと読む)

1 - 20 / 28

[ Back to top ]