Fターム[5J098AA14]の内容

能動素子を用いた回路網 (5,588) | 回路素子 (1,159) | コンデンサ (333)

Fターム[5J098AA14]の下位に属するFターム

可変コンデンサ (54)

Fターム[5J098AA14]に分類される特許

61 - 80 / 279

フィルタ回路および通信装置

【課題】フライングキャパシタを備えるフィルタ回路において、急峻な減衰特性を備えることが可能なフィルタ回路を提供すること。

【解決手段】フライングキャパシタと、フライングキャパシタの入力端と出力端との間に、フライングキャパシタと並列に設けられるキャパシタと、を備えるフィルタ回路は提供される。フライングキャパシタの入力端と出力端との間に所定の容量を有するキャパシタを設けることで、フライングキャパシタを備えるフィルタ回路において、急峻な減衰特性を備えることが可能となる。

(もっと読む)

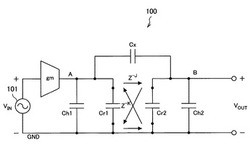

フィルタ回路および通信装置

【課題】フライングキャパシタを備え、急峻な減衰特性を備えた上でさらにQ値を可変にすることが可能なフィルタ回路の提供。

【解決手段】入力端から出力端へ切り替わる場合には極性を維持し、出力端から入力端へ切り替わる場合には極性が反転するフライングキャパシタと、フライングキャパシタの入力端にフライングキャパシタと並列に設けられる第1のキャパシタCh1と、フライングキャパシタの出力端にフライングキャパシタと並列に設けられる第2のキャパシタCh2と、を備え、フライングキャパシタは、出力端から入力端へ切り替わってから所定の時間遅延して入力端から出力端へ切り替わり、入力端から出力端へ切り替わってから所定の時間遅延して出力端から入力端へ切り替わる、フィルタ回路。

(もっと読む)

位相同期回路におけるループフィルタ

【課題】C/Nを改善することができる位相同期回路におけるループフィルタを提供する。

【解決手段】本発明の位相同期回路におけるループフィルタ1は、増幅回路2、第1のローパスフィルタ3、第2のローパスフィルタ4、電圧供給回路17、スイッチング素子5を備える。第2のローパスフィルタ4は、増幅回路2の出力端子2aと第1のローパスフィルタ3との間に接続され、バイアス電圧を供給する電圧供給回路17にも接続される。スイッチング素子5は、第2のローパスフィルタ4の接続状態を制御し、増幅回路2から出力された制御電圧が所定の電圧以下に降下したときに自動的にオンとなるように形成される。

(もっと読む)

フィルタ回路

【課題】ソースフォロワ回路をベースにした、高速でかつ低消費電流であり、高次フィルタの場合でも低い電源電圧で動作が可能なフィルタ回路を提供すること。

【解決手段】ソースフォロワ回路27とドレインフォロワ回路28a,28bとを備え、ソースフォロワ回路27は、MOSトランジスタ1乃至4とコンデンサ25,26と電流源9,10を備え、ドレインフォロワ回路28a,28bは、MOSトランジスタ5乃至8と電流源11,12、29.30とを備えている。ドレインフォロワ回路を用いているので、MOSトランジスタの閾値変動と関係なく2次フィルタ回路の出力電圧と入力電圧をいつも同じレベルにすることができるので、従来に比べてより低い電源電圧においてもフィルタ回路として正常に動作することができる。

(もっと読む)

アクティブフィルタ

【課題】MOSトランジスタ構成のアクティブフィルタの回路規模を小さくする。

【解決手段】アクティブフィルタ50にはバッファアンプBuff1、バッファアンプBuff2、可変利得増幅器GCA1、抵抗R1a、抵抗R1b、抵抗R2、コンデンサC1a、コンデンサC1b、及びコンデンサC2が設けられる。入力電圧Vinが入力される抵抗R1aとコンデンサC1aからなる第1のRCフィルタ、バッファアンプBuff1、抵抗R2とコンデンサC2からなる第2のRCフィルタ、及びバッファアンプBuff2から2次のサレンキー型フィルタ回路が構成され、出力電圧Voutが出力される。出力電圧Voutは第1のRCフィルタに帰還入力される。入力電圧Vin側と第2のRCフィルタの間には抵抗R1bとコンデンサC1bからなる第3のRCフィルタと可変利得増幅器GCA1が縦続接続される。

(もっと読む)

シュミットトリガ型インバータ

【課題】さらに入力ノイズ耐性を有するシュミットトリガ型インバータを提供すること。

【解決手段】入力側ノードへの供給電圧が増加して第1の基準電圧に達するに従い出力側ノードから出る電圧が比較高電圧レベルから比較低電圧レベルに遷移し、入力側ノードへの供給電圧が減少して第1の基準電圧より低い第2の基準電圧まで減少するに従い出力側ノードから出る電圧が比較低電圧レベルから比較高電圧レベルに遷移するインバータと、インバータの入力側ノードに一方端が接続された第1の抵抗素子と、インバータの入力側ノードに一方端が接続された、該一方端の電圧が上昇するほどに抵抗値が減じる可変抵抗素子と、可変抵抗素子の他方端に一方端が接続された第2の抵抗素子と、ドレインが第2の抵抗素子の他方端に接続され、ゲートがインバータの出力側ノードに接続され、ソースが接地電位に接続されたnチャネルMOSトランジスタとを具備する。

(もっと読む)

サーキュレータ

【課題】アイソレーション特性に優れたサーキュレータを実現すること

【解決手段】ポート2に接続されたアンテナ19とダミー負荷15はともに50Ωである。分配回路10の入力端であるポート1に入力された信号は、逆相で等振幅に分配され、一方は第1ベース接地増幅器11、第1整合回路16、第3ベース接地増幅器13を介して合成器18に入力され、他方は第2ベース接地増幅器12、第2整合回路17、第4ベース接地増幅器14を介して合成器に入力される。ここで、アンテナ19のインピーダンスの変動は、第2ベース接地増幅器12の電流源の電流量と、第2整合回路17の並列可変キャパシタ119のキャパシタンスとを制御することで補償することができる。そのため、合成器18において第3ベース接地増幅器13の出力と第4ベース接地増幅器14との出力は打ち消され、ポート3からは出力されない。

(もっと読む)

移相器

【課題】意図せずに信号線に付加される線路によって移相器の特性が劣化してしまうこと。

【解決手段】移相器50は、LPFとHPF間の切替に基づいて入力信号を移相する。移相器50は、入力端子1と出力端子2間に接続されたFET5と、FET5がオン状態のとき共振する共振回路と、FET5がオン状態のとき、入力端子1及び出力端子2間に形成される信号線路に含まれる節点と共振回路との間に接続される付加線路4a(4b)と、FET5がオン状態のとき、信号線路の一部に含まれ、少なくとも付加線路4a(4b)と共にローパスフィルタを形成するインダクタ3a(3b)と、を備える。FET5がオン状態のときに付加線路と共にLPFを形成するインダクタを信号線路に配置する。これによって、意図しない付加線路によって移相器の特性が劣化することを抑制することができる。

(もっと読む)

フィルタ回路及びフィルタ回路の補正方法

【課題】フィルタ回路で、製造ばらつきに対応して容易に特性周波数のずれを補正すること。

【解決手段】フィルタ回路10はgm値が制御可能なセルと、少なくとも2つのコンデンサを含むフィルタ部11を有し、2つのコンデンサの容量差を検出し、その容量差に応じて生成した制御電圧VCをフィルタ部11のgmセルに供給し、gmセルのコンダクタンス値とコンデンサの容量値との比をそれぞれ等しくする。

(もっと読む)

Gm−Cフィルタ回路及びこれを用いた送受信機

【課題】カットオフ周波数の補正動作中における後段回路の異常動作や電力浪費を解消することが可能なGm−Cフィルタ回路の提供。

【解決手段】Gm−Cフィルタ回路100は、カットオフ周波数の補正動作中に後段回路200への電力供給を停止させる電源遮断部(スイッチ112とこれを制御するフィルタ制御回路110)を有して成る構成とされている。

(もっと読む)

アクティブフィルタの設計

【課題】LCフィルタをシミュレートすることで低素子感度フィルタの実現を可能にするアクティブ低域フィルタ回路を提供する。

【解決手段】信号入力端子から直列に複数個の抵抗Rを接続し、信号入力端子側からの各抵抗の接続点に順次演算増幅器A1、・・・・An−1の非反転入力端、出力端、反転入力端の順に接続し、各演算増幅器の非反転入力端と接地間に従来のLCフィルタの設計法を用いて求めた値のコンデンサC1、・・・・Cn、および演算増幅器の非反転入力端間にC1,3、・・・・Cn−1,nを接続し、前記の直列に接続された複数個の抵抗Rの最終端から出力信号を取り出す。

(もっと読む)

帯域通過フィルタ

【課題】ソースフォロワ回路をベースにした帯域通過フィルタを提供する。

【解決手段】入力信号を入力するMOSトランジスタ101、102、ドレインがMOSトランジスタ101のソースに接続されるMOSトランジスタ103、ドレインがMOSトランジスタ102のソースに接続されるMOSトランジスタ104を含み、MOSトランジスタ103のゲートがMOSトランジスタ104のドレインに接続し、MOSトランジスタ104のゲートがMOSトランジスタ103のドレインに接続されるトランジスタ対、電流源105、106、コンデンサ107、108、MOSトランジスタ101のソースの出力信号とMOSトランジスタ103のソースの出力信号とを加算する加算器109、MOSトランジスタ102のソース端子の出力信号とMOSトランジスタ104のソース端子の出力信号とを加算して出力する加算器110とによって帯域通過フィルタを構成する。

(もっと読む)

周波数特性調整回路、受信インタフェース回路および磁気記憶装置

【課題】伝送路との整合を保持しながら交流結合回路による低域側遮断域を変化させる。

【解決手段】周波数特性調整回路20の遮断域調整部21は、AC結合回路10の周波数特性における低域側遮断域が移動するように、AC結合回路10からの出力信号を通過させる。遮断域調整部21の零点周波数および極周波数は、制御信号に応じて設定される。この制御信号により、遮断域調整部21の伝達関数の分子多項式が、AC結合回路10の伝達関数の分母多項式と等しくされ、遮断域調整部21の零点周波数が、AC結合回路10による低域遮断周波数に合わせられる。このため、AC結合回路10から遮断域調整部21を通過した出力信号は、AC結合回路10により生じた低域遮断域が移動した周波数特性を有するようになる。そして、この周波数特性において、制御信号に応じて設定される遮断域調整部21の極周波数が、移動後の低域側遮断域の遮断周波数となる。

(もっと読む)

フィルタ回路

【課題】平滑用コンデンサに対する充電電流及び放電電流による時定数を大きくした場合であっても、平滑用コンデンサの体格の大型化や、オフセット電圧の増加を抑制することが可能なフィルタ回路を提供する。

【解決手段】入力電圧とフィルタ処理電圧との電圧差に応じた電流を、カスコード型カレントミラー回路を利用して減衰させて、平滑用コンデンサC1の放電電流I11及び放電電流I12を発生させる。さらに、平滑用コンデンサC1の充電電流I12の一部となるベース電流Ib1’を流すトランジスタT23を、トランジスタT24と抵抗R13,R14からなる回路により、フィルタ回路10の後段回路と分離する。

(もっと読む)

低周波透過回路、通信回路、通信方法、通信回路のレイアウト方法

【課題】透過周波数域における利得が一定かつ遮断周波数域への遷移における利得変化が急峻であって、かつ、帯域外抑圧比の大きい低周波透過回路を提供すること。

【解決手段】本発明の一態様は、インダクタ素子を有する低周波透過フィルタ101と、低周波透過フィルタ101に縦続接続され、低周波透過フィルタ101が透過から遮断へ遷移する周波数近傍かつ透過周波数域内に利得の盛り上がりを有する増幅器100と、を備える低周波透過回路である。

(もっと読む)

無線受信機用半導体装置

【課題】マルチバンド無線受信機のバンドパスフィルタを集積回路で構成する場合に、回路規模が大きくなり、チップ面積が大きくなったり、製造コストが高くなる。

【解決手段】混合回路58は無線受信信号SRFをダウンコンバートして中間信号SIFを生成する。IFBPF60は、抵抗R及びキャパシタCを用いたRCアクティブフィルタで構成され、SIFから目的受信信号を抽出する。抵抗Rは、クロック信号SCLによって駆動されるスイッチトキャパシタからなる等価抵抗により構成される。SCLを生成するフィルタ制御クロック生成回路72は、SCLの周波数fCLを、目的受信信号が属するバンドに応じて切り換えることができる。IFBPF60の通過帯域は、クロック周波数fCLによる抵抗Rの等価抵抗値の切り換えにより、受信バンドに対応して変更できる。

(もっと読む)

半導体装置

【課題】温度信号の製造バラツキが小さく、高精度の温度信号を生成可能な電子回路を提供すること。

【解決手段】本発明は、ピンチオフ状態にせしめられる第1FET(FET1)と、第1FETのソース端子S1に接続されてなる温度信号Vtempを出力する温度信号出力端子と、を具備する電子回路である。本発明によれば、ピンチオフ状態のFETのソース端子から出力される温度信号を用いることにより。製造ばらつきの小さい温度信号を得ることができる。

である。

(もっと読む)

フィルタ

【課題】タップ係数として任意の値を設定することができるフィルタを得ることを目的とする。

【解決手段】キャパシタ11,31により充電された電荷とキャパシタ13,33により充電された電荷の総和を出力端子Pに出力し、キャパシタ12,32により充電された電荷とキャパシタ14,34により充電された電荷の総和を出力端子Nに出力する。これにより、キャパシタ11〜14,31〜34の容量値Cpp,Cpn,Cnp,Cnnを適宜変更することで、タップ係数として任意の値を設定することができる。

(もっと読む)

フィルタ回路

【課題】 可変する回路定数を減らし、かつ、回路定数の可変範囲を同じにしても、Qの変動が大きくならないようにする。

【解決手段】 VCVS型の2次HPF20B、30Bを縦続接続し、HPF20Bの内、抵抗値を大から小へ可変したときカットオフ周波数が低から高へ変化し、Qが大から小へ変化する抵抗R22と、HPF30Bの内、抵抗値を大から小へ可変したときカットオフ周波数が低から高へ変化し、Qが小から大へ変化する抵抗R32を互いに連動して抵抗値が可変するようにする。可変抵抗R22とR32を連動して可変したとき、各HPF20B、30BのQが相補的に変動するようにしたので、Qの変動を小さく抑えることができる。各HPF20B、30Bはカットオフ周波数の可変範囲、Qに対する設計自由度が高く、R22とR32の可変範囲を同じにしながらQがほぼ一定にすることができる。

(もっと読む)

MOSトランジスタ抵抗器、フィルタおよび集積回路

【課題】製造上のばらつきによるリーク電流の変化に起因する抵抗値の変動が低減され、かつ温度特性の良好なMOSトランジスタ抵抗器を提供する。

【解決手段】抵抗器として使用される第1MOSトランジスタM1と、第1MOSトランジスタのソースに接続され、入力電圧Vinを印加する入力電圧源1と、第1MOSトランジスタのゲートに接続され、ゲート電圧Vgを印加するゲート電圧源6とを備えたMOSトランジスタ抵抗器。ゲート電圧Vg及び入力電圧Vinは、第1MOSトランジスタのゲート−ソース間電圧及びソース−ドレイン間電圧が、第1MOSトランジスタを非飽和領域で動作させる範囲で印加されるとともに、第1MOSトランジスタの抵抗値における温度特性の温度特性が一定になる条件を満たす関係に設定される。

(もっと読む)

61 - 80 / 279

[ Back to top ]