Fターム[5J098AA14]の内容

能動素子を用いた回路網 (5,588) | 回路素子 (1,159) | コンデンサ (333)

Fターム[5J098AA14]の下位に属するFターム

可変コンデンサ (54)

Fターム[5J098AA14]に分類される特許

41 - 60 / 279

フィルタ回路

【課題】フィルタ回路における信号のロスが生じても、通過すべき周波数の信号と他の周波数の信号との十分な強度比が得られるフィルタ回路を提供する。

【解決手段】信号線110に接続され、信号線110を伝搬する信号をフィルタリングするフィルタ回路を、信号線110ラインから信号を入力し、バッファリングするアンプ回路101と、アンプ回路101によってバッファリングされた信号をフィルタリングするノッチフィルタ108と、ノッチフィルタ108から出力された信号を入力し、入力された信号の周波数分布を反転させて信号線110に出力する−gm回路102と、によって構成する。

(もっと読む)

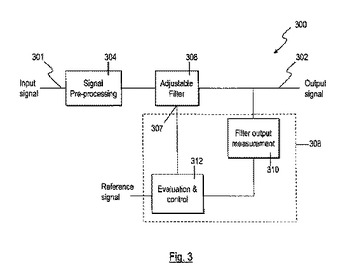

ホイールモニタリングシステムのための追跡フィルタ装置

ホイールモニタリングシステムは、変化する主周波数を有する信号を追跡する追跡フィルタ装置を含む。追跡フィルタ装置は、調整可能なフィルタと、フィルタリングされた信号の振幅を測定し、振幅を基準値に対して比較するように構成されたフィルタコントローラとを備える。フィルタコントローラは、測定された振幅が基準値から所定のしきい値を越える量にわたって相違するとき、フィルタのカットオフ周波数を調整する。フィルタコントローラは、主周波数がフィルタの周波数応答のロールオフ領域内に存在するように、カットオフ周波数を調整する。本システムは、ホイールに設けられたモニタリング装置の衝撃センサによって生成された信号を追跡するために使用可能である。  (もっと読む)

(もっと読む)

アクティブポリフェーズフィルタ

【課題】大電力を入力しても歪の小さいアクティブポリフェーズフィルタを提供する。

【解決手段】npnトランジスタQ1、Q2、Q4及びQ5と、npnトランジスタQ6、Q7、Q4及びQ5は、各々トランスリニアループを形成している。また、npnトランジスタQ2及びQ3と、npnトランジスタQ7及びQ8は各々カレントミラー回路を形成している。こうして、npnトランジスタQ1とQ3の各々のコレクタ電流の差と、npnトランジスタQ6とQ8の各々のコレクタ電流の差とが、いずれも、平衡な高周波入力の電流に等しくなる。このような2組の差動入力を、ポリフェーズフィルタ部10の4入力とすることで、ポリフェーズフィルタ部10の4出力から、偶数次成分の抑制された、位相がπ/2異なる差動出力を得ることができる。

(もっと読む)

回路公差を調節するための回路と方法

【課題】周波数に敏感な回路のための周波数応答調節器、及び回路の周波数応答を調節する方法を提供する。

【解決手段】周波数に敏感な回路の充電状態を第1の電圧として測定し出力する時定数センサと、第1の電圧をサンプルし、第1の電圧を変換して得られる結果である第2の電圧を出力する変換器と、トリミング要素アレイと、トリミング要素アレイから少なくとも1つのトリミング要素を選択するために第2の電圧を利用するセレクタとを含んでいる。この方法は、回路の時定数を感知することと、この感知を第1の電圧として出力することと、第1の電圧を、固定された間隔にわたってサンプルすることと、サンプルした第1の電圧を、第2の電圧に変換することと、第2の電圧を使ってトリミング要素アレイから、少なくとも1つのトリミング要素を選択する。

(もっと読む)

アクティブフィルタ回路

【課題】アナログ式のアクティブフィルタ回路において、起動時に出力が安定するまでの時間の短縮を実現する。

【解決手段】アクティブフィルタ回路は、第1抵抗R1と、演算増幅器3と、第2抵抗Rfと、キャパシタCfと、スイッチSW1とを具備する。演算増幅器3は、+入力端子に基準電圧Vrefを供給され、−入力端子に第1抵抗R1を介して入力電圧Vinを供給される。第2抵抗Rfは、一端を演算増幅器3の出力端子に、他端を−入力端子にそれぞれ接続されている。キャパシタCfは、一端を出力端子に接続されている。スイッチSW1は、起動時にキャパシタCfの他端を+入力端子に接続し、所定時間経過後にキャパシタCfの他端を−入力端子に接続するように切り替わる。

(もっと読む)

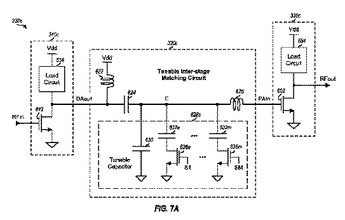

デジタルのチューナブル段間整合回路

性能を改善できるチューナブル段間整合回路について説明する。例示的な設計では、装置は、第1の能動回路(たとえば、ドライバ増幅器)と、第2の能動回路(たとえば、電力増幅器)と、第1の能動回路と第2の能動回路の間に接続されたチューナブル段間整合回路とを含む。このチューナブル段間整合回路は、第1の能動回路と第2の能動回路の間のインピーダンス整合を調整するために個別のステップで変化できるチューナブルキャパシタを含む。例示的な設計では、このチューナブルキャパシタは、(i)並列に接続された複数のキャパシタと、(ii)この複数のキャパシタに対してキャパシタごとに1つ接続された複数のスイッチとを含む。各スイッチは、関連するキャパシタを選択するためにオンにされるか、または関連するキャパシタの選択を解除するためにオフにされることができる。チューナブルキャパシタは、複数のキャパシタと並列に接続された固定キャパシタをさらに含むことができる。  (もっと読む)

(もっと読む)

高周波発振回路

【課題】発振回路の発振周波数を広帯域に制御可能でIC化に適した比較的小規模な発振回路を提供する。

【解決手段】一方の電源に接続される電流源と、他方の電源に接続されて誘導起電力によって電流を変動させる1組の負荷インダクタと、前記電流源と前記負荷インダクタとそれぞれに結合する1組の差動回路と、前記一方の差動回路の入力と前記他方の差動回路の出力との間に抵抗値を制御可能な可変抵抗を備えて正帰還が掛るように構成されて、前記可変抵抗の抵抗値に対応して発振周波数が定まる高周波発振回路である。

(もっと読む)

フィルタ回路及び通信装置

【課題】寄生容量に起因する周波数特性の変化を確実に抑えること。

【解決手段】入力端に入力された電圧信号を電流信号に変換する電圧電流変換部106と、複数のキャパシタから構成され、電圧電流変換部106から出力された電流信号が周期毎に各キャパシタへ順次に入力され、電流信号が入力された1群のキャパシタの電荷を加算して出力する第1のキャパシタ集合体102と、複数のキャパシタから構成され、第1のキャパシタ集合体102から出力された電流信号が周期毎に各キャパシタへ順次に入力され、電流信号が入力された1群のキャパシタの電荷を加算して出力する第2のキャパシタ集合体104と、第1のキャパシタ集合体102において電荷を出力する任意のキャパシタと、当該電荷の出力による電流信号が入力される第2のキャパシタ集合体104のキャパシタとを個々に接続する複数の接続ノード110,112,114,116と、を備える。

(もっと読む)

遅延回路

【課題】矩形波を入力される遅延回路において、入力信号にノイズパルスが存在すると、出力信号のジッターが生じる。

【解決手段】シュミットコンパレータ102からの出力信号VdoでスイッチSW3を制御し、コンデンサCstへの充電電流を供給する電流源I1と、放電電流を供給する電流源I2とのいずれかを選択する。入力信号VdiでスイッチSW1,SW2を制御することで、選択された電流源からの電流供給がオン/オフされる。シュミットコンパレータ102はコンデンサCstの電圧Vstに応じてVdoを切り替える。Vdiの立ち上がり時には、VdiのHレベル期間にてコンデンサCstへ充電電流を供給し、Vdiの立ち下がり時には、VdiのLレベル期間にてコンデンサCstへ放電電流を供給する。

(もっと読む)

容量増倍回路

【課題】半導体材料に起因するhfeのばらつきなどに影響されることなく、安定した増倍率を確保する。

【解決手段】カレントミラー比が共に1:Nに設定された第1及び第2のカレントミラー回路21,22の各々の入力段の間に、第1及び第2のトランジスタ1,13がトーテムポール接続により直列接続されて設けられ、この第1及び第2のトランジスタ1,13の相互の接続点に容量3の一端が接続され、容量3の他端は、入力信号が印加可能とされ、第1及び第2のカレントミラー回路21,22の出力段は、相互に接続されて信号出力可能とされると共に、容量3の他端に接続されて、信号入力端子8から見た容量3の見かけ上の容量値が(1+N)倍に見えるものとなっている。

(もっと読む)

フィルタ回路及び通信装置

【課題】電荷の移動に伴う過渡現象が出力に与える影響を抑止すること。

【解決手段】入力端に入力された電圧信号を電流信号に変換するトランスコンダクタンスアンプ102と、複数のキャパシタから構成され、トランスコンダクタンスアンプ102から出力された電流信号が周期毎に各キャパシタへ順次に入力されるキャパシタ集合体と、電流信号が入力された1群のキャパシタを互いに接続し、当該1群のキャパシタに蓄積された電荷を加算するシェアスイッチS1aS〜S4aS,S1bS〜S4bSと、シェアスイッチS1aS〜S4aS,S1bS〜S4bSにより電荷が加算された後、1群のキャパシタのうちの少なくとも1つのキャパシタを出力端に接続するダンプスイッチS1aD〜S4aDと、を備える。

(もっと読む)

差動電流信号を単一終結信号に変換する回路

【課題】差動電流信号を単一終結信号に変換するミキサ回路を提供する。

【解決手段】多くの適用が差動電流信号の単一終結信号への変換を必要とする。存在しているアプローチで遭遇する欠点は、乏しい変換効率、制限された帯域幅、および大きなサイズを含む。開示された変換器は、小さなサイズおよび作動の広い帯域幅を有している高効率のユニットを得るために能動装置を使用する。

(もっと読む)

寄生容量により誘導される誤差が減少されたセンサデバイス

デバイス110は、駆動ノード34,36および感知ノード42,44を有する感知素子26を備えている。駆動ノード34および感知ノード42との間には寄生容量22が存在する。同様に、駆動ノード36と感知ノード44との間には寄生容量24が存在する。駆動信号56が駆動ノード34、36との間に印加されると、駆動ノード34と感知ノード42との間の寄生電流70および駆動ノード36と感知ノード44との間の寄生電流72が寄生容量22,24のおかげで生成される。容量性ネットワーク112を介して寄生電流70を打ち消す補正電流134を生成するために、駆動ノード36と感知ノード42との間に容量ネットワーク112が接続される。同様に、容量性ネットワーク112を介して寄生電流72を打ち消す補正電流138を生成するために、駆動ノード34と感知ノード44との間に容量性ネットワーク114が接続される。  (もっと読む)

(もっと読む)

フィルタ回路

【課題】高速でかつ低消費電流であり、MOSトランジスタのしきい値電圧の絶対値が低い場合でも入力信号レベルを大きくすることができるフィルタ回路を提供する。

【解決手段】ゲートから信号を入力するMOSトランジスタ(Tr)1、Tr2、ドレインがMOSトランジスタ1のソースに接続され、ゲートがMOSトランジスタ2のソースに接続されるTr3、ドレインがTr2のソースに接続され、ゲートがTr1のソースに接続されるTr4、Tr3のソースに電流を供給する電流源5、Tr4のソースに電流を供給する電流源6、Tr1〜Tr4のソースの各々に接続されるコンデンサ7、8を含むフィルタ回路に、Tr3、Tr4の動作点が飽和領域内の線形領域に近い側から遠い側に向かう方向にシフトするように電圧を印加する電圧源101、102を設ける。

(もっと読む)

増幅装置、センサモジュール

【課題】増幅装置にバンドパスフィルタを持たせる。

【解決手段】ローパスフィルタ回路11は、センサ信号(SIN)が供給される第1の入力端子と、第2の入力端子と、出力信号(SOUTP)を出力するための出力端子とを有する。ローパスフィルタ回路(12)は、ローパスフィルタ回路(11)の第2の入力端子に接続された入力端子と、出力端子とを有する。ローパスフィルタ回路(13)は、ローパスフィルタ回路(12)の出力端子に接続された入力端子と、出力信号(SOUTN)を出力するための出力端子とを有する。

(もっと読む)

遅延回路および半導体装置

【課題】入力信号を遅延させ出力する遅延回路において、動作時の消費電流低減をはかる。

【解決手段】遅延回路100の端子202に、Pチャネル型MOSトランジスタ105を介して容量素子107を接続する。NAND回路104は、入力端子が、遅延回路100の入力端子201とインバータ103へ接続され、出力端子がPチャネル型MOSトランジスタ105のゲート端子へ接続される。インバータ103は、入力端子が遅延回路100の出力端子へ接続される。Pチャネル型MOSトランジスタ105は、遅延回路100の出力信号がLレベルからHレベルに遷移することに応答して、端子202と容量素子107を電気的に非接続とする。

(もっと読む)

バイアス回路及びそれを備えたgm−Cフィルタ回路並びに半導体集積回路

【課題】実装面積の増加を抑えつつ、温度変動や閾値電圧Vthの製造バラツキでの影響を抑えることができるバイアス回路及びそれを備えたgm−Cフィルタ回路並びに半導体集積回路を提供すること。

【解決手段】第1電流源Iaをなす第1のPMOSトランジスタQ1と、第1のPMOSトランジスタQ1のカレントミラー回路を構成し、第2電流源Ibをなす第2のPMOSトランジスタQ2と、第1電流源Iaからそのドレインに電流が供給される第1のNMOSトランジスタQ3と、第1のNMOSトランジスタQ3とカレントミラー回路を構成し、第2電流源Ibからそのドレインに電流が供給される第2のNMOSトランジスタQ4と、第2のNMOSトランジスタQ4のソースとグランドとの間に接続された抵抗とを備え、さらに、第1のNMOSトランジスタQ3のソースとグランドとの間にgm調整用の抵抗成分Zrを接続した。

(もっと読む)

フィルター回路

【課題】入力信号の周波数が高くなるほど出力信号の入力信号に対する相対的な位相が進行し、入力信号の周波数が低くなるほど出力信号の入力信号に対する相対的な位相差がなくなる周波数領域を使用するフィルター回路を得る。

【解決手段】抵抗とコンデンサによって構成されるフィルター回路において、入力端子Iと接地端子Gの間に第1の抵抗R1と第2の抵抗R2とコンデンサCがこの順番で直列に接続され、第1の抵抗R1と第2の抵抗R2の接続点に出力端子Oが設けられており、第1の抵抗R1と第2の抵抗R2の合成抵抗値とコンデンサCの静電容量値によって決定されるカットオフ周波数より高い周波数領域にある最大位相遅延周波数より高い周波数領域を使用することにより、入力信号の周波数が高くなるにつれて、出力信号の入力信号に対する相対的な位相の遅れが小さくなる特性を発揮するフィルター回路による。

(もっと読む)

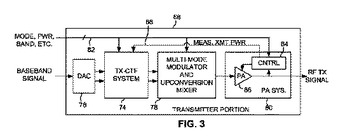

プログラム可能送信連続時間フィルタ

プログラム可能電流の送信連続時間フィルタ(TX−CTF)システムは無線周波数(RF)送信機に含まれ得る。TX−CTFの入力はベースバンド送信信号を受信することができ、TX−CTFの出力はアップコンバージョンミキサに供給されて、送信用のRFに変換され得る。TX−CTFは、フィルタパラメータをともに規定する増幅回路および受動回路を含む。TX−CTFはさらに、プログラム可能バイアス電流を増幅回路に供給するプログラム可能電流回路を含む。TX−CTFシステムはまた、1つ以上の送信機制御信号を受信し、これに応じて、TX−CTFに供給されるバイアス電流を制御する信号を生成する制御論理を含む。  (もっと読む)

(もっと読む)

フィルタ回路、連続時間フィルタ及び信号再生装置

【課題】周波数帯域を制限するフィルタ回路に関し、周波数とは、独立に利得を調整する。

【解決手段】第1の電圧/電流変換回路(12)に、係数設定回路(16)からの第1の制御信号と利得調整のための第2の制御信号とから作成した第3の信号を入力し、第2の電圧/電流変換回路(14)に、第1の制御信号を入力する。このため、周波数と、利得を独立に制御したフィルタを実現できる。

(もっと読む)

41 - 60 / 279

[ Back to top ]