Fターム[5J098AA14]の内容

能動素子を用いた回路網 (5,588) | 回路素子 (1,159) | コンデンサ (333)

Fターム[5J098AA14]の下位に属するFターム

可変コンデンサ (54)

Fターム[5J098AA14]に分類される特許

81 - 100 / 279

移相回路

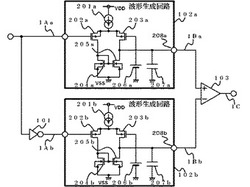

【課題】入力信号の周波数に依存せずに入力信号に対して所定の位相差を有する出力信号を生成する。

【解決手段】VDDから定電流を供給する定電流回路201aと、入力電流に対してn倍の出力電流を流すカレントミラー回路204a、205aと、矩形波の入力信号1Aaの論理レベルによって定電流回路に流れる電流をカレントミラー回路に流すか、出力端子1Baに流すか切り替えるスイッチ回路202a、203aとを備えた波形生成回路102aにより、立ち上がり勾配1に対してn倍の立ち下がり勾配波形を有する三角波を生成する。これと反転信号1Abを入力した波形生成回路102bにより生成した三角波の電圧をコンパレータ103で比較し出力信号を生成する。入力信号のデューティー比が50%である場合には、1/(2+2n)周期遅延した出力信号が得られる。

(もっと読む)

移相回路

【課題】低損失化を図ることができるとともに、小形化を図ることができる移相回路を得る。

【解決手段】第1の入出力端子1aと、第2の入出力端子1bと、第1の入出力端子1aと第2の入出力端子1bの間に接続された第1のスイッチング素子2aと、第1の入出力端子1aに一端が接続された第1のキャパシタ3aと、第2の入出力端子1bに一端が接続された第2のキャパシタ3bと、第1及び第2のキャパシタ3a、3bの他端とグランド4の間に接続された第2のスイッチング素子2bとを設けた。

(もっと読む)

パルス伸長回路及び半導体装置

【課題】幅のより短いパルスに対して伸長が可能なパルス伸長回路及び半導体装置を提供する。

【解決手段】それぞれのソースが定電流源21を介して電源端子5に接続され、それぞれのドレインが定電流源21より電流駆動能力の大きな定電流源22を介して接地端子6に接続され、ゲートが入力端子27に接続されたp‐MOSトランジスタP1及びゲートが出力端子28に接続されたp‐MOSトランジスタP2と、一端がp‐MOSトランジスタP1、P2のソースと定電流源21との間に接続され、他端が接地端子6に接続されたキャパシタC1と、ドレインがp‐MOSトランジスタP2のゲートに接続され、且つ定電流源23を介して電源端子5に接続され、ソースが接地端子6に接続され、ゲートがp‐MOSトランジスタP1、P2のドレインと定電流源22との間に接続されたn‐MOSトランジスタN1とを備える。

(もっと読む)

Gm−Cフィルタをチューニングする装置および方法

チューナブルGm−Cフィルタを制御する装置であって、出力増幅器(304)の帰還符号を切り換えることによって自励発振器として再構成することのできるフィルタと、キャリブレーション構成においてフィルタの出力を検知するディジタルコントローラ(42)と、フィルタを含む相互コンダクタンス増幅器(310、320)のgm入力にアナログ制御信号(48)を提供するDAC(44)とを備える。 (もっと読む)

パッシブイコライザ

【課題】ゲインを増大させるために負のインピーダンスを用いることができるパッシブイコライザを提供する。

【解決手段】

ゲインを増大させるために負のインピーダンスを利用するパッシブイコライザは、第1のRCループと、第2のRCループと、カスケードRL回路および交差結合反転器ユニットとを含む。第1のRCループおよび第2のRCループのそれぞれは、第1の抵抗器と、ノードで第1の抵抗器に直列に接続され、それによって抵抗器直列を形成する第2の抵抗器と、抵抗器直列に並列に接続されるコンデンサとを含む。カスケードRL回路は、RCループの間に接続され、第5の抵抗器と、第6の抵抗器と、第5の抵抗器と第6の抵抗器との間に接続されるインダクタとを含む。優れた高周波数ゲインを得るために負のインピーダンスの特徴を用いるために、交差結合反転器ユニットは、RL回路に並列に接続され、RCループの間に接続される。

(もっと読む)

アクティブバラン回路

【課題】アクティブバラン回路をMMIC化が容易な小型の構成にする。

【解決手段】平衡入力の一方を増幅し180度位相が回転した信号を取り出すN形電界効果トランジスタを有する第1の増幅回路と、平衡入力の他方を増幅し同位相の信号を取り出すP形電界効果トランジスタを有する第2の増幅回路と、第1および第2の増幅回路の出力信号を合成して不平衡出力として取り出す合成回路を備えたものである。

(もっと読む)

受信素子

【課題】バンドパスフィルタの中心周波数の調整を不要とすることで、煩雑な調整工程を省略することができる受信素子を提供する。

【解決手段】受信素子3は、受信信号の搬送波近傍の周波数帯域を通過させる中心周波数を有し、前記中心周波数が調整可能なバンドパスフィルタ(BPF)部3bと、BPF部3bからの出力信号を復調する復調回路部3cと、受信信号が入力され、中心周波数が遮断周波数に設定されたハイパスフィルタ(HPF)部3duおよびローパスフィルタ(LPF)部3dwと、HPF部3duおよびLPF部3dwのそれぞれの出力信号の電圧レベルを比較する比較回路部3dyと、比較回路部3dyで比較した結果、HPF部3duからの出力信号の電圧レベルが高ければ中心周波数を上昇させ、LPF部3dwからの出力信号の電圧レベルが高ければ中心周波数を低減させるようBPF部3bを調整するバイアス回路部3dzとを備えている。

(もっと読む)

信号処理回路

【課題】良好な入力インピーダンス整合特性を維持しながら低雑音化が可能となる増幅回路を有する信号処理回路を提供することを課題とする。

【解決手段】入力端子に入力された信号を増幅して出力端子から出力するゲート接地増幅回路(111)と、前記ゲート接地増幅回路の入力端子及び出力端子間に接続される帰還インピーダンス回路(Zf)と、前記ゲート接地増幅回路の出力端子から出力される信号を周波数変換し、相互に直交関係にあるI相信号及びQ相信号をI相信号用出力端子及びQ相信号用出力端子から出力する直交スイッチングミキサ(113)と、前記直交スイッチングミキサのI相信号用出力端子及びQ相信号用出力端子に接続される周波数フィルタ(116)とを有することを特徴とする信号処理回路が提供される。

(もっと読む)

差動単相変換回路

【課題】差動単相変換回路におけるチップ面積の縮小又は同相ノイズ信号の除去又は電力損失の低下を図る。

【解決手段】差動信号が入力され単相信号が出力される差動単相変換回路10であって、差動信号の一方が入力される制御端子、第1端子、及び第2端子を有する第1トランジスタM2と、接地された制御端子、第1トランジスタの第1端子に接続される第2端子、及び差動信号の他方が入力されるとともに、出力信号が出力される第1端子を有する第2トランジスタM3とを有するカスコード増幅器、第1トランジスタの第2端子に接続される位相調整用容量C2、及び、第1トランジスタの第2端子に接続される電流源M1、を備える差動単相変換回路が提供される。

(もっと読む)

アクティブ接地キャパシター

【課題】接地キャパシターのキャパシタンスを拡大する手段を提供する。

【解決手段】第一の抵抗1とキャパシター2で構成される低域通過濾波器の前段及び後段に電圧利得が+1未満で限りなく+1に近く、入力インピーダンスが十分に高く、出力インピーダンスが十分に低い前置増幅器3と後置増幅器4を接続し、さらに前置増幅器3の入力端と後置増幅器4の出力端を第二の抵抗5で接続し、第一の抵抗1の抵抗値は第二の抵抗5の抵抗値よりも大きくして実現する。

(もっと読む)

ローパスフィルタおよび半導体圧力センサ装置

【課題】カットオフ周波数が低い場合であっても、電源オンの後速やかに出力を安定させる。

【解決手段】電源オンから整定化時間Tsが経過するまでは、フィルタ動作有効化信号φ3をオフにするとともに第1相、第2相クロックパルスφ1、φ2をともにオンにして、アナログスイッチS11〜S26をオン、アナログスイッチS37をオフにする。整定化時間Tsが経過した後は、フィルタ動作有効化信号φ3をオンにするとともに第1相、第2相クロックパルスφ1、φ2を互いにオン期間が異なるように2相動作させ、スイッチトキャパシタフィルタとして動作させる。

(もっと読む)

電流方式ローパスフィルタ

【課題】回路規模の小さい電流方式ローパスフィルタを提供する。

【解決手段】ローパスフィルタ10は、入力端子12と、出力電圧発生ノード16と、電源Vccから入力端子12に定電流Iconst1を供給する定電流源48と、電源Vccから出力電圧発生ノード16に定電流Iconst2を供給する定電流源50と、出力電圧発生ノード16に接続された入力を有するボルテージフォロワ回路34と、ボルテージフォロワ回路34の出力と入力端子12との間に接続された抵抗36と、出力電圧発生ノード16に接続された容量20と、ベース接地トランジスタ62と、カレントミラー回路28と、ボルテージフォロワ回路34の出力に接続された出力端子14とを備える。

(もっと読む)

キャパシタンス乗算器回路

キャパシタンス乗算器回路が、追加の回路を追加することまたは追加の電力を必要とすることなしにキャパシタンス乗算器効果を達成するために、回路のRCフィルタ中のキャパシタを通る電流を検知し、その電流を乗算するように構成される。回路は、RCフィルタと、フィルタ出力に接続された第1の信号経路と、フィルタに入力に接続された第2の信号経路とを含む。フィルタを通る電流出力(iout)は、2つの経路に分割され、第1の経路において検知され、第2の経路において乗算される。乗算された電流は、キャパシタCの実効キャパシタンスを上げるために第2の経路からフィルタ入力にフィードバックされる。キャパシタンス乗算器回路は、フィルタ中のキャパシタの実効キャパシタンスを上げる際に、全体的な回路の周波数応答、直線性性能および/または安定性に影響を及ぼさない。  (もっと読む)

(もっと読む)

フィルタ回路

【課題】 少ない回路素子数で周波数帯域分割を可能とする。

【解決手段】 12は非反転入力が接地され、出力側が第1出力端子13とコンデンサCfを介して反転入力と接続された演算増幅器、R1〜R3は固定抵抗であり、入力端子10と演算増幅器12の出力間にR1とR2が直列に接続され、R1とR2の接続点Pと演算増幅器12の反転入力の間にR3が接続されている。接続点PにはコンデンサCが接続されている。20は電流/電圧変換部であり、この内、21は非反転入力が接地され、出力側が第2出力端子22と抵抗Rfを介して反転入力と接続された演算増幅器である。Cの他端は演算増幅器21の仮想接地された反転入力と接続されており、LPF部11は多重帰還形2次LPFを構成する。入力端子−第1出力端子間の伝達関数は2次LPFの形式、入力端子−第2出力端子間の伝達関数は2次HPFの形式となり、カットオフ周波数f0とQは同じになる。

(もっと読む)

フィルタ回路及びその制御方法

【課題】CMCの正極側巻線と負極側巻線に流れる電流を等しくし、所望の特性を得るようにしたフィルタ回路の提供。

【解決手段】コモンモードノイズフィルタの正極側巻線と、負極側巻線に流れる電流を監視する手段(2、3)と、監視結果に基づき、正極側巻線と負極側巻線が互いに等しくなるように調整する手段(4、5、6)を備える。

(もっと読む)

アクティブインダクタおよび差動アンプ回路

【課題】低電源電圧下においても、半導体集積回路上での面積および消費電力の増大を抑えつつ、高域での利得のピーキングの傾きを急峻化する。

【解決手段】P型電界効果トランジスタM1のソースを電源電位VDDに接続し、P型電界効果トランジスタM1のドレインを出力端子outに接続し、N型電界効果トランジスタM2のドレインを電源電位VDDに接続し、N型電界効果トランジスタM2のソースを電流源IBを介して接地電位に接続し、P型電界効果トランジスタM1のゲートをN型電界効果トランジスタM2のソースに接続し、N型電界効果トランジスタM2のゲートを抵抗素子Rpを介してP型電界効果トランジスタM1のドレインに接続する。

(もっと読む)

低域ろ波回路

【課題】容量素子の小型化を図る低域ろ波回路(ループフィルタ)において、容量素子としてMOS容量を使用した場合の電圧依存によるPLL応答特性のばらつきと、MOS容量として薄膜ゲートトランジスタを使用した場合のゲートリーク電流によるジッタ特性の劣化を抑制する。

【解決手段】ループフィルタは、第1の容量素子31と、この容量素子31に直列に接続された抵抗素子32及び第2の容量素子33とを備える。前記第1の容量素子31の一端に接続された第1の入力端IN1に第1の電流(Ip/10)を与え、前記第1の容量素子31の他端に接続された第2の入力端IN2に第2の電流(Ip/10)を与えることにより、第1の容量素子31の小型化が図られる。前記抵抗素子32に直列に接続された可変電圧電源35は、電圧制御端子36から、第1の容量素子31の両端の印加電圧が一定になるように制御される。

(もっと読む)

広帯域分配器

【課題】出力端子に高電圧が入力された場合でもその影響をより少なくするとともに、広帯域なアイソレーション特性を持つ広帯域分配器を提供する。

【解決手段】入力端子1に一端が接続された第1の容量5と、前記第1の容量の他端にゲート端子が接続された第1のFET6と、前記第1のFETのドレイン端子と第1の容量の一端の間に接続された第1のフィードバック回路4と、第1のFETのソース端子6Sとグランド間に接続された第1のソース回路7と、第1のFETのドレイン端子と第1の出力端子2間に接続された第2の容量8とからなる第1の増幅器と、前記入力端子と第2の出力端子3間に接続され、第3の容量10、第2のFET11、第2のフィードバック回路9、第2のソース回路12及び第4の容量13からなる第2の増幅器と、第1のFETのソース6Sと第2のFETのソース11S間に接続されたアイソレーション回路14により構成される。

(もっと読む)

交流直流分離回路

【課題】交流成分に対して比較的高い入力インピーダンスを確保しながらも、従来構成に比べてインダクタの必要数を低減することができる交流直流分離回路を提供する。

【解決手段】ボルテージフォロア回路2は、第1のインダクタL1の一端と基準電位点との間の交流電圧と同振幅且つ同位相の交流電圧を第1のインダクタL1の他端と基準電位点との間に出力する。フィルタ回路3は、第1のインダクタL1の前記他端にコレクタが接続され、第1のインダクタL1の前記他端に抵抗R2を介してベースが接続され、直流出力端子Tdcにエミッタが接続されたトランジスタTr1と、トランジスタTr1のベースと前記基準電位点との間に挿入されたキャパシタC3とを有する。

(もっと読む)

ボーカルカット回路

【課題】回路規模が小さいボーカルカット回路を提供する。

【解決手段】入力端子21及び22に、それぞれLチャネル信号及びRチャネル信号が入力される。入力端子21に入力されたLチャネル信号はそのまま加算器24に入力され、入力端子22に入力されたRチャネル信号はオールパスフィルタ23を通過した後、加算器24に入力される。オールパスフィルタ23は、Rチャネル信号の全周波数範囲の信号を通過させ、その位相のみを変化させる。これによって、Lチャネル信号とRチャネル信号に含まれるボーカル成分の位相がずらされるので、加算器24の加算出力のボーカル成分が減衰される。

(もっと読む)

81 - 100 / 279

[ Back to top ]