Fターム[5J098AA14]の内容

能動素子を用いた回路網 (5,588) | 回路素子 (1,159) | コンデンサ (333)

Fターム[5J098AA14]の下位に属するFターム

可変コンデンサ (54)

Fターム[5J098AA14]に分類される特許

21 - 40 / 279

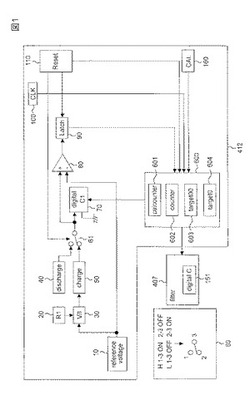

カットオフ周波数自動調整回路及び携帯情報端末

【課題】フィルタのカットオフ周波数を、その調整範囲内の任意の設定値に自動調整可能にする。

【解決手段】電圧電流変換回路(30)、充電回路(50)、放電回路(40)、複数の静電容量を有するデジタル容量(70)、上記デジタル容量に入力される電圧と基準電圧との対比を行う比較器(80)及び上記デジタル容量を制御する容量制御回路(600)を含んでカットオフ周波数自動調整回路(412)を構成する。上記リセット信号が所定の論理レベルになったときから、上記比較器によって上記デジタル容量に入力される電圧が上記基準電圧より高くなったことが検知されるまでの時間を計測し、その計測結果と、上記デジタル容量の目標値と、上記デジタル容量の現在の値とに基づいて上記デジタル容量の次の設定値を求める処理を、所定の条件下で繰り返すことによって上記デジタル容量を制御する。上記目標値は、調整範囲内の任意の設定値とすることができる。

(もっと読む)

電磁誘導型埋設物探査装置

【課題】デジタル信号処理装置(略称「DSP」)による電磁誘導型埋設物探査装置では、デジタル化時の量子化レベル等の制約によって十分な感度が得られず、非金属管路に収容される光ファイバーケーブルを、手軽な間接法によって検出することが難しかった。

【解決手段】本発明の水晶アクティブフィルタは中心周波数の調整機能と水晶振動子の破損防護機能を有しており、多段接続により超狭帯域かつ高DU比のフィルタを容易に構成することができ、高感度の電磁誘導型埋設物探査装置を実現することができる。これによって、非金属管に収容される光ファイバーケーブルを、間接法によって検出することが可能となる。

(もっと読む)

ソースフォロワ回路、ソースフォロワ型フィルタ回路

【課題】入力MOSトランジスタのオーバードライブ電圧が低い場合でも、出力信号が歪まないソースフォロワ回路を提供することを目的とする。

【解決手段】ソースフォロワ回路を、MOSトランジスタ(Tr)1、Tr2でなるTr対、ドレインがTr1のソース及び出力端子17に接続するTr3、ドレインがTr2のソース及び出力端子18に接続するTr4でなるTr対、ゲートとドレインがTr3のゲートに接続してTr3と電流ミラーを構成するTr7、Tr7のドレインに接続してTr7に電流を供給する電流源9、ゲートとドレインがTr4のゲートに接続してTr4と電流ミラーを構成するTr8、Tr8のドレインに接続してTr8に電流を供給する電流源10、Tr7のゲートと出力端子18との間に接続される容量素子11、Tr8のゲートと出力端子17との間に接続される容量素子12によって構成する。

(もっと読む)

オペレイショナル・トランスコンダクタンス・アンプ、オペレイショナル・トランスコンダクタンス・アンプを用いたフィルタ回路

【課題】入力電圧範囲を広くしても線形性能の優れ、かつトランスコンダクタンス値精度の優れたOTA、OTAを用いたフィルタ回路を提供する。

【解決手段】I−V変換器と、内部抵抗素子の抵抗値に比例する増幅率でI−V変換器の出力電流を増幅する電流制御回路1、2とによってOTAを構成する。そして、電流制御回路1、2を、入力電流が入力されるドレイン、第1制御電圧が供給されるゲートを有するMOSトランジスタ10、出力電流が出力されるドレインを有するMOSトランジスタ13、第2制御電圧が供給されるゲートを有するMOSトランジスタ11、MOSトランジスタ10のドレインと接続される非反転入力端子、MOSトランジスタ13のゲートと接続される出力端子、MOSトランジスタ13のソース及びMOSトランジスタ11のドレインと接続される反転入力端子を有する差動増幅器12によって構成する。

(もっと読む)

半導体装置

【課題】半導体装置は、必要に応じてダイナミックレンジを確保し、且つ低消費電流化に資するフィルタ回路を備える。

【解決手段】半導体装置は、トランスコンダクタンス増幅器(103a〜103d、203a〜203d)とキャパシタ(104a、104b)から構成されるフィルタ回路(10、20)を有し、前記フィルタ回路は、妨害信号の電界強度を検出し、検出結果に基づいて、前記トランスコンダクタンス増幅器の差動入力段トランジスタのソース側のインピーダンスと前記トランスコンダクタンス増幅器のバイアス電流の双方を調整するための制御を行う。

(もっと読む)

可変利得減衰器

【課題】特性劣化を引き起こす容量結合をしないで次段増幅器と接続でき、非常に広い周波数範囲に渡って同様の特性で、入力される高周波信号の利得を適切に減衰させて次段増幅器に伝達できる可変利得減衰器を提供すること。

【解決手段】高周波信号を入力するための入力ポート18と、高周波信号を出力するための出力ポート19と、外部からバイアス電圧を印加するためのバイアスポート20と、入力ポートと出力ポートとの間に直列に接続され、それぞれ同等の制御電圧により利得が制御されるMOSトランジスタ10,11と、MOSトランジスタ10,11の直列接続端とグランドとの間に接続され、MOSトランジスタ10,11に適用する制御電圧とは逆特性の制御電圧によって利得が制御されるMOSトランジスタ12とを備え、3つのMOSトランジスタの各バックゲート端子は共通にバイアスポートに接続されている。

(もっと読む)

スイッチトキャパシタフィルタ及びスイッチトキャパシタフィルタの制御方法

【課題】簡易な構成により雑音を低減することができるスイッチトキャパシタフィルタ及びその制御方法を提供すること。

【解決手段】本発明では、演算増幅器AMPの反転入力は積分キャパシタC0の一端と、出力は積分キャパシタC0他端と接続される。スイッチトキャパシタは第1〜3の順に接続状態が移行する。第1の接続状態では、第1の端子は入力信号と、第2の端子は固定電圧と接続される。第2の接続状態では、第1の端子は固定電圧と、第2の端子は演算増幅器AMPの反転入力と接続される。第3の接続状態では、第1の端子は演算増幅器AMPの出力と、第2の端子は演算増幅器AMPの反転入力と接続される。第2及び第3の接続状態のスイッチトキャパシタが各1個以上存在する場合の第2の接続状態のスイッチトキャパシタの個数は常に同じであり、第3の接続状態のスイッチトキャパシタの個数も常に同じである。

(もっと読む)

高インピーダンス回路、フィルタ回路及び増幅回路

【課題】従来技術の高インピーダンス回路は、温度変化等の影響を受けて、高いインピーダンスを維持することができないという問題があった。

【解決手段】本発明にかかる高インピーダンス回路は、ダイオード接続されたトランジスタ21,22を備え、トランジスタ21のバックゲートとトランジスタ22のソースとが接続され、トランジスタ22のバックゲートとトランジスタ21のソースとが接続される。このような回路構成により、温度変化等の影響を抑え、高いインピーダンスを維持することができる。

(もっと読む)

時定数調整回路

【課題】参照用の時定数発生回路を集積回路の外部に用意すると、集積回路の端子数の増加および半導体チップ面積の増大を招き、その結果、製造コストが増大してしまう。また、集積回路単体では時定数の調整を行えない。

【解決手段】スイッチトキャパシタを用いることで、時定数発生回路を集積回路に内蔵しても十分な精度が保たれる。さらに、時定数の補正結果を記憶する記憶部を設けることで、時定数調整用回路と、時定数調整後の通常動作用回路を、一部兼用することが可能となる。集積回路の端子数と、半導体チップ面積を節約でき、その結果、製造コストを抑えられる。さらに、外部から電源さえ供給されれば、自動的かつ自律的に時定数の調整を行える。

(もっと読む)

スイッチトキャパシター回路を用いたハイパスフィルター及び電子機器

【課題】設計の自由度を失うことなく、SC回路を構成するスイッチのクロック周波数を高く、且つカットオフ周波数を低くする場合において面積をより小さくできるSC回路を用いたHPF等を提供する。

【解決手段】スイッチトキャパシター回路を用いたM(Mは2以上の整数)次のハイパスフィルター10は、第1の入力端、第2の入力端及び出力端を備える第1のオペアンプをOP1と、第1の入力キャパシターC1とを有する第1のスイッチトキャパシター積分器1001を含み、第1の入力端に、前記ハイパスフィルター10の入力信号VINが供給され、第2の入力端に、出力端から帰還された帰還信号が第1の入力キャパシターC1を介して供給され、出力端からハイパスフィルター10の出力信号VOUTが出力される。

(もっと読む)

スイッチトキャパシター回路を用いたハイパスフィルター及び電子機器

【課題】設計の自由度を失うことなく、SC回路を構成するスイッチのクロック周波数を高く、且つカットオフ周波数を低くする場合において面積をより小さくできるSC回路を用いたHPF等を提供する。

【解決手段】スイッチトキャパシター回路を用いたM(Mは2以上の整数)次のハイパスフィルターは、第1の入力端、第2の入力端及び出力端を備える第1のオペアンプOP1と、第1の入力キャパシターC1と、出力端から帰還される帰還信号に対してハイパスフィルターのゲイン調整を行うゲイン調整回路GA1とを有する第1のスイッチトキャパシター積分器1001を含み、第1の入力端に、ハイパスフィルターの入力信号VINが供給され、第2の入力端に、帰還信号が第1の入力キャパシターC1を介して供給され、出力端からハイパスフィルターの出力信号VOUTが出力される。

(もっと読む)

フィルタ回路

【課題】フィルタ特性の可変幅が細かく且つ範囲が広い場合であっても、回路の増大を抑制できると共に、コストを抑制し得るフィルタ回路を提供する。

【解決手段】フィルタ回路2のフィルタ特性を決定する少なくとも1種の素子3の素子値を、動作クロックCLKに基づきデジタルコード入力Codeをシグマデルタ変調するΣΔ変調器1の出力、或いは該ΣΔ変調器1の出力をコード変換するデコーダ4を介した信号に基づき変化させる。

(もっと読む)

フィルタ回路

【課題】 回路規模を増大させることなく、コモンモードノイズを除去できるフィルタ回路を提供すること。

【解決手段】 フィルタ回路1は、オペアンプQ1と、オペアンプQ1の非反転入力端子と入力信号源との間に接続された抵抗R2と、オペアンプQ1の非反転入力端子に接続されたコンデンサC3と、オペアンプQ1の非反転入力端子に接続された抵抗R3と、オペアンプQ1の反転入力端子と入力信号源との間に接続された抵抗R4と、オペアンプQ1の反転入力端子と出力端子との間に接続されたコンデンサC4と、オペアンプQ1の反転入力端子に接続された抵抗R5とを備える。抵抗2の抵抗値と抵抗R4の抵抗値とが等しく、コンデンサC3の容量値とコンデンサC4の容量値とが等しく、抵抗R3の抵抗値と抵抗R5の抵抗値とが等しく設定されている。

(もっと読む)

フィルタ装置

【課題】少ない電力でフィルタリング処理を行うことのできるフィルタ装置を提供する。

【解決手段】スイッチ制御部13は、動作フェーズにおいて、クロック制御信号φ1をクロック制御信号φの8クロックのうち1クロック、つまり1/8の時間だけ電力供給スイッチ17を電気的接続状態にする。次に、スイッチ制御部13は、クロック制御信号φ2をクロック制御信号φの8クロックのうち1/2クロック、つまり1/16の時間だけ信号入力スイッチ12を電気的接続状態にする。これ以外の時間を休止フェーズとして電気的接続状態が間欠的になるように各スイッチを切り換え制御することによって、フィルタリング処理で消費する電力を抑えることができる。

(もっと読む)

電圧制御発振回路

【課題】電圧制御発振回路の回路規模の増大を抑制する。

【解決手段】電圧制御発振回路は、発振信号を増幅する発振アンプ部32と、発振信号の発振周波数を制御するLC共振部33と、負性抵抗成分を有する負性抵抗部34と、を備える。LC共振部33は、ループ状に接続されたgmセル25,26と、ループ上のノードに一端が接続された容量28〜31と、を有し、gmセル25,26と容量28,29とに基づくインダクタンス値と、容量30,31の容量値と、に基づいて発振周波数を制御する。

(もっと読む)

フィルタ自動調整回路及び方法並びに無線通信装置

【課題】調整機能を有する複数のフィルタにおいて、高い調整精度を有し、かつ低消費電流化が容易なフィルタのバラツキ調整を可能にする。

【解決手段】位相差検出器104により、複数のモードの切り替えを有する基準フィルタ103における前後の位相差をカウンタ105にてカウントし、基準フィルタ103のバラツキを検出する。その際、主フィルタ109を調整する時には基準フィルタ103を第1のモードに設定し、主フィルタ111を調整する時には基準フィルタ103を第2のモードに設定することで、複数の主フィルタ109,111に対して、より精度の高いフィルタ調整を行う。検出結果から得られる主フィルタ109の調整結果はレジスタ108に、主フィルタ111の調整結果はレジスタ110に保持し、調整後はフィルタ調整に関する部材をすべて動作停止し、低消費電力化を図る。

(もっと読む)

フィルタ回路

【課題】高速に動作することが可能であり、周波数特性制御するためのフィルタ制御信号生成回路が小規模でしかも設計に要する時間が短時間で済むようなフィルタ回路を提供する。

【解決手段】Gm−Cフィルタのフィルタ制御信号生成回路を、MOSトランジスタ32、MOSトランジスタ32とゲート同士が接続されるMOSトランジスタ33、MOSトランジスタ32とドレイン同士が接続されるMOSトランジスタ30、ドレインとゲートが接続され、MOSトランジスタ30とゲート同士が接続され、MOSトランジスタ33とドレイン同士が接続されるMOSトランジスタ31、MOSトランジスタ30〜33のうちの1つのソースに接続される抵抗素子34によって構成し、MOSトランジスタ33,30のドレインに接続される出力端子35または出力端子36からフィルタ制御信号を出力させる。

(もっと読む)

ローパスフィルタ設計

高い品質係数(Q)を有するローパスフィルタリングのための手法。 例示的な実施形態では、入力電流は第1のトランジスタのドレインに接続される。 1のトランジスタのドレインとゲートとは抵抗器R1によって一緒に結合され、そして、ドレインは第1キャパシタC1によって基準電圧に結合される。ゲートは第2のキャパシタC2により、基準圧に結合される。ゲートはさらに第2のトランジスタのゲートに結合され、出力電流が第2のトランジスタのドレインに接続される。別の例示的な実施形態では、さらに受動素子が奇数次のローパス伝達特性を発生するために結合されることができる。 複数のフィルタは、任意のオーダーを有するフィルタを合成するために、直列にカスケード接続することができる。  (もっと読む)

(もっと読む)

時定数回路、スイッチ回路、DC/DCコンバータ及び表示装置

【課題】単調に減衰するだけの出力電圧特性に比べて、急峻に減衰した後に緩やかに減衰する出力電圧特性が得られる時定数回路等を提供する。

【解決手段】時定数回路10は、抵抗素子111と容量素子121との並列回路131,…が第一の端子14と第二の端子15との間に複数直列に接続されて成る直並列回路16と、第二の端子15に接続された第三の端子17と第四の端子18との間に接続された分圧用抵抗素子19と、を備えている。並列回路131は抵抗素子111と容量素子121とから成り、並列回路132は抵抗素子112と容量素子122とから成り、・・・、並列回路13nは抵抗素子11nと容量素子12nとから成る。nは、並列回路131〜13nの数であり、2以上の整数である。

(もっと読む)

イコライザ回路及び受信装置

【課題】回路を構成する素子の特性バラツキの影響を受けることなく、信号伝送で減衰した成分が補償された良好な信号が得られるイコライザ回路を提供する。

【解決手段】入力される電圧信号をトランスコンダクタンスにより電流に変換して、その出力に応じて各容量負荷の充放電を行い、容量負荷毎に期間を異ならせて、電圧信号に応じた電流による容量負荷からの電荷の引き抜きと電圧信号に応じた電流による容量負荷への電荷の注入とを行うようにして、デジタルフィルタにおけるハイパスフィルタの機能を実現し、素子の特性バラツキの影響を受けることなくイコライズ機能を実現できるようにする。

(もっと読む)

21 - 40 / 279

[ Back to top ]