Fターム[5J098AB01]の内容

能動素子を用いた回路網 (5,588) | 回路要素 (1,356) | 増幅器 (406)

Fターム[5J098AB01]の下位に属するFターム

Fターム[5J098AB01]に分類される特許

1 - 20 / 91

信号等化器

スプリッタ回路およびチューナーシステム

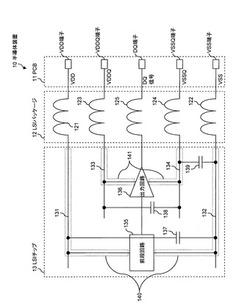

半導体装置

【課題】異なる配線を介して異なる電源端子から内部回路を構成する第1の回路および第2の回路にそれぞれ給電する際に、第1の回路に給電する配線と第2の回路に給電する配線との間に発生するノイズを抑制する。

【解決手段】半導体装置は、第1の回路に給電を行う第1の電源配線と、第2の回路に給電を行う第2の電源配線と、第1の電源配線と第2の電源配線との間に容量素子を設けることにより、両端子間のインピーダンスを、大幅に低減させることにより異種電源間のノイズを低減する。

(もっと読む)

無線通信装置、マッチング制御回路、マッチング制御方法

【課題】RSSI(受信信号強度)を用いたパワーマッチングではノイズが反映されておらず最適な受信感度を実現することができなかった。

【解決手段】本発明の無線通信装置は、アンテナで受信した受信信号に対してインピーダンスマッチングを行うマッチング手段と、前記インピーダンスマッチングが行われた受信信号のノイズが反映された品質指標を算出する品質指標算出手段と、前記ノイズが反映された品質指標に基づいて前記マッチング手段が行うインピーダンスマッチングのマッチング定数を制御する制御手段と、を具備する。当該構成によれば、ノイズを考慮した上でのマッチング制御を行うことができるため、受信感度の最良化を図ることができる。

(もっと読む)

フィルタ装置およびその制御方法

【課題】フィルタのノッチ周波数を調整する機能を持ったフィルタ装置を提供する。

【解決手段】フィルタ動作するときには、バッファ201を介して入力される入力信号Vinと、移相器204及び可変ゲインアンプ205を通った入力信号Vinとを減算器202で減算した結果を出力信号Voutとする。フィルタ調整時には、切り替えスイッチ203および206の接続先を切り替え、バッファ201、移相器204、可変ゲインアンプ205、バッファ201からなる正帰還ループを形成する。この正帰還ループ上の信号をフィードバック信号Vfとし、フィルタコア部102を発振状態にした状態で、前記フィードバック信号Vfの振幅及び周波数が基準振幅及び基準周波数となるように可変ゲインアンプ205のゲイン及び移相器204の位相のシフト量を制御する。調整終了後、切り替えスイッチ203および206を切り替え、ノッチフィルタとして動作させる。

(もっと読む)

直交信号生成回路、直交信号生成回路の調整方法、及び無線通信装置

【課題】高周波の広い範囲で周波数が高速で切り替わり、正確に位相が90度異なる直交信号を消費電力が少ない回路で生成する。

【解決手段】可変利得アンプ9によって増幅した信号を、ポリフェイズフィルタ1を通すことで、大まかに位相差が90度となる直交信号を生成する。ディジタル制御回路8からのディジタル信号で制御された可変利得アンプ2,3により、直交信号を増幅する。可変利得アンプ2,3の出力信号の振幅を振幅検出器4,5によって検出し、可変利得アンプ2,3の出力信号の振幅が等しくなるように、可変利得アンプの利得をディジタル制御回路8によって疎調整する。この疎調整に加えて、後述する微調整を行うことで、可変利得アンプ2,3の出力信号の振幅を等しくする。

(もっと読む)

バランス/アンバランス信号出力回路

【課題】簡易な構成で無駄なくバランス出力とアンバランス出力とを選択的に切り替えて出力する。

【解決手段】バランス/アンバランス信号出力回路は、バランス出力の場合、D/Aコンバータ10,12でそれぞれアナログ正相信号、アナログ逆相信号を生成し、切替スイッチ20,22でバランスHOT端子及びバランスCOLD端子から出力する。アンバランス出力の場合、D/Aコンバータ10,12でそれぞれアナログ正相信号を生成し、切替スイッチ24,26でアンバランス端子から出力する。

(もっと読む)

半導体装置

【課題】省面積化されたローパスフィルタを備える半導体装置を提供する。

【解決手段】第1のノードと第2のノードとの間に接続され、印加される電圧に応じて内部容量が変化する可変容量素子と、第1のノードと第2のノードとの間に可変容量素子と並列に接続される電圧増幅部とを備え、電圧増幅部は、第1のノードと電気的に接続される増幅器と、増幅器の出力の電圧をシフトさせるレベルシフト回路とを含み、レベルシフト回路の出力は第2のノードと電気的に接続される。

(もっと読む)

オーディオ機器

【課題】入力端子に接続されたソース機器に合わせて入力インピーダンスやゲインを設定可能なオーディオ機器を提供する。

【解決手段】ホット端子およびコールド端子を有しソース機器が接続される入力端子と、インピーダンス素子と、キャパシタと、テスト信号発生部と、リターン信号解析部と、通常動作時にインピーダンス素子を入力端子に並列に接続し、ソース機器のインピーダンス検出時にコールド端子にテスト信号発生部を接続するとともにホット端子にキャパシタおよびリターン信号解説部を接続する切替スイッチとを備え、ソース機器のインピーダンス検出時に、テスト信号発生部はテスト信号を発生し、リターン信号解析部はホット端子に戻ってきたテスト信号であるリターン信号に基づいてソース機器のインピーダンスを検出する。

(もっと読む)

オーディオ用GIC回路

【課題】オーディオ用アクティブ型フィルター、特にGICフィルターにおいて遮断周波数以降で発生する特性劣化(遮断特性の跳ね返り)を2次LCフィルターの追加により補償する事、およびGICフィルターのピーキング特性を維持しながらGIC遮断限界以上で所定の遮断特性を実現する事。

【解決手段】2次LCフィルターの終端抵抗としてFDNR(Frequency Dependent Negative Resistors)を用いる事、およびLCフィルターと直列に制動抵抗(1)を接続する事で共振特性を備えた2次LCフィルターを実現しGIC遮断限界以上で所定の遮断特性を実現する。

(もっと読む)

インピーダンス整合回路、インピーダンス整合方法及び双方向伝送回路

【課題】オープンドレイン出力バッファ間で双方向の伝送を行う際のインピーダンスを整合させて、誤動作することなく高速通信すること。

【解決手段】インピーダンス整合回路は、第1の端子にオープンドレイン出力バッファ、第2の端子に双方向伝送線路が接続され、オープンドレイン出力バッファからの第1の出力信号及び双方向伝送線路からの第2の出力信号を検出する検出回路と、第1の出力信号の電圧の変化が第1の方向であると検出された場合、当該第1の出力信号に負荷抵抗を接続して双方向伝送線路へ出力し、第1の出力信号の電圧の変化が第1の方向とは逆の第2の方向であると検出された場合、当該第1の出力信号にダンピング抵抗を接続して双方向伝送線路へ出力し、第2の出力信号の電圧の変化が検出された場合、当該第2の出力信号に負荷抵抗及びダンピング抵抗のいずれも接続せずにオープンドレイン出力バッファへ出力する抵抗接続回路とを有する。

(もっと読む)

デカップリング回路及び半導体集積回路

【課題】容量値の切り換えが可能なデカップリング回路を提供すること。

【解決手段】本発明は、インバータ21を有する。インバータ21は、ゲート電極G1を有するi(iは1以上の整数)個のPMOSトランジスタ及びゲート電極G2を有するj(jは0以上の整数)個のPMOSトランジスタを有する。また、インバータ21は、ゲート電極G3を有するm(mは1以上の整数)個のNMOSトランジスタ及びゲート電極G2を有するn(nは0以上の整数)個のNMOSトランジスタを有する。ゲート電極G1〜G4は、インバータ21の入力端と接続される。ゲート電極G1及びG2の合計面積は、ゲート電極G3及びG4の合計面積と異なる。

(もっと読む)

フィルタ

【課題】従来に比して格段的に特性のばらつきを小さくすることができるフィルタを提供する。

【解決手段】入力信号Vinの周波数特性を補正して出力するフィルタ部22と、フィルタ部22の特性を制御する制御部23とを備えるようにする。フィルタ部22は、制御電流ICNTにより相互コンダクタンスを可変して入力電圧に応じた電流を出力するトランスコンダクタンス回路24を使用したジャイレータ方式のフィルタ回路であり、制御部23は、制御用のクロック信号CLKを周波数電流変換して制御電流ICNTを生成する。

(もっと読む)

フィルタ回路

【課題】フィルタ回路の中心周波数を調整する機能を備えたフィルタ回路を提供する。

【解決手段】入力信号とフィードバック信号(信号Vf)の加算信号を出力するカプラー109、加算信号を増幅した増幅信号を生成するAGC回路110、増幅信号の位相をシフトさせて信号Vfを生成する移相器111を備えたフィルタコア部102と、基準信号(信号Vr)を取得する基準信号生成部119、信号Vr、信号Vfの振幅を比較する振幅比較回路101、比較の結果に基づいてAGC回路110の増幅率を制御するゲイン制御電圧生成部108、信号Vrの位相と信号Vfの位相とを比較する移相比較回路103、比較結果に基づいて移相器111の位相のシフト量を制御する移相器制御電圧生成部117によってフィルタ回路を構成し、増幅率、シフト量が制御される間、カプラー109には信号Vfに代えて基準信号が入力される。

(もっと読む)

可変減衰器

【課題】 従来の可変減衰器では、高周波信号を損失少なく通過させる基準状態と、所望の減衰量を得る減衰状態との間で、通過位相差を生じてしまうという課題があった。

【解決手段】 入出力間FET3と並列、定位相可変減衰器4と直列に位相補正用FET5を設置することで、入出力間FET3がオン状態のときは位相補正用FET5をオフ状態とし、入出力間FET3がオフ状態のときは位相補正用FET5をオン状態とすることによって、基準状態と減衰状態との間で通過位相を等しくすることができる。

(もっと読む)

信号生成装置

【課題】位相に不連続を生じさせずに信号を生成する。

【解決手段】処理部6は、一の通過帯域の周波数の第1信号S1を第1DDS32で生成し、フィルタ35を介して出力信号Soとして出力させている状態において、出力信号Soの周波数を一の通過帯域に隣接する他の通過帯域(フィルタ36の通過帯域)の他の周波数に変更する際に、第1切替部34に対する切替制御を実行して第2DDS33をフィルタ36に接続すると共に、周波数設定制御を実行することによって各DDS32,33から出力される各信号S1,S2の周波数を一の通過帯域と他の通過帯域との重複する帯域の共通周波数に設定し、次いで、第2DDS33に対する位相設定制御を実行して第2信号S2の位相をフィルタ35から出力されている第1信号S1の位相に一致させた後に、第2切替部39に対する切替制御を実行して、出力信号Soを第1信号S1から第2信号S2に切り替える 。

(もっと読む)

フィルタ回路

【課題】フィルタ回路における信号のロスが生じても、通過すべき周波数の信号と他の周波数の信号との十分な強度比が得られるフィルタ回路を提供する。

【解決手段】信号線110に接続され、信号線110を伝搬する信号をフィルタリングするフィルタ回路を、信号線110ラインから信号を入力し、バッファリングするアンプ回路101と、アンプ回路101によってバッファリングされた信号をフィルタリングするノッチフィルタ108と、ノッチフィルタ108から出力された信号を入力し、入力された信号の周波数分布を反転させて信号線110に出力する−gm回路102と、によって構成する。

(もっと読む)

イコライザ回路及び受信装置

【課題】回路を構成する素子の特性バラツキの影響を受けることなく、信号伝送で減衰した成分が補償された良好な信号が得られるイコライザ回路を提供する。

【解決手段】入力される電圧信号をトランスコンダクタンスにより電流に変換して、その出力に応じて各容量負荷の充放電を行い、容量負荷毎に期間を異ならせて、電圧信号に応じた電流による容量負荷からの電荷の引き抜きと電圧信号に応じた電流による容量負荷への電荷の注入とを行うようにして、デジタルフィルタにおけるハイパスフィルタの機能を実現し、素子の特性バラツキの影響を受けることなくイコライズ機能を実現できるようにする。

(もっと読む)

アクティブポリフェーズフィルタ

【課題】大電力を入力しても歪の小さいアクティブポリフェーズフィルタを提供する。

【解決手段】npnトランジスタQ1、Q2、Q4及びQ5と、npnトランジスタQ6、Q7、Q4及びQ5は、各々トランスリニアループを形成している。また、npnトランジスタQ2及びQ3と、npnトランジスタQ7及びQ8は各々カレントミラー回路を形成している。こうして、npnトランジスタQ1とQ3の各々のコレクタ電流の差と、npnトランジスタQ6とQ8の各々のコレクタ電流の差とが、いずれも、平衡な高周波入力の電流に等しくなる。このような2組の差動入力を、ポリフェーズフィルタ部10の4入力とすることで、ポリフェーズフィルタ部10の4出力から、偶数次成分の抑制された、位相がπ/2異なる差動出力を得ることができる。

(もっと読む)

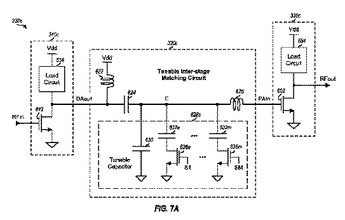

デジタルのチューナブル段間整合回路

性能を改善できるチューナブル段間整合回路について説明する。例示的な設計では、装置は、第1の能動回路(たとえば、ドライバ増幅器)と、第2の能動回路(たとえば、電力増幅器)と、第1の能動回路と第2の能動回路の間に接続されたチューナブル段間整合回路とを含む。このチューナブル段間整合回路は、第1の能動回路と第2の能動回路の間のインピーダンス整合を調整するために個別のステップで変化できるチューナブルキャパシタを含む。例示的な設計では、このチューナブルキャパシタは、(i)並列に接続された複数のキャパシタと、(ii)この複数のキャパシタに対してキャパシタごとに1つ接続された複数のスイッチとを含む。各スイッチは、関連するキャパシタを選択するためにオンにされるか、または関連するキャパシタの選択を解除するためにオフにされることができる。チューナブルキャパシタは、複数のキャパシタと並列に接続された固定キャパシタをさらに含むことができる。  (もっと読む)

(もっと読む)

1 - 20 / 91

[ Back to top ]