Fターム[5J098AB31]の内容

能動素子を用いた回路網 (5,588) | 回路要素 (1,356) | フィルタ (143)

Fターム[5J098AB31]に分類される特許

1 - 20 / 143

制御回路および位相変調器

フィルタ回路及び受信装置

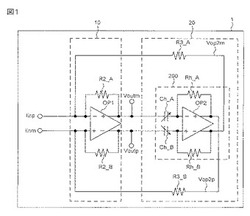

【課題】低雑音かつ低カットオフ周波数のフィルタ回路をより小面積で実現する。

【解決手段】フィルタ回路(1〜5)は、入力端子(Iinp、Iinm、(Vinp、Vinm))に供給された入力信号を受け、信号を増幅して出力端子(Voutm、Voutp)に出力する第1回路(10、11)と、第1容量素子(Ch_A、Ch_B)を介して前記第1回路の出力信号を入力する第1差動増幅回路(OP2)と、前記第1差動増幅回路(OP2)の入出力間に負帰還経路を形成する第1抵抗素子(Rh_A、Ch_B)と、前記第1差動増幅回路の出力と前記第1回路の入力との間に負帰還経路を形成する第2抵抗素子(R3_A、R3_B)とを有する。

(もっと読む)

ポジショナ

【課題】低周波のノイズの影響に強いポジショナを提供する。

【解決手段】入力ラインL1と出力ラインL2との間に能動負荷Zとして可変インピーダンス回路ZBを設ける。可変インピーダンス回路ZBは、直流の電流信号に対するインピーダンスが低く、交流の電流信号に対するインピーダンスが高いという特性を有し、ラインL1,L2間に接続された抵抗R1とR2とR3との直列回路と、ラインL1にそのコレクタが接続され、そのベースが抵抗R2とR3との接続点に接続されたトランジスタQ1と、トランジスタQ1のエミッタとラインL2との間に接続された抵抗R4と、抵抗R2とR3との接続点にその一端が接続されたコンデンサC1と、コンデンサC1の他端とラインL2との間に接続された抵抗R5と、抵抗R1とR2との接続点にその一端が接続されたコンデンサC2と、コンデンサC2の他端とラインL2との間に接続された抵抗R2とから構成されている。

(もっと読む)

無線通信装置、マッチング制御回路、マッチング制御方法

【課題】RSSI(受信信号強度)を用いたパワーマッチングではノイズが反映されておらず最適な受信感度を実現することができなかった。

【解決手段】本発明の無線通信装置は、アンテナで受信した受信信号に対してインピーダンスマッチングを行うマッチング手段と、前記インピーダンスマッチングが行われた受信信号のノイズが反映された品質指標を算出する品質指標算出手段と、前記ノイズが反映された品質指標に基づいて前記マッチング手段が行うインピーダンスマッチングのマッチング定数を制御する制御手段と、を具備する。当該構成によれば、ノイズを考慮した上でのマッチング制御を行うことができるため、受信感度の最良化を図ることができる。

(もっと読む)

フィルタ装置およびその制御方法

【課題】フィルタのノッチ周波数を調整する機能を持ったフィルタ装置を提供する。

【解決手段】入力信号を抵抗109と可変容量110、アクティブインダクタ111を備えたフィルタコア部102にて分圧し、フィルタコア部102のフィルタ特性信号Vfの振幅と基準振幅とを比較する振幅比較回路101、振幅比較回路101での比較結果に基づいてアクティブインダクタ111の位相を制御する位相制御部108、フィルタコア部102のフィルタ特性信号Vfの周波数と基準周波数とを比較する周波数比較回路103、周波数比較回路103の比較結果に基づいて可変容量110の容量を制御する可変容量制御部117によってフィルタ装置を構成し、アクティブインダクタ111の位相、可変容量11の容量が制御される間、アクティブインダクタ111の位相制御部108が、フィルタコア部102を発振させる。

(もっと読む)

インピーダンス整合フィルタ、および、実装基板

【課題】従来のフィルタ部品では、高速IF信号を扱うにもかかわらず、基板配線を行う場合において、インピーダンス整合を十分に確保しにくい問題がある。例えば、フィルタ部品を用いて理想的なインピーダンス整合で基板配線したものとしてSIM上では扱うが、実際に、基板配線を行った場合には、フィルタ部品の構成上、インピーダンス不整合が発生してしまい、ずれが生じてしまう。

【解決手段】入力端子と出力端子を備えたフィルタ部品に、実装基板上で容易にインピーダンス整合を実施可能とするためにGND接続部を備えたインピーダンス整合フィルタと、前記インピーダンス整合フィルタを搭載した実装基板とする。

(もっと読む)

オーディオ機器

【課題】入力端子に接続されたソース機器に合わせて入力インピーダンスやゲインを設定可能なオーディオ機器を提供する。

【解決手段】ホット端子およびコールド端子を有しソース機器が接続される入力端子と、インピーダンス素子と、キャパシタと、テスト信号発生部と、リターン信号解析部と、通常動作時にインピーダンス素子を入力端子に並列に接続し、ソース機器のインピーダンス検出時にコールド端子にテスト信号発生部を接続するとともにホット端子にキャパシタおよびリターン信号解説部を接続する切替スイッチとを備え、ソース機器のインピーダンス検出時に、テスト信号発生部はテスト信号を発生し、リターン信号解析部はホット端子に戻ってきたテスト信号であるリターン信号に基づいてソース機器のインピーダンスを検出する。

(もっと読む)

トランスコンダクタンス調整回路、回路装置及び電子機器

【課題】トランスコンダクタンスを精度良く調整することができるトランスコンダクタンス調整回路、回路装置及び電子機器等を提供すること。

【解決手段】トランスコンダクタンス調整回路100は、第1の信号I及び第1の信号Iと位相が90度異なる第2の信号Qが入力され、第1、第2の抵抗素子RA1と、第1、第2のキャパシターCA1、CA2と、演算トランスコンダクタンス増幅器で構成される中心周波数シフト回路110と、トランスコンダクタンス調整信号AGMを出力する調整信号生成回路120とを含む。調整信号生成回路120は、第2の信号Qと第1の出力信号OIとに基づいて、又は第1の信号Iと第2の出力信号OQとに基づいて、又は第1の信号Iと第1の出力信号OIとに基づいて、又は第2の信号Qと第2の出力信号OQとに基づいて、トランスコンダクタンス調整信号AGMを生成する。

(もっと読む)

オーディオ用GIC回路

【課題】オーディオ用アクティブ型フィルター、特にGICフィルターにおいて遮断周波数以降で発生する特性劣化(遮断特性の跳ね返り)を2次LCフィルターの追加により補償する事、およびGICフィルターのピーキング特性を維持しながらGIC遮断限界以上で所定の遮断特性を実現する事。

【解決手段】2次LCフィルターの終端抵抗としてFDNR(Frequency Dependent Negative Resistors)を用いる事、およびLCフィルターと直列に制動抵抗(1)を接続する事で共振特性を備えた2次LCフィルターを実現しGIC遮断限界以上で所定の遮断特性を実現する。

(もっと読む)

バンドパスフィルタ及びバンドパスフィルタのキャリブレーション方法

【課題】BPFを構成するOTAの個数を削減し,低消費電力で高次のバンドパスフィルタを提供する。

【解決手段】バンドパスフィルタは,入力信号が入力されるハイパスフィルタ(14)と,ハイパスフィルタの出力が反転入力端子に入力され,反転入力端子と非反転入力端子間の入力電圧を増幅して出力信号を出力端子に出力するアンプ(10)と,アンプの非反転出力端子と反転入力端子との間に接続された第1抵抗(R2)と,反転入力端子に第1端子が接続された第1キャパシタ(C2)と,アンプの非反転出力端子の出力信号の極性を反転し,当該反転した信号をキャパシタの第2端子に出力する反転アンプ(12)とを有する。

(もっと読む)

半導体集積回路およびその動作方法

【課題】DCオフセットキャンセル動作の動作期間を短縮する。

【解決手段】フィルタ処理と増幅機能を有するアクティブローフィルタ300の差動出力端子に2個の校正抵抗R22の一方の端子が接続され、2個の校正抵抗R22の他方の端子に電圧比較器CMPの2個の入力端子と切り換えスイッチSWIOの2個の端子が接続される。DCオフセット電圧低減のデジタル制御信号DACS、DAC2…DAC0を算出する算出期間で、デジタルアナログ変換器DAC0のアナログ電流による一方の校正抵抗R22の電圧降下に依存する校正電圧を電圧比較器CMPが検出する。DCオフセット電圧を低減する校正期間では、デジタル制御信号に応答したデジタルアナログ変換器の校正アナログ電流が切り換えスイッチSWIOを介してフィルタ300の入力側に流される。

(もっと読む)

フィルタ装置および通過帯域特性調整方法

【課題】従来よりも少ない回路規模で、半導体で構成される受動素子により形成される通過帯域特性の調整機能を実現できるフィルタ装置および通過帯域特性調整方法を得ること。

【解決手段】通信装置の受信系で用いられるフィルタ装置8であって、半導体で構成される受動素子の組み合わせにより、入力される受信信号に対し通過帯域の制限を行うフィルタ回路4と、毎回の受信動作開始時に、当該受信系において前記フィルタ回路の後段に設けられている信号強度検出回路が検出した信号強度を利用して、前記フィルタ回路の周波数通過特性を、前記入力される受信信号を最大に出力できるように調整する制御回路9とを備えた。

(もっと読む)

位相調整回路、検出装置及び電子機器

【課題】信号の位相を高精度に調整可能な位相調整回路、検出装置及び電子機器等を提供すること。

【解決手段】位相調整回路は、位相主調整用のローパスフィルター210と、位相微調整用のハイパスフィルター230を含む。ローパスフィルター210は、周波数finの第1の信号が入力され、その周波数finにおける位相遅れ角度がX度(X≧0)となる周波数特性を有する。ハイパスフィルター230は、ローパスフィルター210からの出力信号LQに基づく第2の信号GQが入力され、周波数finにおける位相進み角度がY度(Y≧0)となる周波数特性を有する。Y度はX度よりも小さい値に設定される。

(もっと読む)

積分回路および電圧検出装置

【課題】カットオフ周波数が入力抵抗と帰還コンデンサとで規定される目標とする積分特性を確保しつつ、積分信号の振動を防止する。

【解決手段】非反転入力端子がグランド電位Vgに規定された演算増幅器34aと、演算増幅器34aの反転入力端子に接続された入力抵抗34bと、演算増幅器34aの反転入力端子に一端が接続されると共に演算増幅器34aの出力端子に他端が接続された帰還コンデンサ34cと、演算増幅器34aの反転入力端子に一端が接続されると共に演算増幅器34aの出力端子に他端が接続され、かつ接続点Bが交流的にグランド電位Vgに短絡可能に構成された帰還抵抗34d,34eとを備え、接続点Bとグランド電位Vgとの間に接続されて、接続点Bのグランド電位Vgへの交流的な短絡をオン・オフさせる短絡用スイッチ34gを備えている。

(もっと読む)

ロードスイッチ

【課題】小さい入力−出力差分電圧を維持し、既定の応答を提供する半導体装置、回路、そしてAC及びDCロードスイッチを提供する。

【解決手段】ロードスイッチは、入力端子及び出力端子へ結合された通過素子を含み得る。通過素子は制御端子を含み、制御端子は通過素子の応答を制御し得る。ロードスイッチは第1のループを含み得る。第1のループは制御端子へ結合され、通過素子との高インピーダンスを維持しながら入力端子及び出力端子間の電圧降下を制御するように構成される。ロードスイッチは第2のループを含み得る。第2のループは制御端子へ結合され、既定のフィルタ応答を入力端子から提供するように構成される。既定の応答は、低域通過応答、高域通過応答、又は帯域通過応答であり得る。応答の通過帯域及び/又は阻止帯域は、プログラムされ得る。

(もっと読む)

フィルタ較正

【課題】費用対効果が大きく、簡単であり、さらに正確な、フィルタを較正する方法を提供する。

【解決手段】フィルタ104、116は、較正中に発振器として再構成される。フィルタを再構成するために、スイッチおよび/または他の構成が使用されて、フィルタの負のフィードバックループに対して正のフィードバックループを再構成する。フィルタのコンポーネントを調整して、所望のフィルタ特性に対応する発振を達成するために発振パラメータが次に測定される。

(もっと読む)

半導体装置

【課題】半導体装置は、必要に応じてダイナミックレンジを確保し、且つ低消費電流化に資するフィルタ回路を備える。

【解決手段】半導体装置は、トランスコンダクタンス増幅器(103a〜103d、203a〜203d)とキャパシタ(104a、104b)から構成されるフィルタ回路(10、20)を有し、前記フィルタ回路は、妨害信号の電界強度を検出し、検出結果に基づいて、前記トランスコンダクタンス増幅器の差動入力段トランジスタのソース側のインピーダンスと前記トランスコンダクタンス増幅器のバイアス電流の双方を調整するための制御を行う。

(もっと読む)

デカップリング回路及び半導体集積回路

【課題】容量値の切り換えが可能なデカップリング回路を提供すること。

【解決手段】本発明は、インバータ21を有する。インバータ21は、ゲート電極G1を有するi(iは1以上の整数)個のPMOSトランジスタ及びゲート電極G2を有するj(jは0以上の整数)個のPMOSトランジスタを有する。また、インバータ21は、ゲート電極G3を有するm(mは1以上の整数)個のNMOSトランジスタ及びゲート電極G2を有するn(nは0以上の整数)個のNMOSトランジスタを有する。ゲート電極G1〜G4は、インバータ21の入力端と接続される。ゲート電極G1及びG2の合計面積は、ゲート電極G3及びG4の合計面積と異なる。

(もっと読む)

再帰型フィルタ回路

【課題】再帰フィルタ回路のエミッタフォロア回路の数を低減し、回路規模が小さい再帰型フィルタ回路を提供する。

【解決手段】バイポーラトランジスタ(Tr)101を流れる電流Iinとフィードバック電流Ifbとを加算して電流Iを生成するノードB、電流Iをテール電流とし、ゲインを変更する制御信号が入力されるバイポーラTr106及びバイポーラTr103を含む差動対100、バイポーラTr106に流れる電流を電圧に変換する抵抗素子105を含む可変ゲイン増幅部、変換後の電圧を増幅して出力信号を生成するバイポーラTr113を含む出力部115、可変容量素子104を含むハイパス部、ハイパス部から出力された信号をバッファリングする回路114、バッファリングされた信号を、可変容量素子109を介して周波数帯域制限するローパス部を含む移相部によって再帰型フィルタを構成する。

(もっと読む)

フィルタ回路

【課題】フィルタ回路の中心周波数を調整する機能を備えたフィルタ回路を提供する。

【解決手段】入力信号とフィードバック信号(信号Vf)の加算信号を出力するカプラー109、加算信号を増幅した増幅信号を生成するAGC回路110、増幅信号の位相をシフトさせて信号Vfを生成する移相器111を備えたフィルタコア部102と、基準信号(信号Vr)を取得する基準信号生成部119、信号Vr、信号Vfの振幅を比較する振幅比較回路101、比較の結果に基づいてAGC回路110の増幅率を制御するゲイン制御電圧生成部108、信号Vrの位相と信号Vfの位相とを比較する移相比較回路103、比較結果に基づいて移相器111の位相のシフト量を制御する移相器制御電圧生成部117によってフィルタ回路を構成し、増幅率、シフト量が制御される間、カプラー109には信号Vfに代えて基準信号が入力される。

(もっと読む)

1 - 20 / 143

[ Back to top ]