Fターム[5J098GA08]の内容

能動素子を用いた回路網 (5,588) | インピーダンスの変換と擬似回路の機能と構成 (102) | 1端子対回路 (30)

Fターム[5J098GA08]に分類される特許

1 - 20 / 30

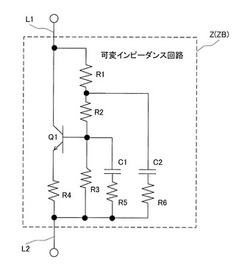

ポジショナ

【課題】低周波のノイズの影響に強いポジショナを提供する。

【解決手段】入力ラインL1と出力ラインL2との間に能動負荷Zとして可変インピーダンス回路ZBを設ける。可変インピーダンス回路ZBは、直流の電流信号に対するインピーダンスが低く、交流の電流信号に対するインピーダンスが高いという特性を有し、ラインL1,L2間に接続された抵抗R1とR2とR3との直列回路と、ラインL1にそのコレクタが接続され、そのベースが抵抗R2とR3との接続点に接続されたトランジスタQ1と、トランジスタQ1のエミッタとラインL2との間に接続された抵抗R4と、抵抗R2とR3との接続点にその一端が接続されたコンデンサC1と、コンデンサC1の他端とラインL2との間に接続された抵抗R5と、抵抗R1とR2との接続点にその一端が接続されたコンデンサC2と、コンデンサC2の他端とラインL2との間に接続された抵抗R2とから構成されている。

(もっと読む)

アクティブインダクタ

【課題】アクティブインダクタを提供する。

【解決手段】ソース、ドレイン、及びゲートを含むpMOSトランジスタであって、前記pMOSトランジスタの前記ソースが電源Vddと接続し、抵抗Rの一端が前記pMOSトランジスタの前記ゲートに接続し、前記抵抗Rの他端が前記pMOSトランジスタの前記ドレインに接続している回路において、電源からの直流バイアスの略フルレンジに対して、インダクテイブインピーダンスを生成し、インダクタの特性を有する。

(もっと読む)

デカップリング回路及び半導体集積回路

【課題】容量値の切り換えが可能なデカップリング回路を提供すること。

【解決手段】本発明は、インバータ21を有する。インバータ21は、ゲート電極G1を有するi(iは1以上の整数)個のPMOSトランジスタ及びゲート電極G2を有するj(jは0以上の整数)個のPMOSトランジスタを有する。また、インバータ21は、ゲート電極G3を有するm(mは1以上の整数)個のNMOSトランジスタ及びゲート電極G2を有するn(nは0以上の整数)個のNMOSトランジスタを有する。ゲート電極G1〜G4は、インバータ21の入力端と接続される。ゲート電極G1及びG2の合計面積は、ゲート電極G3及びG4の合計面積と異なる。

(もっと読む)

通信システム、車載通信装置及び分岐コネクタ

【課題】電力線を介した通信に関し、利得低下の防止及び伝送品質の低下を防止を実現することができる通信システムを提供する。

【解決手段】バッテリ4からの電力を供給するための電力線3がECU1,1,…及びアクチュエータ2,2,…に接続し、ECU1,1,…及びアクチュエータ2,2,…は夫々電力線3から電力の供給を受けると共に、電力線3を介して通信を行なう。ECU1,1,…及びアクチュエータ2,2,…は、電力線3の分岐点31からの分岐に夫々接続される。分岐点31に、負性インピーダンス変換回路5の一端を接続し、他端を固定電位に接続する。

(もっと読む)

電圧制御発振回路

【課題】電圧制御発振回路の回路規模の増大を抑制する。

【解決手段】電圧制御発振回路は、発振信号を増幅する発振アンプ部32と、発振信号の発振周波数を制御するLC共振部33と、負性抵抗成分を有する負性抵抗部34と、を備える。LC共振部33は、ループ状に接続されたgmセル25,26と、ループ上のノードに一端が接続された容量28〜31と、を有し、gmセル25,26と容量28,29とに基づくインダクタンス値と、容量30,31の容量値と、に基づいて発振周波数を制御する。

(もっと読む)

アクティヴインダクタ

【課題】出力電流雑音の変動しない可変型アクティヴインダクタを提供すること。

【解決手段】トランジスタのゲート−ソース間に並列に容量素子とスイッチを直列接続した素子を接続する。すなわち、PMOSトランジスタM2のドレインとキャパシタC1の一方の端子を接続する。また、端子VinとキャパシタC1のもう一方の端子にスイッチS1の一方の端子を直列接続し、スイッチS1のもう1方の端子をPMOSトランジスタM2のゲートと接続する。スイッチS1を開閉する事で見かけ上のトランジスタのゲート−ソース間容量を変化させてインダクタンス値を変動させるが、MOSトランジスタM1・M2の相互コンダクタンスは変化せず、そのため出力電流雑音は変らない。

(もっと読む)

アクティブインダクタおよび差動アンプ回路

【課題】低電源電圧下においても、半導体集積回路上での面積および消費電力の増大を抑えつつ、高域での利得のピーキングの傾きを急峻化する。

【解決手段】P型電界効果トランジスタM1のソースを電源電位VDDに接続し、P型電界効果トランジスタM1のドレインを出力端子outに接続し、N型電界効果トランジスタM2のドレインを電源電位VDDに接続し、N型電界効果トランジスタM2のソースを電流源IBを介して接地電位に接続し、P型電界効果トランジスタM1のゲートをN型電界効果トランジスタM2のソースに接続し、N型電界効果トランジスタM2のゲートを抵抗素子Rpを介してP型電界効果トランジスタM1のドレインに接続する。

(もっと読む)

インピーダンス調整回路

【課題】回路規模を縮減するインピーダンス調整回路の提供。

【解決手段】外付抵抗3と、被調整抵抗5のレプリカをなすレプリカ抵抗4の抵抗値の大小を比較するコンパレータ2と、抵抗制御回路10と、を備え、抵抗制御回路10は、コンパレータ2での比較結果に基づきカウント値をアップ・ダウンしレプリカ抵抗への制御信号を出力するレプリカ抵抗制御カウンタ11と、被調整抵抗5へ与える制御信号を保持する被調整抵抗制御信号保持回路12と、前記カウンタの状態と、前記保持回路の出力を入力し、レプリカ抵抗制御カウンタ11のカウント状態と被調整抵抗制御信号保持回路12の出力(Y)との値の差(|X−Y|)が予め定められた所定範囲内にあるときは、被調整抵抗制御信号保持回路12の出力(Y)を被調整抵抗制御信号保持回路(12)への入力(Z)として供給する監視回路13を備えている。

(もっと読む)

半導体集積回路

【課題】チップ占有面積が小さく低消費電力の広帯域RF信号処理回路を提供すること。

【解決手段】半導体集積回路は、第1制御端子101の第1制御信号Vc1により制御可能なキャパシタンスCRを有する第1キャパシタ1と、第2制御端子102の第2制御信号Vc2により制御可能なキャパシタンスCLを有する第2キャパシタ3を含み等価的にインダクタLをエミュレートするジャイレータ2、5とからなる共振回路を半導体チップに具備する。キャパシタンスCRとインダクタLは、並列共振回路を構成する。並列共振周波数を変更する際に、第1と第2のキャパシタ1、3のキャパシタンスを協調的に変更する。並列共振回路は増幅素子Q1の出力電極に接続されるアクティブ負荷に好適である。

(もっと読む)

アクティブインダクタ回路、発振器、及び、フィルタ回路

【課題】 外部接続用の2端子の各入力インピーダンスが等しく差動回路に適用した場合の波形歪を抑制でき、小面積化、低消費電力化の図れるアクティブインダクタ回路を提供する。

【解決手段】 相互コンダクタンスの極性の異なる第1電圧制御電流源回路5A〜5Dと第2電圧制御電流源回路6A〜6Dの一方の入力と他方の出力、他方の入力と一方の出力

を互いに接続した能動回路1A〜1Dの4つを循環的に接続し、各能動回路の4つの接続点の対向する1対間にキャパシタ4を接続し、他の対向する1対を外部接続用の端子対Nx1,Nx2として構成する。

(もっと読む)

可変インピーダンス回路、それを用いた可変インピーダンスシステム、フィルタ回路、増幅器、通信システム

【課題】可変インピーダンス回路の歪を低減したい。

【解決手段】第1トランジスタM1は、差動入力信号の一方を受ける第1端子と、インピーダンスを変化させるための制御信号を受ける第2端子と、第2トランジスタと接続された第3端子と、基板に電位を供給するための第4端子とを含む。第2トランジスタM2は、差動入力信号の他方を受ける第5端子と、制御信号を受ける第6端子と、第1トランジスタと接続された第7端子と、基板に電位を供給するための第8端子とを含む。第3端子、第4端子、第7端子および第8端子が接続される。

(もっと読む)

キャパシタンス回路

【課題】外部からトランジスタの容量値を調整できる容量調整機能を有し、処理する信号の応答特性を適宜調整可能とし、成形波形の特性を一致させることが可能なキャパシタンス回路を提供する。

【解決手段】トランジスタを用いるキャパシタンス回路において、容量調整信号を受け付ける容量調整端子と、トランジスタのソース端子とドレイン端子とに接続されて、容量調整信号によりトランジスタの容量を調整する容量調整回路と、を具備する。

(もっと読む)

可変容量回路

【課題】可変容量ダイオード2への印加逆制御電圧変化対その容量変化の関係を線形にする補正手段に負性インピーダンス変換回路3を用い、容量変化範囲を狭くせず、複雑な補正手段を用いずに済む可変容量回路を提供する。

【解決手段】非接地側入力端子1aと接地側入力端子1b間に接続され、可制御電圧形成装置6の可変制御電圧が供給される可変容量ダイオード2と、入力端と出力端と接地端を有し、入力端が記非接地側入力端子1aに、出力端が容量素子5を介して接地側入力端子1bに接続された負性インピーダンス変換回路3を備え、容量素子5の容量を非接地側入力端子1aと接地側入力端子1b間に形成される分布容量に略等しい値に選び、可制御電圧形成装置6の調整によって可変制御電圧を線形変化させるに伴い可変容量ダイオード2の容量を対数的に変化させるように形成した。

(もっと読む)

受信機入力回路

【課題】周波数選択回路1と高周波入力段3間に2端子型浮動負性抵抗回路2を接続し、その負性抵抗により周波数選択回路1に形成される抵抗成分を打ち消すことにより受信機入力回路における雑音指数を大幅に低減できる受信機入力回路を提供する。

【解決手段】受信した高周波信号を選択する周波数選択回路1と、周波数選択回路1で選択した高周波信号を供給する高周波入力段3とを備える受信機入力回路において、周波数選択回路1と高周波入力段3間に2端子型浮動負性抵抗回路2を接続し、2端子型浮動負性抵抗回路2の負性抵抗により周波数選択回路1に形成される抵抗成分を打ち消すようにした。

(もっと読む)

浮動アクティブインダクタ

【課題】回路構成を複雑にすることなしに、そのインダクタンス値及びその内部抵抗値を個別に設定することが可能な浮動アクティブインダクタを提供する。

【解決手段】第1及び第2入力端子1、2間に直列接続された浮動インダクタ回路A及び浮動負性抵抗回路Bと、それらの回路A、Bの直列接続点3を備え、第1及び第2入力端子1、2間に浮動アクティブインダクタが形成されるもので、浮動インダクタ回路Aは、第1入力端子1と直列接続点3間に直列接続された第1キャパシタ4、第1抵抗5、第2キャパシタ6と、第1キャパシタ4の両端に第1低抵抗8を介して接続された第1電圧フォロワ8と、第2キャパシタ6の両端に第2低抵抗を介して接続された第2電圧フォロワ8からなり、浮動負性抵抗回路Bは、直列接続点3と第2入力端子2間に直列接続された第2乃至第6抵抗11〜15と、第2及び第3抵抗11、12に接続された第1オペアンプ16と、第5及び第6抵抗14、15に接続された第2オペアンプ17からなる。

(もっと読む)

浮動アクティブリアクタ

【課題】既知の浮動アクティブリアクタに比べ用いるオペアンプの数が少なく、内部の回路構成を極限まで簡素化した浮動アクティブリアクタを提供する。

【解決手段】第1及び第2入力端子1、2、インピーダンス3(1)〜3(4)をブリッジ接続したブリッジ回路3、電圧フォロワ4、5、低抵抗値の第1及び第2抵抗6、7からなり、ブリッジ回路3の入力端a、cを各別に第1及び第2入力端子1、2に、ブリッジ回路3の出力端b、dを各別に電圧4、5の入力端に、電圧フォロワ4、5の出力端を各別に第1及び第2抵抗6、7を通して第1及び第2入力端子1、2に接続した構成を有し、ブリッジ回路3の相対する一辺に配置するインピーダンスを同種のリアクタ素子で等リアクタンス値の素子に、相対する他辺に配置するインピーダンスを抵抗素子で等抵抗値の素子に選び、第1及び第2入力端子1、2に信号電圧の供給時、第1及び第2入力端子1、2間に浮動アクティブリアクタが形成される。

(もっと読む)

浮動アクティブインダクタ

【課題】既知のものに比べ用いるオペアンプ数が少なく、簡素化された回路構成であり、内部の回路構成をより簡素化した浮動アクティブインダクタを提供する。

【解決手段】 第1及び第2入力端子1、2間に接続された4素子ブリッジ回路型の1次のパッシブ全域通過形進相回路3、当該パッシブ全域通過形進相回路3の出力進相信号を単位利得増幅する電圧フォロワ4、電圧フォロワ4の出力進相信号を反転増幅する位相反転回路5、電圧フォロワ4の出力と第1入力端子1間に接続した低抵抗値の第1抵抗6、位相反転回路5の出力と第2入力端子2間に接続した低抵抗値の第2抵抗7を備え、ブリッジ回路は、2素子が第1及び第2入力端子1、2間に直列接続した等高抵抗値を有する2つの抵抗3(1)、3(2)で、2素子が第1及び第2入力端子1、2間に直列接続したキャパシタ3(3)と抵抗3(4)であり、当該キャパシタ3(3)と抵抗3(4)の接続点から進相信号を得ている。

(もっと読む)

浮動アクティブキャパシタ

【課題】既知のものに比べ用いるオペアンプ数が少なく、簡素化された回路構成であり、内部の回路構成をより簡素化した浮動アクティブキャパシタを提供する。

【解決手段】 第1及び第2入力端子1、2間に接続された4素子ブリッジ回路型の1次のパッシブ全域通過形遅相回路3、当該パッシブ全域通過形遅相回路3の出力遅相信号を単位利得増幅する電圧フォロワ4、電圧フォロワ4の出力遅相信号を反転増幅する位相反転回路5、電圧フォロワ4の出力と第1入力端子1間に接続した低抵抗値の第1抵抗6、位相反転回路5の出力と第2入力端子2間に接続した低抵抗値の第2抵抗7を備え、ブリッジ回路は、2素子が第1及び第2入力端子1、2間に直列接続した等高抵抗値を有する2つの抵抗3(1)、3(2)で、2素子が第1及び第2入力端子1、2間に直列接続した抵抗3(3)とキャパシタ3(4)であり、当該抵抗3(3)とキャパシタ3(4)の接続点から遅相信号を得ている。

(もっと読む)

浮動アクティブキャパシタ

【課題】用いられるオペアンプの数が少なく、簡素化された回路構成の浮動アクティブキャパシタを提供する。

【解決手段】第1及び第2入力端子1、2間に直列接続された2つの高抵抗3、4、第1入力端子1に接続した1次のアクティブ全域通過形90°遅相回路5、前記90°遅相回路に縦続接続した位相反転回路6、前記90°遅相回路5及び前記位相反転回路6の動作基準電位を設定する仮想接地路9、前記90°遅相回路5の出力と第1入力端子1間に接続した第1抵抗7、前記位相反転回路6の出力と第2入力端子2間に接続した第2抵抗8、前記2つの高抵抗の接続点と仮想接地路9とを接続する電圧バッファ10を備え、第1及び第2入力端子1、2間に信号電圧を供給すると、第1入力端子1に90°進相信号電流が流入し、第2入力端子2から90°進相信号電流が流出し、第1及び第2入力端子1、2間に浮動アクティブキャパシタが形成される。

(もっと読む)

可変容量回路とこれを用いた電圧制御発振回路

【課題】低電圧動作に適し、動作周波数レンジが広げられ、安定動作が得られ、位相ノイズやジッタの低減を図れる。

【解決手段】電圧可変容量回路は、電圧可変容量手段としてのNMOS42と、NMOS42のドレインにソース電位と異なる電位を供給するための電位供給部41とから構成されている。NMOS42のゲート42gと接地端子GNDとの間に発生する等価容量Cgを可変できる電位範囲や、変化の傾きを電気的・回路設計的に調整することが可能となる。更に、電圧制御端子VCに印加する制御電位vcに対して等価容量Cgは単調に変化し、制御電位vcの有効な電位範囲は拡大する。前記電圧可変容量回路をVCOに用いることで、VCOの発振周波数fは、電圧制御端子VCに印加する制御電位vcによって、制御できる。

(もっと読む)

1 - 20 / 30

[ Back to top ]