Fターム[5J106BB08]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 用途 (1,086) | 変調 (40)

Fターム[5J106BB08]に分類される特許

1 - 20 / 40

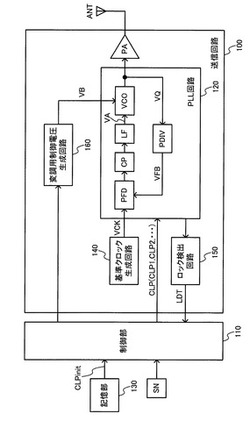

回路装置及び電子機器

【課題】低消費電力でキャリブレーションができる回路装置及び電子機器等を提供すること。

【解決手段】回路装置は、無線による送信処理を行う送信回路100と、送信回路100を制御する制御部110とを含む。制御部110は、第1の送信期間では、送信回路100のキャリブレーションパラメーターCLPとして、第1のキャリブレーションパラメーターCLP1を設定し、送信回路100は、第1の送信期間では、第1のキャリブレーションパラメーターCLP1に基づく第1の送信処理を行う。制御部110は、第2の送信期間では、キャリブレーションパラメーターCLPとして、第1の送信処理での送信状態の検出結果に基づいて更新された第2のキャリブレーションパラメーターCLP2を設定し、送信回路100は、第2の送信期間では、第2のキャリブレーションパラメーターCLP2に基づく第2の送信処理を行う。

(もっと読む)

無線通信のためのディジタル送信機

【課題】改善された性能、低電力消費、低コストのディジタル送信機を提供する。

【解決手段】デカルト座標−極座標変換器230で、受信したデカルト座標から極座標への変換を行う。FIRフィルタ234(または、デルタ−シグマ変調器)により、前記極座標の振幅情報からエンベロープ信号を生成し、位相変調PLL250、VCOにより、前記極座標の位相情報から位相変調された信号を生成する。複数状態増幅器274(または、排他的論理和ゲート)により、前記のエンベロープ信号および位相変調された信号に基づいて、ディジタル変調された信号を生成する。電力増幅器280は、前記のディジタル変調された信号を増幅して、RF出力信号を生成する。

(もっと読む)

周波数シンセサイザ装置及び変調周波数変位調整方法

【課題】2つの変調経路を有する周波数シンセサイザ装置において、DACから電圧制御発振器に出力される制御電圧の振幅を適切に調整することができる。

【解決手段】周波数シンセサイザ装置10は、入力電圧に応じた発振周波数で発振する電圧制御発振器14、電圧制御発振器14からの信号を分周するプログラマブル分周器20、分周信号と基準クロックとの位相差を電圧制御発振器14に出力する周波数位相比較器22、送信データに応じて目標周波数変位分周波数を変位させる場合の調整電圧を電圧制御発振器14に出力するDAC12、調整電圧の校正時に、電圧制御発振器14を基準電圧電源に接続するスイッチ32、任意の送信データをDAC12に出力して発振させた状態で分周信号の周波数をカウントしたカウント値に基づいて、目標周波数変位に対応する調整電圧に対応した調整データを設定する変調周波数変位校正回路30を備える。

(もっと読む)

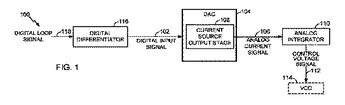

アナログ積分のためのデジタル補償を有するフェイズロックループ

フェイズロックループ(PLL)デバイスは、アナログ積分器によるアナログ電流信号の積分を少なくとも部分的に補償するために、デジタルループ信号を微分するように構成されたデジタル微分器を含む。デジタルアナログコンバータ(DAC)は、デジタル入力信号に基づいてアナログ電流信号を発生する電流源出力ステージを含む。アナログ積分器は、アナログ電流信号を積分して、電圧制御発振器(VCO)を制御するための電圧制御信号を発生する。  (もっと読む)

(もっと読む)

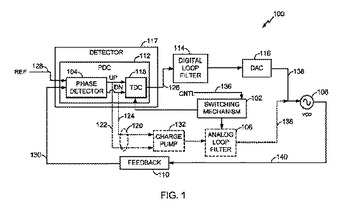

設定可能なデジタル−アナログ位相ロックループ

位相ロックループ(PLL)デバイスは、アナログ位相ロックループおよびハイブリッドアナログ−デジタル位相ロックループ内で構成可能である。アナログモードでは、少なくとも位相検出器、アナログループフィルタおよび電圧制御発振器(VCO)はアナログループを形成するために接続される。デジタルモードでは、少なくとも前記位相検出器、前記電圧制御発振器(VCO)、時間−デジタルコンバータ(TDC)、デジタルループフィルタおよびデジタル−アナログコンバータ(DAC)は前記ハイブリッドデジタル−アナログループを形成するために接続される。  (もっと読む)

(もっと読む)

無線回路、集積回路装置及び電子機器

【課題】安定したデータ送信ができる無線回路、集積回路装置及び電子機器等を提供すること。

【解決手段】無線回路100は、電圧制御発振回路を有するPLL回路120を有し送信信号を生成して出力する送信信号生成回路110と、送信信号を増幅するパワーアンプ130と、周波数測定回路140とを含む。PLL回路120は、送信データ出力期間の前の期間ではクローズドループ動作に設定され、送信データ出力期間ではオープンループ動作に設定される。周波数測定回路140は、クローズドループ動作からオープンループ動作への切り換え時における送信信号の搬送波信号の周波数シフト量、及び送信データ出力期間における搬送波信号の周波数ドリフト量の少なくとも一方を測定する。

(もっと読む)

2ポイント変調と適応遅延マッチングとを用いるデジタル位相ロックドループ

適応遅延マッチングとともに2ポイント変調をサポートするデジタル位相ロックドループ(DPLL)が記述される。DPLLは、それぞれ、発振器の周波数および/または位相の広帯域および狭帯域の変調をサポートするハイパスおよびローパス変調パスを含む。DPLLは、他の変調パスの遅延と合わせるためにある変調パスの遅延を適応して調整することができる。ある設計において、DPLLは、2つの変調パスのうちの一つに、可変遅延を提供する適応遅延ユニットを含む。適応遅延ユニット内で、遅延計算ユニットは、2つの変調パスに適用される変調する信号と、DPLLにおける位相エラー信号とに基づいて、可変遅延を決定する。補正器は可変遅延の小数部分を提供し、プログラマブル遅延ユニットは可変遅延の整数部分を提供する。 (もっと読む)

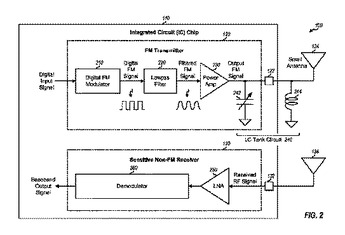

シングルチップ上に集積されたFM送信機及び非FM受信機

例示的な態様は、周波数変調(FM)送信機及び非FM受信機を含み、それらは同一のICチップ上にインプリメントされる。FM送信機は、デジタルFM変調器、ロウパスフィルタ、増幅器、及びLCタンク回路を含む。デジタルFM変調器は、デジタル入力信号を受け取り、デジタル入力信号によってFM変調を行い、デジタルFM信号を供給する。ロウパスフィルタは、デジタルFM信号をフィルタし、フィルタされたFM信号を供給する。増幅器は、フィルタされたFM信号を増幅し、出力FM信号を供給する。LCタンク回路は、出力FM信号をフィルタする。デジタルFM変調器は、PLL内のマルチモジュール分周器の可変分周比を変化させることによってFM変調を行う。デルタ−シグマ変調器は、デジタル入力信号を受け取り、可変分周比を得るために用いられる変調器出力信号を発生する。  (もっと読む)

(もっと読む)

2点FSK変調を用いる周波数シンセサイザのための自己較正方法

【課題】2点FSK変調を用いる周波数シンセサイザの自己較正方法の提供。

【解決手段】周波数シンセサイザ1が、第1の位相ロック・ループおよび高周波アクセス部を備え、高周波アクセス部は、電圧制御発振器の第2の入力に接続されたデジタル/アナログ変換器20を備える。較正動作のために、高周波アクセス部に、第1の位相ロック・ループ内の位相比較器3に接続された第2の電荷ポンプ14および第2のループ・フィルタ15を備える。第2の電荷ポンプ14が、オンに切り替えられると、第2の位相ロック・ループを形成する。デジタル/アナログ変換器20の利得を較正するために、決められた出力周波数に予めロックされた第2の位相ロック・ループの第2の電荷ポンプ14を切り離した後に、電圧比較器21が、デジタル/アナログ変換器20の出力電圧を、第2のループ・フィルタ内に蓄えられた電圧と比較する。

(もっと読む)

位相同期ループ回路

【課題】ループ利得の変動を抑圧できるループ利得検出回路を備えたPLL回路を提供する。

【解決手段】PLL回路内の電圧発振器1で駆動されるカウンタ6と、その出力を周期的に積算するアキュームレータ(ACL)と、ACLのカウント値とレジスタ9に予め設定された設計値とを比較する比較演算回路部8を設け、ACLのカウント値がループ利得と反比例することを応用してPLL回路のループ利得を検出する。検出結果に基づいてチャージポンプ電流等でループ利得の補正を行ってループ利得を校正する。これにより、PLL回路は、PLLを構成する各素子の特性のばらつきに影響しない安定したループ特性を保つことができる。

(もっと読む)

半導体集積回路

【課題】動作モードによって周波数変調を行うか行わないかを選択することによって受信側の負荷を低減することができる半導体集積回路を提供すること。

【解決手段】半導体集積回路1は、2以上の内部回路(ビデオデコーダ11、CPU12など)と、所定の周波数のクロックを発生するPLL31と、周波数を変調させたクロックを発生するSSCG PLL32と、内部回路にPLL31からのクロックか、SSCG PLL32からのクロックのいずれかを選択して内部回路に入力するセレクタ21とを有する。

(もっと読む)

通信用半導体集積回路

【課題】周波数変調及び位相変調の高精度化を図ることが可能な通信用半導体集積回路を提供する。

【解決手段】通信用半導体集積回路は、ループフィルタの出力に第1の係数を乗算したキャリア周波数制御値を出力する第1の乗算器と、変調周波数データに第2の係数を乗算した変調周波数制御値を出力する第2の乗算器と、キャリア周波数制御値と変調周波数制御値とを加算し、その加算結果として前記発振器制御値を出力する第4の演算器と、を備える。第2の係数Kmは、Km=Kc+A×Fmod/Frefの関係にある(Kc:第1の係数、A:補正項(実数)、Fmod:前記変調周波数、Fref:前記基準周波数)。

(もっと読む)

通信装置、発振器、並びに周波数シンセサイザ

【課題】CDMAやOFDMといった大きな包絡線変動を伴う変調方式を使用することができ、送信機に線形性と高効率を両立するLINC送信機を提供する。

【解決手段】変調データの周波数変換を行なうPLLにおいて2ポイント変調方式を採用することで、発振器に入力される変調データはPLLにとって外乱とは見えなくなり、PLLのループ帯域幅に制限されない広帯域変調を実現することが可能となる。また、発振器の積分効果により、サンプリング周波数付近におけるレプリカを、アナログ・スムージング・フィルタを追加することなく大幅に抑制することができ、回路のリコンフィギャラビリティを高めることができる。

(もっと読む)

ゲート時間/デジタル変換器を有するデジタル位相ロックドループ

デジタルPLL(DPLL)、時間/デジタル変換器(TDC)および制御ユニットを含む。TDCは、位相情報を量子化するために、短い時間の間、周期的に有効され、電力消費を削減するために、残り時間の間、無効にされる。TDCは、第1のクロック信号と第1の基準信号を受信し、第1のクロック信号と第1の基準信号との位相差を示す出力をTDCに提供する。制御ユニットは、主基準信号に基づいてイネーブル信号を生成し、イネーブル信号でTDCを有効および無効にする。ある設計において、制御ユニットは、第1の基準信号および第2の基準信号を獲得するために、主基準信号を遅らせ、主基準信号および第2の基準信号に基づいてイネーブル信号を生成し、TDCに対する第1のクロック信号を獲得するために、イネーブル信号で主クロック信号をゲートする。 (もっと読む)

標準信号発生器及び標準信号発生システム

【課題】恒温設備を設けることなく位相ドリフトを低減させて、標準信号発生器のウォームアップ時間の短縮を図ること。

【解決手段】位相補正データ生成部4のA/D変換器41は、基準信号生成部1から出力された基準信号14aの周波数をサンプリング周波数として標準信号100aをA/D変換する。プログラマブル周波数ディバイダ42が分周した基準信号14aの周期で、データ間引き部43はA/D変換器41からのビート信号41aを間引き抽出する。補正量算出部40は、データ間引き部43からのビート信号43aの電圧値に基づいて、位相ドリフト量Δθdriftを算出する。その位相ドリフト量Δθdriftに基づいて標準信号100aの位相補正を行う。

(もっと読む)

クロック信号源

【課題】周波数拡散させたクロック信号に対して正確な位相シフトを実現する。

【解決手段】周波数拡散クロック源40で周波数拡散されたクロック信号を位相シフタ30で位相シフトさせるとき、演算回路20に対して、周波数拡散クロック40から単位遅延セルの直列接続個数Nsを表す第1のコードを与え、この第1のコードの変化によって表される周波数拡散クロック源40の単位遅延セルの直列接続個数Nsの時間的変化、および希望するシフト量Saに基づいて、位相シフタ30における単位遅延セルの直列接続個数Npを表す第2のコードを生成する。

(もっと読む)

スペクトラム拡散クロック発生回路

【課題】入力される基準クロック信号に基づく変調波を生成するスペクトラム拡散クロック発生回路であって、回路の製造プロセス、電源、又は、温度等に起因する変調波の変動を低減するスペクトラム拡散クロック発生回路を提供すること。

【解決手段】出力信号を分周した分周出力信号を出力する分周器と、前記分周出力信号と受信した基準クロック信号との位相差を検出する位相比較器と、前記位相差に応じて充放電信号を発生するチャージポンプと、前記充放電信号に応じた差信号を発生するループフィルタと、前記差信号と変調波とが入力されて被変調波を生成する変調回路と、前記被変調波に応じた周波数のクロックを発生するクロック発生器とを有するスペクトラム拡散クロック発生回路であって、前記基準クロック信号に基づき前記変調波を生成する変調波生成回路を有するスペクトラム拡散クロック発生回路。

(もっと読む)

変調回路方式及びその電圧制御発振器

【課題】PLLループの電圧制御発振器にかかる回路負担を抑えることにより、電圧制御発振器の性能が低下することの無い変調回路方式及びその電圧制御発振器を提供することを目的とする。

【解決手段】電圧制御発振器12を具備するPLLループと、変調信号とPLLループ外調整電圧とを加算する加算手段17と、加算手段17の出力を電圧制御発振器12へ供給する周波数粗調整手段18とを有し、加算手段17において加算されて出力された、変調信号とPLLループ外調整電圧との加算信号を、周波数粗調整手段18を介して電圧制御発振器12へ供給し、PLLループにおける電圧制御発振器12の発振周波数信号に加算信号を重畳して変調信号を生成する。

(もっと読む)

通信用半導体集積回路

【課題】通信用半導体集積回路で、発振用の電界効果トランジスタ(FET)のしきい値電圧Vthのバラツキによる送信用電圧制御発振器TXVCOの発振振幅値のバラツキを補償すること。

【解決手段】位相変調ループ制御回路PM_LPは、しきい値電圧発生回路Vth_Genと、送信用電圧制御発振器TXVCOの出力と送信用RF電力増幅器RF_PAの入力との間の可変利得増幅器BFとを含む。しきい値電圧発生回路Vth_Genは、TXVCOの発振用FETQN1、QN2:QP1、QP2のVthと等しいVthのFETQn17、Qp17を含む。送信用電圧制御発振器TXVCOの発振電圧振幅値のバラツキをRF_PAの入力で補償するように、可変利得増幅器BFの可変増幅利得がVth_Genからの出力V1に応答して設定される。

(もっと読む)

周波数変調器およびこれを用いたFM送信回路

【課題】PLLを用いた周波数変調器を簡素化する。

【解決手段】周波数変調器100において、VCO12は、入力端子13に印加された電圧Vcntに応じた周波数で発振する。分周器14は、VCO12の出力信号Soutを分周する。位相比較器16は、分周器14の出力信号Sfbを、基準クロック信号CKrefと比較し、位相差に応じた電圧Vpcを出力する。ループフィルタ18は、位相比較器16の出力端子17からVCO12の入力端子13に至る経路上に設けられ、位相比較器16の出力電圧Vpcの高周波成分を除去する。ループフィルタ18が位相比較器16の出力端子17からVCO12の入力端子13に至る経路と接続される端子とは別に、変調信号Sinを入力するための端子19をループフィルタ18に設ける。

(もっと読む)

1 - 20 / 40

[ Back to top ]