Fターム[5J106DD29]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | 同期化クロック制御回路 (365) | 複数の同期化クロック制御回路 (29)

Fターム[5J106DD29]に分類される特許

1 - 20 / 29

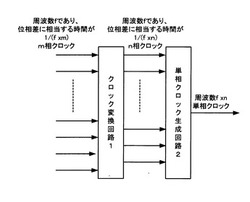

クロック生成回路、及びクロック生成方法

【課題】一種類の多相クロックより多くの周波数の種類の単相クロックを得ることができるクロック生成回路及びその方法を提供する。

【解決手段】少なくともn個の位相補間器を有し、周波数がfで位相差が1/(f×m)づつ異なるm相クロックを、周波数がfで位相差が1/(f×n)づつ異なるn相クロックに変換するクロック変換回路1と、前記n相クロック信号の一部又は全部を用いて、周波数(f×n)/Aの単相クロック信号を生成する単相クロック生成回路2と、前記位相補間器に設定する内分比を制御する制御回路とを有し、前記各位相補間器は、前記m相の内の異なる二つのクロックを入力し、それらのタイミング差を、制御回路により設定した内分比で分割した遅延時間のクロックを生成して出力し、前記制御回路は、基準クロックと、回路の末端で分配されたクロックとのタイミングとが一致するように内分比を制御する。

(もっと読む)

多相信号を生成するための方法、回路及びシステム

【課題】位相誤差を補償しながら設定可能な位相オフセットで多相信号を生成するための方法等を提供する。

【解決手段】一実施形態において、回路は、第1の周波数及び第1の位相を有する第1の周期信号を生成する第1のLC型電圧制御発振器(LCVCO)と、第2の周波数及び第2の位相を有する第2の周期信号を生成する第2のLCVCOとを有し、第2の位相は、90度オフセットで第1の位相に対してオフセットされる。

(もっと読む)

受信装置及びゲイン設定方法

【課題】受信特性を向上させることのできる受信装置を提供する。

【解決手段】受信装置は、受信データD1に基づいて抽出クロックCLKを生成するクロックデータリカバリ回路2と、受信データD1のジッタ量に応じて、上記クロックデータリカバリ回路2内のフィルタ回路11のゲインパラメータG1を設定するゲイン設定部3とを有する。

(もっと読む)

位相同期回路及びその制御方法

【課題】従来技術の位相同期回路では、入力クロックの切り替え時において、安定した出力クロックを生成することができないという問題があった。

【解決手段】本発明にかかる位相同期回路は、入力クロックを選択するセレクタ3と、入力クロックを分周する1/m分周器4と、フィードバッククロックを分周する1/n分周器5と、位相差検出器と、電圧保持回路30を有する電圧制御発振器10と、電圧保持回路31を有する電圧制御発振器11と、電圧制御発振器10,11のうちいずれかの出力を出力クロックとして出力するセレクタ13と、電圧制御発振器10,11のうちいずれかの出力をフィードバッククロックとして出力するセレクタ12と、備え、保持モードの電圧制御発振器が出力クロックfoutを生成し、通常モードの電圧制御発振器がフィードバッククロックを生成している場合に、入力クロックの切り替えが行われる。

(もっと読む)

CDR回路

【課題】入力データに対する瞬時応答特性を備えかつジッタが大きな入力データが入力された時にも出力ジッタを低減可能な小型低消費電力のCDR回路を提供する。

【解決手段】CDR回路は、入力データ4のタイミングに合うように出力クロックの位相を調整するVCO11と、VCO11の出力クロックのタイミングに合うように再生クロック7の位相を調整するVCO13と、VCO11,13の発振周波数を制御する制御信号8を発生する周波数制御回路である周波数比較器2およびVCO12と、VCO11の出力端子とVCO13の入力端子との間に挿入された減衰器30とを備える。

(もっと読む)

クロック装置

【課題】複数のクロック信号を出力するPLL回路において、その特性を問わず、リセットを従来よりも適切なタイミングで行うことを目的とする。

【解決手段】クロック装置は複数のクロック信号を出力するクロック回路を備え、出力するクロック信号を使用して動作している複数の周辺回路からエラー信号を受信し、受信したエラー情報を用いて、前記クロック回路をリセットするか否かを判定し、リセットすると判定した場合に、前記クロック回路をリセットする。

(もっと読む)

閉ループ・クロック訂正方法および閉ループ・クロック訂正制御システム適応装置

【課題】閉ループ・クロック訂正方法および閉ループ・クロック訂正制御システム適応装置を提供する。

【解決手段】閉ループ・クロック訂正システムおよび方法は、少なくとも1つの同位相クロックおよび少なくとも1つの直交位相クロックを含む2つ以上の入力信号を調整するステップと、調整された直交位相クロック信号を、4象限補間出力クロック位相を生成可能なデバイスに印加するステップとを含む。補間出力クロック位相は、遅延されて測定デバイス用のクロックを形成する。2つ以上の調整された入力信号は、測定デバイス上で補間出力クロック位相の範囲にわたって測定される。測定デバイスからのサンプル情報を使用して、同位相クロックおよび直交位相クロック上の誤差が決定される。同位相クロックおよび直交位相クロックは、決定された誤差情報を使用して適応される。

(もっと読む)

クロック生成回路

【課題】位相ロックの精度を向上する。

【解決手段】クロック生成回路は、出力クロックの周期または位相を段階的に遅延する第1の遅延回路および前記第1の遅延回路の遅延時間を設定し制御する第1のカウンタを有する逓倍回路と、前記逓倍回路内の第1の遅延回路から出力された前記出力クロックを入力し、前記出力クロックを所定時間遅延させる第2の遅延回路および前記第2の遅延回路の遅延時間を設定し制御する第2のカウンタを有する位相同期回路を備え、前記逓倍回路は、初期値が第1の値であり第1のカウンタのカウンタ値が一定時間以内で変化しない場合に第2の値が設定される第3のカウンタをさらに有し、前記第3のカウンタのカウンタ値が前記第1の値から前記第2の値に変化した時、前記第2の遅延回路の遅延時間が前記第1の遅延回路の遅延時間と同じかあるいは少し長い遅延時間となるように前記第2のカウンタのカウンタ値を設定する。

(もっと読む)

基準周波数発生システム及び基準周波数発生装置

【課題】冗長化された基準周波数発生システムにおいて、現用側と予備側での出力切替時に出力信号のタイミングが急激に変動するのを防止する。

【解決手段】現用側の基準周波数発生装置51においては、自機のGPS受信機21aが生成する1PPS信号がPLL回路22aに供給される。予備側の基準周波数発生装置52においては、現用側の基準周波数発生装置51のGPS受信機21aからケーブル101を介して出力された1PPS信号がPLL回路22bに供給される。予備側に入力された1PPS信号は、ケーブル101と遅延量が等しいケーブル102を介して現用側に戻される。現用側の基準周波数発生装置51は、自機のGPS受信機21aからの1PPS信号と、予備側に出力して戻された1PPS信号と、の時間差に基づき補正用信号を出力する。予備側の基準周波数発生装置52は、補正用信号に基づいて、PLL回路22bの出力信号の位相を調整する。

(もっと読む)

冗長構成システムにおける基準信号同期制御方法

【課題】運用系と待機系の位相差を正確に求めることが出来る冗長構成システムにおける基準信号同期制御方法を提供することである。

【解決手段】装置の基準信号を生成し、運用系と待機系の冗長構成を成すユニットにおいて、運用系のハードウェアと、待機系のハードウェアで、同じタイミングの基準信号を用いて装置を動作させるために、運用系から出力する基準信号は、各機能部の他、待機系にも送り、待機系は、運用系から入力される基準信号と自ら生成する基準信号との位相差を、運用系から待機系までの遅延を擬似的に実現させ、そこから求められた遅延量に従い、待機系が生成する基準信号に遅延分のオフセットをかけることで、運用系の基準信号と同期させる。

(もっと読む)

PLL回路

【課題】 ループゲインを大きくすることができ、ループ利得が上がらない場合でも、ロック時の位相ノイズを良化できるPLL回路を提供する。

【解決手段】 入力端子1からの基準周波数を第1,3の分周器2,9で分周し、VCO8からの出力と発振器13からの出力をミキサ14で合成し、MCF15aで周波数を選択して、第2,4の分周器3,10で分周し、第1,第2の分周器2,3からの出力を位相比較器4で位相比較し、LPF5で平滑化し、第3,第4の分周器9,10からの出力を位相進み/遅れ検出器11で位相の進み又は遅れを検出し、積分器12で積分して電圧を出力し、加算器6でLPF5からの出力と積分器12からの出力を加算してVCO8に出力し、MCF15aからの出力を増幅器16で増幅して出力端子17に出力し、基準周波数に対して発振器13での周波数を調整するPLL回路である。

(もっと読む)

スペクトラム拡散クロックジェネレータ

【課題】 PVT変動に起因して周波数変調プロファイルが変化することを防止することができるスペクトラム拡散クロックジェネレータを提供する。

【解決手段】 入力クロックCLKINと出力クロックCLKOUTの位相を位相比較記30で比較し、その比較結果信号POに基づいて制御回路20で新たな遅延パターンを算出し、その新たな遅延パターンに従って1クロックパルス毎に遅延セル11_0,11_1,11_2,11_3,…,11_N−2,11_N−1,11_Nの段数を切替信号S[0],S[1],S[2],S[3],…,S[N−2],S[N−1],S[N]により切り替えながら入力クロックCLKINを入力させて周波数変調を行なう。

(もっと読む)

半導体集積回路

【課題】本発明は、Ser/Des回路において、休眠ステートからパワーアップの状態へ遷移した際の受信エラーを減少できるようにする。

【解決手段】たとえば、受信機21が、休眠ステートP1からパワーアップの状態P0に遷移したとする。すると、リセット制御回路21mは、ディレイ回路21m-1によって、PLL31からのシステムクロックのカウントを開始する。そして、ディレイ回路21m-1がXサイクルをカウントした後に、リセット制御回路21mは、ディジタルフィルタ21eおよびPI制御回路21fのリセットを解除するように構成されている。

(もっと読む)

信号発生装置

【課題】IC化が可能なように、VCOの出力の位相雑音のうち、中心周波数から所望の離調周波数における位相雑音を軽減化した信号発生装置を提供することである。

【解決手段】基準信号を出力する基準信号源1と、発振周波数を電圧制御可能な可変信号源3aを有し、可変信号源の出力信号を基準信号に位相同期させる複数のPLL手段31、32、・・3)と、各PLL手段の該各可変信号源の出力信号を合成する合成手段2と、各可変信号源の出力信号の位相が前記合成手段により合成後に同一となるように各可変信号源の出力信号の位相を調整する移相手段41、42、・・4Mとを備えた。

(もっと読む)

DLL回路

【課題】 クロックの立ち上がり及び立ち下がりに同期した内部クロックを生成するDLL回路においては、高精度が要求されることから回路規模が大きくなるという問題がある。

【解決手段】 Rise用の遅延調整回路とFall用の遅延調整回路を備え、Fall用の遅延調整回路にはRise用の遅延調整回路でRise側を調整したクロックを入力する。入力されるクロックのRise側が調整されていることから、Fall側の遅延差は非常に小さくなる。そのため、Fall用の遅延調整回路、カウンタの回路規模が大幅に削減できる。その結果少ない回路規模で、高精度のDLL回路が得られる。

(もっと読む)

半導体記憶装置及び半導体装置

【課題】DLL回路を備えた半導体記憶装置のチップを複数備えた半導体装置の消費電力の低減。

【解決手段】DLL(Delay Lock Loop)を備えた半導体記憶装置の積層モジュールまたは半導体記憶装置を複数有するマルチチップモジュール(MCM)において、DLLで遅延調整されたクロック信号(CLK)を、一の半導体記憶装置と他の半導体記憶装置間で共用するための専用パッド(PAD)を有し、一の半導体記憶装置のDLLを動作させ、他の半導体記憶装置ではDLLを動作させず、一の半導体記憶装置の前記専用パッドから、DLLで遅延調整されたクロック信号(CLK)から作られる、差動の外部クロック信号(CLK、CLKB)に同期した、フライングロッククロック信号を出力し、他の半導体記憶装置は、フライングロッククロック信号を、専用パッドから入力する。

(もっと読む)

ダブル・データ・レート・システム

集積回路用の拡張可能なタイミングアーキテクチャを提供する。拡張可能なタイミングアーキテクチャは、異なる操作クロック周波数で使用される金属プログラム可能な部品を提供する。いくつかの実施例において、アーキテクチャは、ダブル・データ・レート・メモリ回路を有するマスタ/スレーブDLLを利用する。  (もっと読む)

(もっと読む)

スイッチ可能なフェーズロックループ及びスイッチ可能なフェーズロックループの動作方法

【課題】PLL及びPLLの動作方法に関し、制御可能なオシレータが出力信号を発生し且つPLLの入力クロック信号として使用するために第一クロック信号及び第二クロック信号の間でスイッチオーバーさせる。

【解決手段】現在使用されているクロック信号(CKin1又はCKin2)が出力信号を発生するために、このクロック信号と出力信号との間の位相差が決定され且つオシレータの制御のために使用され、一方現在使用されていないクロック信号(CKin2又はCKin1)が出力信号を発生するために、出力信号に関してのその周波数差が決定され且つ格納され且つ継続的にアップデートされ且つ、前に使用されていないこのクロック信号へのスイッチオーバーの後にオシレータの制御のために提供される。PLL出力信号はどのようなスイッチオーバーに関連する周波数変化よりも迅速に追従することが可能である。

(もっと読む)

クロック供給装置

【課題】クロック供給ユニットを複数備え、これらクロック供給ユニットのいずれかを運用系ユニットとし、その他のユニットを待機系ユニットとする冗長構成を有するクロック供給装置において、運用系ユニットを切り替える際に生じる供給クロック信号の位相変動を低減することを目的とする。

【解決手段】自ユニット20が待機系ユニットであるとき、運用系ユニット10から入力される運用系ユニットのDPLL12からのクロック信号を基準として、自ユニット20のDPLL22の出力クロック信号を、運用系ユニット10のDPLL12の出力クロック信号に、所定の位相差を持って同期させるユニット間同期部21、37、39を、クロック供給ユニット10、20に備えて構成する。

(もっと読む)

ADSLのTTRオフセット調整装置及びその方法

【課題】ADSL装置とTCM−ISDN装置とが整合されてサービスされるときに発生するNEXTまたはFEXTのノイズをTTRのオフセット調整を通じて除去することのできるADSLのTTRオフセット調整装置及びその方法を提供する。

【解決手段】TTRcに同期された第1及び第2クロックを相互に同期化し、前記同期化された第2クロックを一定の大きさの第3クロックに分周し、前記TTRcを前記分周された第3クロックを用いてハイクロック及びロウクロックに区分して各々カウントし、オフセット調整値の分だけ前記カウントされたハイクロック及びロウクロックを各々オフセット補正し、補正された第4クロック及び前記第1及び第2クロックを前記ADSL装置に提供するようにする。

(もっと読む)

1 - 20 / 29

[ Back to top ]