Fターム[5J106DD34]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | デジタル回路 (2,545) | CPU (108)

Fターム[5J106DD34]に分類される特許

1 - 20 / 108

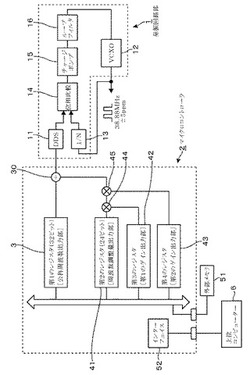

発振器

【課題】周波数の可変幅を容易に変更することができ、また周波数を高精度に調整することができる発振器を提供すること。

【解決手段】第1のレジスタ3により公称周波数に対応するディジタル値を出力する。第2のレジスタ41により、公称周波数に対して周波数比率で表した周波数の調整量を出力する。一方前記周波数調整量であるディジタル値の可変範囲(フルレンジ)と周波数比率で表わした周波数の可変幅とを対応させるようにゲインを決め、このゲインを第2のレジスタ41からのディジタル値に乗算し、この乗算値と公称周波数に対応するディジタル値とを加算して周波数設定信号とする。

(もっと読む)

クロック発振回路

【課題】発振周波数のトリミングを行うクロック発振回路であって、CR発振回路の特性に起因する発振周波数のばらつきを低減することが可能なクロック発振回路を提供する。

【解決手段】クロック発振回路は、周波数調整コードに応じた発振周波数のクロック信号を生成する発振部101と、発振部101の発振周波数をカウントするOSCクロックカウンタ102と、外部接続された水晶発振器の発振周波数をカウントする基準クロックカウンタ103と、両発振周波数の比較を行う比較回路104とを備える。また、周波数調整コードの自動探索を行う探索回路105を備える。探索回路105は、周波数調整動作時において、発振部101に対する周波数調整コードの設定と、比較回路104による比較結果に応じた周波数調整コードの更新とを繰り返し行うことにより、周波数調整コードの自動探索を行う。

(もっと読む)

周波数シンセサイザ

【課題】 外部基準信号の入力断で高速にスイッチを切り替えて一定の電圧を発振器の制御電圧として出力でき、出力周波数の変動量を最小限に抑えることができる周波数シンセサイザを提供する。

【解決手段】 制御回路11が、検波回路10からの検波出力を入力し、外部基準入力信号「入」の場合には、SW3にPLL−IC1の出力をループフィルタ4に出力させる切替信号を出力し、外部基準入力信号「断」の場合には、SW3に可変抵抗2の出力をループフィルタ4に出力させる切替信号を出力し、スイッチ高速切替回路12が、外部基準入力信号の「断」を検出して制御回路11より高速にSW3に可変抵抗2の出力をループフィルタ4に出力させる切替信号を出力する周波数シンセサイザである。

(もっと読む)

情報処理システム

【課題】システムリセット時の起動時間を短縮可能な情報処理システムを提供する。

【解決手段】複数の機能モジュールの内の機能モジュール1では、システムリセット信号にてPLL回路10及び信号処理部12をリセットした後にPLL回路10へのリセットを解除する。リセット解除後にPLL回路10で生成された内部クロック信号がシステムクロック信号に位相ロックしていない場合には起動中を示す第1の起動状態信号を機能モジュール2に供給する。位相ロックしている場合には起動完了を示す第2の起動状態信号を機能モジュール2に供給すると共に信号処理部12へのリセットを解除する。機能モジュール2では、第1の起動状態信号にてPLL回路20及び信号処理部22をリセットする。そして、第2の起動状態信号にてPLL回路20へのリセットを解除し、リセット解除後に、位相ロックした時に信号処理部22へのリセットを解除する。

(もっと読む)

制御装置、光受信装置および制御方法

【課題】特性の制御を安定させること。

【解決手段】制御装置120は、第1演算器122と、更新制御回路123と、取得部125と、第2演算器126と、を備えている。第1演算器122は、処理装置の第1特性の検出結果に基づいて、第1特性を変化させる処理装置のパラメータを操作する。更新制御回路123は、第1演算器122の機能を更新する場合に、第1演算器122によるパラメータの操作を停止させる。取得部125は、パラメータの操作量と、第1特性を変化させる処理装置の第2特性の変化量との関係を示す関係情報を取得する。第2演算器126は、更新制御回路123によって第1演算器122によるパラメータの操作が停止している場合に、取得部125によって取得された関係情報と、第2特性の検出結果の変化量と、に基づく操作量によってパラメータを操作する。

(もっと読む)

クロック生成装置、クロック生成方法及びプログラム

【課題】目的の周波数からずれた周波数のクロックをクロックの供給先に与える危険性の少ない、クロック生成装置を提供する。

【解決手段】各クロック供給部10,20に、水晶発振器であるVCXO11,21を目的の周波数で発振させるために設定された基準値と基準値が設定された時を示す設定時情報とを記憶するメモリ14,24と、VCXO11,21の生成するクロックを他のクロック供給部のVCXOの出力するクロックに同期させる同期手段とをそれぞれ備える。メモリ14,24の記憶内容に基づき、最も設定時情報が新しいVCXOを選別し、その選別したVCXOを基準値に基づいて発振させて目的の周波数のクロックを生成させる。他のVCXOには、選別したVCXOの生成したクロックに同期したクロックを生成させる。

(もっと読む)

PWM信号生成装置

【課題】PWM信号生成装置において、回路規模を小さくして効果的に放射雑音等のノイズを低減する。

【解決手段】CPU204、カウンタ201、レジスタ202、及びコンパレータ205は基準クロックの周波数をその一周期未満の時間で変動させた変動クロックを生成する。TFF206は基準クロックに応じて変動クロックを第1のPWM信号として出力する。TFF251は基準クロックを所定の時間遅延させた遅延クロックに応じて変動クロックを第2のPWM信号として出力する。セレクタ252は第1及び第2のPWM信号を選択的にPWM信号として出力する。

(もっと読む)

クロック発生装置及びクロック信号生成方法

【課題】CPUに供給するクロック信号の周波数に関わらず、周辺回路に所定の周波数のクロック信号を供給することができるクロック信号生成回路及びクロック信号生成方法を提供する。

【解決手段】本発明にかかるクロック信号生成回路は、CPUに入力される第1クロック信号から、周辺回路に入力される所定の周波数を有する第2クロック信号を生成する。外部から入力される逓倍比及び分周比のうち少なくとも1に基づき、発振子が出力するクロック信号から入力される第1クロック信号を生成する第1クロック生成部と、第1クロック信号から第2クロックを作成するための基準値を算出する基準値算出部と、第1クロック信号のカウント値と基準値との比較結果に基づき、第2クロックを生成する第2クロック生成部とを有し、基準値算出部は、逓倍比及び分周比のうち少なくとも1つが変更され第1のクロック信号の周波数が変更されると、基準値を再度算出する。

(もっと読む)

発振周波数補正装置

【課題】同期信号の検出が困難なときにも正確な発振周波数のクロック信号を生成できるようにした発振周波数補正装置を提供する。

【解決手段】電源投入時の劣化検出タイミングにおいて、定電流源23から抵抗器22に通電して得られたA/D変換器6のAD変換値(抵抗器22の端子電圧VR)に基づいて、CPU2が逓倍数設定値FMULRを補正する。この場合、定電流源20を用いることなく定電流源23が作動して抵抗器22に通電する。CPU2は、抵抗器22の端子電圧を測定することでCR発振器14内の抵抗器R1の抵抗値の経年変化を反映し、この変化に基づいてCR発振回路8のクロック信号CLKの逓倍数設定値FMULRを補正する。

(もっと読む)

周波数シンセサイザ装置及びその製造システム

【課題】 多数の類似機種を製造する場合でも、製造工程や検査工程における人為的なミスをなくし、適正な仕様とすることができる周波数シンセサイザ装置及びその製造システムを提供する。

【解決手段】 周波数シンセサイザ装置1のハードウェア識別子回路13が機種に対応するハードウェア識別子を記憶し、外部PC2が複数のハードウェア識別子とそれに対応するパラメータを記憶しており、マイクロコントローラ12が、外部PC2からハードウェア識別子の要求を受信すると、ハードウェア識別子回路13からハードウェア識別子を読み取って外部PC2に出力し、外部PC2が、周波数シンセサイザ装置1から取得したハードウェア識別子に対応して記憶されているパラメータを読み取って周波数シンセサイザ装置1に出力し、マイクロコントローラ12が、受信したパラメータを不揮発性メモリ14に記憶する周波数シンセサイザ装置及びその製造システムとしている。

(もっと読む)

無線通信機

【課題】信号発生器の周波数設定データを複数の箇所から設定する際に、複雑なスイッチを設けることなく、周波数設定データの衝突を防止し、また、より狭い周波数偏差の要求に応える。

【解決手段】無線通信機100は、PLL回路144を構成するPLLIC128と、PLLICに出力周波数を設定する第1のデータを出力し、少なくとも、PLLICへのアクセス不実行状態と、アクセス待機状態と、アクセス実行状態との3つの状態を遷移するCPU112と、出力周波数を増加もしくは減少させるためPLLICに設定する第2のデータを出力し、少なくとも、PLLICのアクセス可能状態と、アクセス禁止状態との2つの状態を遷移するDSP118とを備え、CPUとDSPとが第1の信号と第2の信号によって互いに状態遷移に関する情報を交換し、PLLICへのアクセスの衝突を防止する。

(もっと読む)

周波数シンセサイザ

【課題】

応答性が高く維持され、かつハードウェアの構成が簡略化されるにもかかわらず、各部の変動やバラツキに対して安定に適応できる周波数シンセサイザを提供する。

【解決手段】

位相同期ループが供給する制御情報に対応した所望の周波数で出力信号を生成する可変周波発振器を有し、前記所望の周波数となり得る目標周波数毎に、前期可変周波発振器に与えられるべき制御情報の初期値が予め登録されたテーブルと、前記所望の周波数が切り替えられたときに、前記位相同期ループの応答を規制し、かつ最新の所望の周波数に対応して前期テーブルに登録されている初期値を前記可変周波発振器に供給する初期値設定手段と、前記位相同期ループのロックアップを前記位相差に基づいて検出するロックアップ検出手段と、前記ロックアップが検出されたときに、前記応答の規制を解除し、かつ前記初期値設定手段による初期値の供給を規制する位相同期再開手段とを備える。

(もっと読む)

通信装置及び周波数シンセサイザ

【課題】使用する周波数帯域で、温度変化による送受信の振幅値の偏差を抑えることができる通信装置を提供すること。

【解決手段】送信信号の信号路に介在して設けられると共に制御電圧の印加により容量が変化する可変容量素子とインダクタンスとを含む共振回路を有し、この共振回路の共振点に応じて高周波の入力信号の振幅を調整する振幅調整回路と、前記信号路が置かれている雰囲気の温度を検出する温度検出部と、一のチャンネルにおける周波数帯域において、送信信号の振幅値が予め設定した値になるようにまたは近づくように、前記振幅調整回路の制御電圧値と温度検出値との関係データを記憶する記憶部と、前記温度検出部の温度検出値と前記関係データとに基づいて振幅調整回路の制御電圧を出力する制御電圧出力部と、を備えるように装置を構成する。

(もっと読む)

PLL装置

【課題】外部からの基準周波数信号の振幅レベルの適正範囲内を特定し、その適正範囲の内外に応じて電圧制御発振器に制御電圧を供給するPLL装置において、温度により動作が不安定になることを防ぐこと。

【解決手段】制御電圧出力部に供給される信号を位相比較部と予備信号供給部との間で切り替える切り替え部と、前記基準周波数信号の信号路とアースとの間に設けられ、当該基準周波数信号の振幅レベルを規制するために、ダイオードを逆並列に接続した保護回路と、この保護回路の雰囲気温度を検出する温度検出部と、外部からの前記基準周波数信号の振幅レベルを検出するレベル検出部と、を備えるようにPLL装置を構成し、検出温度に応じて前記切り替えの基準となるしきい値を設定し、前記ダイオードの温度特性により前記振幅レベルが変わることに対応する。

(もっと読む)

PLL回路のジッタ補正装置

【課題】PLL回路から発生するクロックジッタを検出し、基準クロック周波数と同期するPLL回路のジッタ補正装置を提供する。

【解決手段】ジッタ検出回路2がPLL回路1に入力する基準クロック周波数とPLL周波数とを比較したジッタ情報をマイコン3およびメモリ4に出力し、前記ジッタ情報に基づいてマイコン3は設定されているジッタ幅しきい値を超えるジッタ情報を基準クロック周波数との時間差からジッタ補正値を演算、PLL回路1に出力し、PLL回路1は補正後のPLL周波数を出力する。

(もっと読む)

デジタルクロック再生器

サンプリング装置(110)は、変動する周期時間を有する入力クロック信号(CLKin)を受信し、入力クロック信号(CLKin)の平均周波数より実質的に高い周波数を有するサンプリングクロック信号(CLKsmpl)に基づいて、入力クロック信号(CLKin)をサンプリングする。サンプリング装置(110)は、入力クロック信号(CLKin)の各周期に対して、各周期長値(PL)を生成する。平均化装置(120)は、いくつかの周期長値(PL)をサンプリング装置(110)から受信し、それに基づき、前記数の周期長値(PL)に等しい周期数を含む平均化期間に渡って、入力クロック信号(CLKin)に対して平均周期時間を表す平均周期長値(PLavg)を生成する。出力装置(151)は、平均周期長値(PLavg)およびサンプリングクロック信号(CLKsmpl)に基づいて、安定した出力クロック信号(CLKout)を生成する。 (もっと読む)

PLL発振回路

【課題】 アンロック状態を検査すると共に、自動的に再同期する自動リトライ機能を備えるPLL発振回路を提供する。

【解決手段】 MPU4は、外部基準信号とVCXO3からの出力信号の位相を比較してVCXO3への制御電圧を出力するPLL−IC1からのロック検出信号を入力し、ロック状態においてアンロック状態にするためのアンロックアラームテスト用データをPLL−IC1に設定し、PLL−IC1からのロック検出信号によりアンロック状態を判定すると、外部にアンロックアラーム出力信号を出力し、アンロック状態が第1の期間継続しているか否かを判定し、アンロック状態が第1の期間継続していれば、再同期を行わせるためのデータをPLL−IC1に設定するリトライを実行するPLL発振回路である。

(もっと読む)

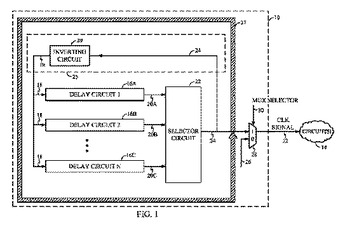

適応クロック発生器、システムおよび方法

機能回路のための、性能マージンを回避し、あるいは小さくするためのクロック信号を生成するために使用することができる適応クロック発生器、システムおよび関連する方法が開示される。特定の実施形態では、クロック発生器は、機能回路内の選択された遅延経路に関連する遅延回路に提供された遅延経路に従って、自律的に、かつ、適合的にクロック信号を生成する。クロック発生器には、入力信号を受け取るように適合され、かつ、出力信号を生成するために、受け取った入力信号を機能回路の遅延経路に関連する量だけ遅延させるように適合された遅延回路が含まれている。遅延回路には、上記出力信号に応答する帰還回路が結合されており、この帰還回路は、遅延回路に発振ループ構成で戻すための入力信号を生成するように適合されている。入力信号を使用して機能回路にクロック信号を提供することができる。  (もっと読む)

(もっと読む)

クロック位相同期回路

【課題】基準クロックに位相同期したクロックを出力するクロック位相同期回路に関し、長期間安定化及び入力擾乱影響を緩和する。

【解決手段】リファレンス入力a位相に同期した電圧制御発振器1の出力信号dを得る為のクロック位相同期回路であって、リファレンス入力aの周波数と電圧制御発振器1の出力信号dの周波数とを一致させて位相比較器3により所定のタイミング毎に位相比較した位相差検出信号bを入力し、それを所定期間順次記憶するメモリ等の記憶手段と、所定期間毎の位相差検出信号の差を位相変動量として求め、位相変動量が許容範囲内の場合は、その位相変動量に対応した電圧制御発振器1の制御電圧に変換し、許容範囲内でない場合は、前回の位相変動量に対応した制御電圧又は自走状態となる制御電圧として、電圧制御発振器1に制御電圧cを入力する演算処理手段とを備えている。

(もっと読む)

時刻同期装置およびその時刻同期補正方法

【課題】GPS衛星電波が受信出来ない時も正確に同期タイミング信号を出力する時刻同期装置およびその時刻同期補正方法を提供する。

【解決手段】内蔵発振器1は、GPS受信器Rからの1pps信号と出力するクロックと間の位相差信号を発振制御部3へ出力し、この位相差を無くす発振周波数制御信号が発振制御部3内蔵発振器1へ出力される。1pps信号が断となった場合、発振制御部3は、ログ部LGのドリフト記録部5と信号断時間記録部6から、予め測定記録していた単位時間あたりの内蔵発振器1の周波数のドリフト量からドリフトを補正する発振周波数制御信号を生成して内蔵発振器1へ出力し、タイミング信号発生部2は、内蔵発振器1からのクロックにより生成した同期タイミング信号を外部へ出力する。

(もっと読む)

1 - 20 / 108

[ Back to top ]