Fターム[5J106GG15]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 制御対象 (2,074) | チャージポンプ回路 (170)

Fターム[5J106GG15]に分類される特許

1 - 20 / 170

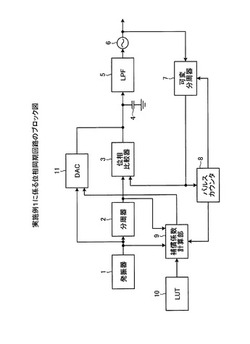

位相同期回路及び位相同期回路制御方法

【課題】少ない分周数を用いた小数点以下の分周における位相の同期を精度良く行う位相同期回路及び位相同期回路制御方法を提供する。

【解決手段】位相比較器3は、基準クロックと比較クロックとの位相差を電流に変換して出力する。キャパシタ4は、位相比較器3から入力された電流に応じて電圧を出力する。VCO6は、キャパシタ4から入力された電圧によって出力周波数を制御し、当該出力周波数を有する信号を出力する。可変分周器7は、VCO6から出力された信号を所定の周期で異なる値に分周することで、小数点以下の値を有する分周を行なった比較クロックを生成する。パルスカウンタ8は、可変分周器7から出力された比較クロックの数をカウントする。補償係数計算部9は、パルスカウンタ8のカウント数を基に、キャパシタ4に対する電流及び電圧の補償値を取得する。DAC11は、前記補償値を基に、キャパシタ4に対して電流を流し補償を行う。

(もっと読む)

PLL回路

【課題】出力クロック信号の周波数制御を精度良く行うことが容易となるPLL回路を提供する。

【解決手段】流出または流入の出力電流を出力するものであって、パルス信号に応じて前記出力電流のオン/オフが切替えられるチャージポンプと、周期性を有する多値の参照信号に応じて前記パルス信号を生成する、パルス信号生成部と、を備え、前記出力電流に応じた出力クロック信号を生成するPLL回路であって、前記参照信号に応じて前記出力電流の電流量を調節する、電流量調節部を備えたPLL回路とする。

(もっと読む)

PLL回路

【課題】低消費電力のPLL回路を提供する。

【解決手段】位相比較回路11は、基準信号と、フィードバック信号の位相を比較し、比較結果に応じた2種の位相差信号(UP信号とDN信号)をチャージポンプ12に供給し、バイアス回路16は、チャージポンプ12にバイアス電流を供給し、制御回路17は、2種の位相差信号のうち一方または両方が活性化状態のときにバイアス回路16の動作を行わせ、2種の位相差信号の両方が非活性化状態のときに、バイアス回路16を停止させる。

(もっと読む)

遅延ロックループ/フェーズロックループにおける移相処理

【課題】

本開示は遅延ロックループ(DLL)及びフェーズロックループ(PLL)における移相処理に関する。

【解決手段】

DLLまたはPLLにおけるチャージポンプは、出力ノードに並列に接続されたキャパシタを備える。一次電流スイッチング回路は、ソース電流でキャパシタを充電し、シンク電流でキャパシタを放電する。補助ソース回路は、大きさの範囲を有する正の位相生成電流をソースする。正の移相生成電流の大きさは、少なくとも1つのソース選択信号により決定される。補助シンク回路は、大きさの範囲を有する負の移相生成電流をソースする。前記負の移相生成電流の大きさは、少なくとも1つのシンク選択信号により決定される。

(もっと読む)

PLL回路

【課題】PLLのチャージポンプ回路からの出力電流ミスマッチにより、PLLの特性劣化に繋がるリファレンススプリアスが発生する問題がある。

【解決手段】基準信号とフィードバック信号との位相差に応じて第1、第2のパルス信号を出力する位相比較器と、第1の制御信号に応じて、前記第1、第2のパルス信号のパルス幅をそれぞれ調整した第3、第4のパルス信号を生成するパルス幅調整回路と、前記第3、第4のパルス信号に応じて出力電流を生成するチャージポンプと、前記チャージポンプの出力に接続され、電流を電圧に変換するループフィルタと、前記ループフィルタの変換した電圧を積分した検出結果を出力する検出回路と、前記検出結果に応じて、前記第1の制御信号を生成する制御回路と、を有するPLL回路。

(もっと読む)

誤ロック防止回路、防止方法及びそれを利用した遅延ロックループ

【課題】遅延ロックループにおいて誤ロックが生じた場合、そこから抜け出すために使用される誤ロック防止回路、防止方法及びそれを利用した遅延ロックループを提供する。

【解決手段】誤ロック防止回路はハーモニックロックを検出する検出器とスタックロックを検出する検出器とで構成される。ハーモニックロック検出器は前記遅延クロックを本発明の特徴的な方法でサンプリングする複数個のフリップフロップ及び論理部で構成される。ハーモニックロック検出器では基準クロックと基準クロックから遅延された複数個の遅延クロックの立ち上がりエッジを比較してこれらの立ち上がりエッジが基準クロックの1周期から離れた場合を検出する。スタックロック検出器は位相検出器の出力信号と前記遅延クロックのうち1つを利用した論理回路であり、論理演算の結果で位相検出器をリセットさせる。

(もっと読む)

PLL

【課題】ジッタが抑制されたPLLを提供する。

【解決手段】PLLは,基準クロックとフィードバッククロックとの位相差信号を遅延し,異なる時間遅延させた位相差信号に応じてチャージ電流を生成する複数のチャージポンプCPを有す。また当該複数のチャージポンプが生成するチャージ電流を加算して出力するチャージポンプ等化器と,ループフィルタと電圧制御発振器の理想特性を持ち,位相差信号の位相差を有する位相差デジタル値を入力して理想特性に基づいてレプリカ出力を生成するレプリカ回路10と,レプリカ出力と理想出力との誤差信号と前記位相差信号との相関値を平滑化してチャージポンプ係数を生成し,複数のチャージポンプそれぞれに負帰還する係数生成回路20−1とを有し、複数のチャージポンプはチャージポンプ係数に応じた電流値を持つチャージ電流をそれぞれ生成する。

(もっと読む)

スペクトラム拡散クロックジェネレータ

【課題】 残ピークノイズを低減させることができるとともに、ジッターの増大を防止することのできるスペクトラム拡散クロックジェネレータを提供する。

【解決手段】 実施形態のスペクトラム拡散クロックジェネレータは、チャージポンプ回路1が、出力電流量が設定に応じて変化する可変電流源を有し、位相比較器14により検出された位相差に応じた期間、VCO11へ印加する電圧を制御するためのチャージ電流を出力する。

(もっと読む)

遅延制御回路、チャージポンプ回路、及びチャージポンプ回路における充放電電流制御方法

【課題】トランジスタがアンバランスであってもチャージポンプ回路に最適なバイアス電圧を与えられる遅延制御回路を提供する。

【解決手段】所定の信号を受けて電流入出力端子から充放電を行うチャージポンプ回路と、電流入出力端子の端子電圧に基づく電圧が電源として供給される遅延回路と、チャージポンプ回路の充放電電流の基準となるバイアス電圧を生成するバイアス生成回路と、を備え、チャージポンプ回路及び遅延回路が、それぞれ、第1導電型トランジスタと、第2導電型トランジスタを含んで構成され、バイアス生成回路が、第1導電型トランジスタの相互コンダクタンスと第2導電型トランジスタの相互コンダクタンスの和に基づいて、バイアス電圧を生成する。チャージポンプ回路の充放電により遅延回路の電源電圧を制御し、これにより遅延回路の遅延時間を制御する。

(もっと読む)

PLL回路および半導体装置

【課題】 PLL回路の発振精度の低下を抑制しつつ、ロックアップタイムを短縮する。

【解決手段】 PLL回路は、制御電圧に応じた周波数の出力信号を生成する電圧制御発振器と、出力信号を分周する分周器と、基準信号と分周された出力信号との位相差を検出し、位相差に応じて第1検出信号および第2検出信号を生成する位相比較器と、第1検出信号に基づいてオン/オフが制御される第1スイッチおよび第2検出信号に基づいてオン/オフが制御される第2スイッチを含み、制御電圧を調整するチャージポンプ回路と、チャージポンプ回路により充放電される容量素子を含み、チャージポンプ回路の出力を平滑化して制御電圧を生成するローパスフィルタと、電圧制御発振器に初期電圧を与える初期設定期間に、第1スイッチおよび第2スイッチの少なくとも一方をオンし、容量素子の充放電を制御することにより、制御電圧を初期電圧に設定する電圧供給部とを有している。

(もっと読む)

PLL回路

【課題】PLL回路のロック状態での定常位相誤差を抑制する。

【解決手段】PLL回路は,レファレンスクロックとフィードバッククロックの位相を比較し,当該位相の差を示す位相比較信号を出力する位相比較器と,位相比較信号が示す位相の差に応じた期間,第1のチャージポンプ電流と第2のチャージポンプ電流とを出力するチャージポンプ回路と,第1及び第2のチャージポンプ電流に基づく電荷を蓄積するキャパシタを有し,蓄積電荷による制御電圧を生成するループフィルタと,制御電圧に応じた周波数の出力クロックを生成する発振器と,出力クロックを分周して前記フィードバッククロックを出力する分周器とを有し,さらに,ロック状態のときに,位相比較信号が示す位相の差に応じて,当該位相の差が抑制されるように,第1または第2のチャージポンプ電流の電流値を調整するチャージポンプ調整回路とを有する。

(もっと読む)

無線通信装置

【課題】無線通信装置の変調精度の低下を抑制しつつ、スプリアスによる受信特性の低下を抑制する。

【解決手段】デジタル部2は、アナログ部1にて周波数変換された受信信号の復調処理を行う。PLL回路25は、前記デジタル部のクロックを発生する。PLL設定変更部24は、現在の通信状態が受信状態であり、チャネル周波数内にスプリアスが存在し、受信電力が閾値に満たない場合、クロックCKのジッタを増加させ、それ以外の場合、クロックCKのジッタを通常設定にする。

(もっと読む)

クロック発生器、電子機器、及びクロックを発生するための制御方法

【課題】周波数変調機能をオフした際のロックアップタイムを短縮することが可能なクロック発生器、及びクロック発生器の制御方法、並びに電子機器を提供すること。

【解決手段】周波数変調機能を有するクロック発生器で、リファレンスクロックを元にフィードバック制御を加えて、位相の同期した出力クロックを出力する位相同期ループと、出力クロックの周波数を変動させる変調制御回路と、を備え、変調制御回路は、周波数変調機能がオフされた際に、出力クロックの周波数を所望の周波数へ収束させるタイミングを速くする構成とする。

(もっと読む)

位相比較器およびクロックデータリカバリ回路

【課題】充放電流を切り替えるスイッチを確実に動作させ、高速化に対応できチャージポンプ回路の機能を保持できる位相比較器およびクロックデータリカバリ回路を提供する。

【解決手段】入力データと第1のラッチ111のラッチデータの論理不一致を検出する第1の検出回路と、第1のラッチのラッチデータと第2のラッチ112のラッチデータの論理不一致を検出する第2の検出回路と、第1の検出回路および第2の検出回路の検出結果に応じて、電流を充電または放電を切り替えるための切替スイッチ機能を含むチャージポンプ回路と、を有し、第1の検出回路、第2の検出回路、およびチャージポンプ回路は、第1および第2の検出回路の論理不一致判定部とチャージポンプ回路の充放電流を切り替える切替スイッチとが複合化された検出回路複合型チャージポンプ回路120として形成されている。

(もっと読む)

位相同期回路

【課題】位相同期回路においてロックアップを高速化する。

【解決手段】位相同期回路100は、基準信号の周波数にXを乗じて得られる出力周波数を有し、基準信号源180と、電圧制御発振器110と、位相比較器120と、第1チャージポンプ130と、ループフィルタ150と、カウンタ161と、第2チャージポンプ170と、制御回路164とを備える。電圧制御発振器110は、第1信号、および逆相の第2信号を生成する。スイッチ140は、第1チャージポンプ130で生成された電流信号をループフィルタ150に供給する。カウンタ161は、基準信号の1周期期間に含まれる、第2信号のサイクル数をカウントする。第2チャージポンプ170は、互いに反対符号の第1電流信号と第2電流信号をループフィルタ150に供給可能である。制御回路164は、サイクル数とXの値との比較に基づき、スイッチ140および第2チャージポンプ170を制御する。

(もっと読む)

位相同期回路、CDR回路及び受信回路

【課題】基準クロックの周波数を低くして消費電力を抑制することのできる位相同期回路を提供する。

【解決手段】第1の位相比較器と第2の位相比較器とに、それぞれ帰還クロックの少なくとも1周期分異なる位相差をつけた分周クロックを入力して基準クロックとの位相比較を行い、受信信号と帰還クロックとの位相比較の結果で第1と第2の位相比較器の出力の重みづけを行い、重みづけされた出力により帰還クロックの位相調節を行う。

(もっと読む)

PLL周波数シンセサイザ、無線通信装置およびPLL周波数シンセサイザの制御方法

【課題】安価な構成とするとともに、性能を向上させることができるPLL周波数シンセサイザ、無線通信装置およびPLL周波数シンセサイザの制御方法を提供する。

【解決手段】PLL周波数シンセサイザは、基準周波数信号と分周信号との位相を比較する位相比較部101からの信号と位相誤差補償信号とに応じて、電流パルス信号を生成するCPDAC102と、電流パルス信号を電圧信号に変換するループフィルタ103と、電圧信号に応じた発振周波数の信号を出力するVCO104と、VCO104からの出力を分周して分周信号として出力する分周器105と、分数分周のための分周比のデータに基づいて、分周比制御信号を生成するデルタシグマ変調器107および加算器106と、分周比のデータから少なくとも2つの位相誤差補償用のデータを生成し、生成したデータを異なるタイミングで利用して、位相誤差補償信号を生成する制御部108とを備える。

(もっと読む)

位相ロックループ回路

【課題】簡素な回路構成で、電圧制御発振回路の入力部でのリークに起因する定常位相誤差を防止できる位相ロックループ回路を提供する。

【解決手段】リファレンスクロック信号とフィードバッククロック信号の位相差を検出する位相比較回路1と、検出された位相差に応じた電流を容量に出力するチャージポンプ回路2と、容量に蓄積されている電荷に基づく制御電圧に応じた発振周波数の出力クロック信号を生成する電圧制御発振回路4とを有する位相ロックループ回路にて、制御電圧がロック状態時の電圧であった場合に電圧制御発振回路4の入力部に流れるリーク電流に等しい電流を生成し、生成された電流に応じた補正電流をカレントミラー回路を介して容量に出力するようにして、リーク電流による制御電圧の変動を抑制する。

(もっと読む)

PLL回路

【課題】ロックアップタイムの高速化とリファレンスリークの低減化をとバランス良く達成する。

【解決手段】電圧制御発振器(104)の制御電圧VCONTをアナログ/デジタル変換して得られるデジタル信号(ADCO)を出力するアナログ/デジタル変換回路(106)と、基準クロック信号(FREF)と帰還クロック信号(FDIV)とがロックしたことを検出した時にロック検出信号(S201)を出力するロック検出部(201)と、ロック検出部からロック検出信号が入力された時にアナログ/デジタル変換回路から入力されたロック時デジタル信号を保持する保持部(107)と、保持部に保持されたロック時デジタル信号とアナログ/デジタル変換回路から出力されたデジタル信号との比較結果に基づいてチャージポンプ電流の電流量を段階的に減少させるチャージポンプ電流量制御信号(CPCONT)を生成するチャージポンプ制御部(108)と、を備えるPLL回路。

(もっと読む)

PLL回路、DLL回路

【課題】基準クロック信号と比較対象となるクロック信号の両者の位相を比較する位相比較器から位相差信号が出力され続けるPLL回路又はDLL回路にあって、両信号の同期を適切に検出して低ジッタ動作を実現する。

【解決手段】同期判定回路(15)は、基準クロック信号(R)の位相を基準として帰還クロック信号(V)の位相が進相又は遅相であるかを検出し、両信号の位相差の期間、進相検出信号(DOWN)又は遅相検出信号(UP)を出力する進相及び遅相検出部(158)と、進相検出信号(DOWN)が出力されている期間、初期値からの計数を開始する進相期間計数部(155)と、遅相検出信号UPが出力されている期間、初期値からの計数を開始する遅相期間計数部(156)と、進相期間計数部又は遅相期間計数部の計数値が第1の規定値に到達しない回数が第2の規定値を上回ったとき、位相同期検出信号(P_DET)を出力する位相同期判定部(157)と、を備える。

(もっと読む)

1 - 20 / 170

[ Back to top ]