Fターム[5J106HH08]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 制御量 (1,632) | 起動、停止 (35)

Fターム[5J106HH08]に分類される特許

1 - 20 / 35

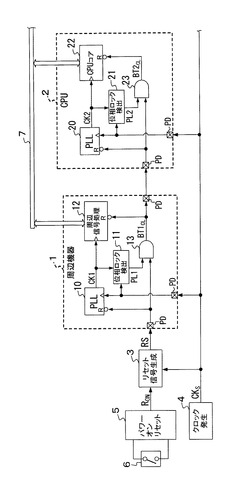

情報処理システム

【課題】システムリセット時の起動時間を短縮可能な情報処理システムを提供する。

【解決手段】複数の機能モジュールの内の機能モジュール1では、システムリセット信号にてPLL回路10及び信号処理部12をリセットした後にPLL回路10へのリセットを解除する。リセット解除後にPLL回路10で生成された内部クロック信号がシステムクロック信号に位相ロックしていない場合には起動中を示す第1の起動状態信号を機能モジュール2に供給する。位相ロックしている場合には起動完了を示す第2の起動状態信号を機能モジュール2に供給すると共に信号処理部12へのリセットを解除する。機能モジュール2では、第1の起動状態信号にてPLL回路20及び信号処理部22をリセットする。そして、第2の起動状態信号にてPLL回路20へのリセットを解除し、リセット解除後に、位相ロックした時に信号処理部22へのリセットを解除する。

(もっと読む)

半導体装置

【課題】入力信号と出力信号の位相差の増大を抑制すること。

【解決手段】本発明の半導体装置は、縦続接続された複数の遅延素子を用いて、入力信号と出力信号の位相を合致させるロック調整動作を行うDLL回路と、リファレンス電位を基準として生成した出力電圧を、複数の遅延素子に供給する遅延素子用電源回路と、出力電圧がリファレンス電位の一定範囲内にあるか否かを検出し、出力電圧が一定範囲内にない場合、ロック調整動作を停止させるDLL動作信号をDLL回路に出力する検出回路と、を有する。

(もっと読む)

半導体装置

【課題】再開トリガ信号を生成できないことによってリードデータの出力タイミングと外部クロック信号の同期が外れてしまうことを防止する。

【解決手段】DLL回路100には、当該DLL回路100を初期起動させるリセット信号RESETと、内部クロック信号LCLKの内部クロック信号ICLKに対する遅延量の制御を当該DLL回路100に再開させる再開トリガ信号RESTARTとが入力され、DLL回路100は、リセット信号RESET又は再開トリガ信号RESTARTが活性化されたことに応じて遅延量の制御を開始し、リセット信RESET号が活性化された後再開トリガ信号RESTARTが活性化される前には、当該DLL回路100のロック後にも遅延量の制御を継続し、再開トリガ信号RESTARTが活性化された後には、当該DLL回路100のロックに応じて遅延量の制御を停止する。

(もっと読む)

分周回路及び集積回路

【課題】分周器の発振を防止する分周回路を提供する。

【解決手段】クロック信号Vcを所定の分周比にて分周する分周器20を備え、分周器の発振を防止する分周回路1であって、クロック信号のピーク電圧Vcpを検出してピーク値を保持するピーク検出器30と、分周器が正常動作するために必要なクロック信号の振幅vpに対応した参照電圧Vrefを出力する参照電圧発生器40と、ピーク検出器により検出されたピーク値と参照電圧とを比較する比較器50と、を備え、分周器に分周開始を指示する制御信号を入力する制御端子を備え、制御端子に比較器の出力信号Veを接続し、ピーク値が参照電圧を超えたときに、比較器は、分周器の制御端子に分周開始を指示する制御信号を出力する

(もっと読む)

送信回路、集積回路装置及び電子機器

【課題】安定したデータ送信ができる送信回路、集積回路装置及び電子機器等を提供すること。

【解決手段】送信回路100は、電圧制御発振回路190を有し、搬送波の信号を生成するPLL回路110と、送信データDTXに基づいて、電圧制御発振回路190の変調用制御電圧信号入力ノードNBに対して、変調用制御電圧信号VMを出力する変調用制御電圧生成回路120と、電圧制御発振回路190の出力信号を増幅するパワーアンプ210とを含む。変調用制御電圧生成回路120は、送信データ出力期間の前の擬似信号出力期間に、擬似制御電圧信号を変調用制御電圧信号VMとして出力する。

(もっと読む)

水晶発振器

【課題】実装スペースとコストの更なる低減のため、電子機器内の水晶部品を1つに集約するためには、消費電流や周波数精度の問題があった。

【解決手段】本発明の水晶発振器は、音叉型水晶振動体と、この振動体の温度による発振周波数の変化を、時間領域で連続的に補正するための温度補償回路を含んだ発振回路とを備え、この発振回路の出力を源振として高周波クロック信号を出力する、複数のPLL(フェイズロックループ)回路を備える。このような構成にすることにより、電子機器内で必要とされる全てのクロック信号を、精度良く提供することができる。

(もっと読む)

原子発振器

【課題】τ秒平均時間の短い期間における短期安定度を向上させた原子発振器を提供する

。

【解決手段】周波数制御部2は、光検出器の出力信号をデジタル信号に変換するA/D変

換器12と、制御電圧を所定の周期又はデューティ比で間欠的に出力するタイミングを生

成するタイマ(制御周期生成手段)13と、タイマ13により生成されたタイミングに基

づいて出力された制御電圧Vcをアナログ電圧に変換するD/A変換器10と、タイマ1

3のタイミングに基づいて、パワーダウンする期間を指示した信号を出力するIO(パワ

ーダウン生成部)14と、全体の動作を制御するCPU11と、を備え、IO14は、少

なくとも周波数合成逓倍部4、又は/及び、原子共鳴部3をパワーダウンするように構成

されている。

(もっと読む)

ディスプレイ駆動装置

【課題】本発明は、ディスプレイ駆動装置に関する。

【解決手段】本発明はディスプレイ装置、特にディスプレイ装置に使用されるバックライトユニット駆動装置において、映像信号が正常である場合には映像信号の周波数に同期された周波数を有する駆動信号を提供し、映像信号が異常状態である場合には予め設定された周波数を有する駆動信号を提供して、安定的な動作を行うため、入力された映像信号の周波数と分周された駆動信号の周波数の差を検出する周波数検出部と、上記周波数検出部からの検出結果により、上記映像信号の周波数と同期された周波数を有する上記駆動信号を生成する駆動信号生成部と、上記周波数検出部からの上記検出結果が異常動作である場合、上記周波数検出部の周波数検出動作を停止させる制御部とを含むディスプレイ駆動装置を提供する。

(もっと読む)

クロック生成回路

【課題】ロングタームジッタを正確に評価し、回路の誤動作を未然に防ぐ。

【解決手段】第1オシレータ10は、基準クロックCKrefを生成する。PLL回路14は、第1オシレータ10からの基準クロックCKrefにもとづいて出力クロックCKoutを生成する。異常発振監視部20は、基準クロックCKrefを分岐して受け、基準クロックCKrefの周期の整数倍の所定時間経過後にアサートされる基準タイミング信号S1を生成する。異常発振監視部20は、出力クロックCKoutのエッジのタイミングが基準タイミング信号S1のエッジに応じて規定される所定の範囲から逸脱するとき、異常検出信号S2をアサートする。

(もっと読む)

発振回路、発振回路を備えた電子機器及び発振回路の制御方法

【課題】高精度発振器間の位相同期を間欠動作にすることにより低消費電力化する。

【解決手段】基準となる周波数の基準信号Frefを出力する周波数確度が高い高精度発振器100と、出力信号Foutの周波数を制御電圧Vcで制御する電圧制御発振器110と、基準信号Frefの位相と出力信号Foutの位相との位相差を検出し位相差信号Poを出力する位相比較部120と、位相差信号Poに基づき制御電圧Vcを生成する制御電圧生成部130と、位相比較部120への電源VDDの接続を接続状態または非接続状態に切り替えるスイッチ回路140と、位相差信号Poに基づき位相差が無くなった時点から所定の時間が経過するまでの期間はスイッチ回路140を接続状態にし、期間以外はスイッチ回路140を非接続状態にする制御信号Swを出力するタイマ回路150と、を含む発振回路1。

(もっと読む)

DLL回路、および半導体装置

【課題】DLLクロックが消失した場合に、位相検知における誤判定の結果を基に、遅延量が更新されることを回避し、ロック制御におけるDLLクロックサイクルの短縮化と、DLL回路の動作安定性の向上を図る。

【解決手段】本発明のDLL回路は、入力されるクロック信号の遅延量を制御する遅延信号を出力する遅延制御回路13と、この遅延信号に基づいた遅延量をクロック信号に付加し、DLLクロックとして出力する遅延回路12と、DLLクロック信号のクロッキング動作の有無を検知するDLLクロック検知回路31とを備える。そして、DLLクロック検知回路31は、DLLクロックのクロッキング動作が検知されない場合に、遅延制御回路13による遅延量の更新制御を停止させる。

(もっと読む)

リアルタイムクロック回路のバックアップ電源回路および半導体装置

【課題】二次電池を過充電することなく、負荷回路の正確な消費電流の測定を可能にする。

【解決手段】リアルタイムクロック回路11のバックアップ電源回路20において、主電源Vinにより充電されるバックアップ電源20と、主電源Vinと、リアルタイムクロック回路11の電源端子間に介挿された第1スイッチ手段SW1と、バックアップ電源20と、リアルタイムクロック回路11の電源端子間に介挿された第2スイッチ手段SW2と、主電源Vinの電圧を検出し、該電圧が第1検出電圧以下の場合には第1スイッチ手段SW1をオフする第1電圧検出回路12と、主電源Vinの電圧を検出し、該電圧が第2検出電圧以上の場合には前記第2スイッチ手段SW2をオフする第2電圧検出回路13を備える。

(もっと読む)

起動制御回路付き水晶発振回路および位相同期回路

【課題】 水晶発振回路が定常発振に達するまでの起動時間を短くすることができる起動制御回路付き水晶発振回路、水晶発振回路の起動時間を短くすることで間欠動作の比率を大きくし、低消費電力化に寄与する位相同期回路を実現する。

る。

【解決手段】 水晶振動子と負性抵抗回路を備えた水晶発振回路の起動制御を行う起動制御回路を含み、一定の発振周波数の信号を出力させる起動制御回路付き水晶発振回路であって、水晶発振回路は、水晶振動子を励振する励振信号を外部から入力するための信号入力端子を備え、起動制御回路は、発振周波数またはそれに近い周波数を有する励振信号を生成し、水晶発振回路の起動時に励振信号を励振信号入力端子に入力し、水晶発振回路の発振周波数が安定する前に励振信号の入力を停止する構成である。

(もっと読む)

DLL回路およびその制御方法

【課題】より迅速な固定完了時間を有し、半導体集積回路の高速化実現をより効率的に支援するDLL回路およびその制御方法を提供する。

【解決手段】本発明のDLL(Delay Locked Loop)回路は、基準クロックと動作開始信号に応答して初期動作信号を生成する初期動作設定手段と、前記初期動作信号、位相比較信号、および初期設定コードに応答して遅延制御コードを生成するシフトレジスタと、前記初期動作信号および前記遅延制御コードに応答して前記基準クロックまたはフィードバッククロックを遅延させ、複数の単位遅延クロックを生成する遅延ラインと、前記基準クロックと前記複数の単位遅延クロックに応答して前記初期設定コードを生成する初期遅延モニタリング手段とを含むことを特徴とする。

(もっと読む)

低消費電力装置を有するタイヤ圧検出器

タイヤ圧検出器は、集積回路に外付けされるように構成されるパワーアンプと、入力データストリームの論理状態に応じて動作するVCOを有するPLL回路とを備える低消費電力装置を用いる。入力データストリームは、タイヤ圧力情報を有し、複数の論理状態を有するようにエンコードされるように構成される。入力データストリームの各データビットのパターンに応じて、所定の期間、VCO及び/又はアンプをターンオン及びターンオフすると、マイクロコントローラがVCOを制御するために用いられる。このタイヤ圧検出器は、電力効率に関して最適化された回路配置をこのようにして具現化する。  (もっと読む)

(もっと読む)

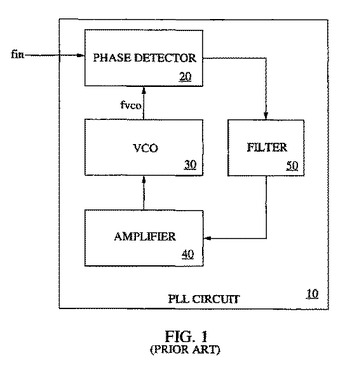

PLL回路

【課題】この発明は、PLL回路に関し、プロセス、温度、電源電圧等の変動に合わせた回路の制御を行い、ロックイン時間を短縮させる事を目的とする。

【解決手段】ループに接続された位相検出器1、チャージポンプ2、ループフィルタ3、電圧制御発振器4を備えた本発明のPLL回路は、チャージポンプ2と並列動作可能な加速用チャージポンプ7、加速用チャージポンプ7の動作タイミングを制御する制御手段5を備えて構成される。

(もっと読む)

データ通信システムの高速パワーアップ

データ通信システムは、第1のクロック発生回路を有する送信機と、第2のクロック発生回路を有する受信機とを具えている。第1及び第2のクロック発生回路のうちの少なくとも一方の特定のクロック発生回路が順次のデータバースト間でパワーダウンされるようになっている。このデータ通信システムは、前記特定のクロック発生回路がパワーダウンした際にこのデータ通信システムを実用使用状態に起動するのを促進させる。このデータ通信システムは、起動時に前記特定のクロック発生回路の動作量を予め決定した値にプリセットする。  (もっと読む)

(もっと読む)

自動周波数制御回路

【課題】 自動周波数制御回路における検出部の起動および停止を簡単に制御し、消費電力を低減する。

【解決手段】 受信パケットから送信装置と受信装置との間のクロック周波数の誤差を検出し、その周波数誤差に対する補正値を出力する検出部と、検出部から出力された補正値に基づいて受信パケットの周波数誤差を補正する補正部とを備えた自動周波数制御回路において、検出部とは別のアルゴリズムで、受信パケットの周波数誤差の有無を簡易に判定し、周波数誤差があれば検出部を動作させ、周波数誤差がなければ検出部の動作を停止させ、検出部の動作時に出力した補正値を受信パケットの周波数誤差の補正に用いる制御を行う簡易判定部を備える。

(もっと読む)

撮像装置

【課題】サンプルホールドタイミングを高精度に決定しながらも消費電力を抑えることが可能な撮像装置を提供する。

【解決手段】撮像素子と、撮像素子から出力される撮像信号OSに相関二重サンプリング処理等を行うAFEとを有するデジタルカメラであって、DLL回路40と、AFEを制御するための制御信号(サンプルホールドタイミングパルスshp)をDLL回路40から出力されるクロックpulseに基づいて生成するパルス発生回路と、ブランキング期間中、DLL回路40を、そのロック状態を維持させたまま停止させる制御を行うDLL制御部51とを備える。

(もっと読む)

半導体集積回路

【課題】本発明は、Ser/Des回路において、休眠ステートからパワーアップの状態へ遷移した際の受信エラーを減少できるようにする。

【解決手段】たとえば、受信機21が、休眠ステートP1からパワーアップの状態P0に遷移したとする。すると、リセット制御回路21mは、ディレイ回路21m-1によって、PLL31からのシステムクロックのカウントを開始する。そして、ディレイ回路21m-1がXサイクルをカウントした後に、リセット制御回路21mは、ディジタルフィルタ21eおよびPI制御回路21fのリセットを解除するように構成されている。

(もっと読む)

1 - 20 / 35

[ Back to top ]