Fターム[5J106KK38]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 目的、効果 (3,441) | 小型化 (224)

Fターム[5J106KK38]に分類される特許

141 - 160 / 224

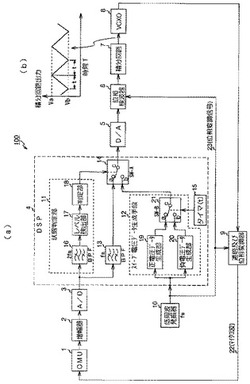

ルビジウム原子発振器

【課題】スイープ電圧発生のための回路規模を小型化し、且つ非ロック時における周波数引き込み動作を自動的に行なうことが可能なルビジウム原子発振器を提供する。

【解決手段】このルビジウム原子発振器100は、OMU1と、増幅器2と、出力信号をデジタル信号に変換するA/D変換器3と、ロック状態又は非ロック状態を判定する状態判定部11と、位相変調信号fmの周波数成分を選択的に出力するBPF13と、スイープ電圧データを生成するスイープ電圧データ生成手段12と、タイマ15と、第1のBPF13の出力信号又はスイープ電圧データ生成手段12の出力信号を選択するSW−A14と、アナログ信号に変換するD/A変換器5と、位相検波して周波数制御信号を生成する位相検波器6と、周波数制御信号を積分処理する積分回路7と、周波数制御信号に従い出力周波数が制御されるVCXO8と、を備えて構成されている。

(もっと読む)

タイムトゥデジタルコンバータ

【課題】タイムトゥデジタルコンバータを提供する。

【解決手段】タイムトゥデジタルコンバータは、高い解像度と広い測定範囲のために低解像度タイムトゥデジタルコンバータと高解像度タイムトゥデジタルコンバータとを含む。低解像度タイムトゥデジタルコンバータは、第1信号と第2信号との時間差を第1量子化間隔で測定する。高解像度タイムトゥデジタルコンバータは、第1信号と第2信号との時間差を第1量子化間隔よい更に小さい第2量子化間隔で測定する。低解像度タイムトゥデジタルコンバータは、高解像度タイムトゥデジタルコンバータより広い測定範囲を有する。

(もっと読む)

電圧制御発振回路およびPLL回路

【課題】出力クロックの変動を抑えることができる電圧制御発振回路およびPLL回路を提供する。

【解決手段】この電圧制御発振回路によれば、第2の電源生成回路1−2が出力するゲート制御信号103,104によって、一部の反転回路10−nの遅延時間を変更制御するが、残りの反転回路10−1〜10−(n−1)の遅延時間は第1の電源生成回路1−1によって一定に制御する。したがって、第2の電源生成回路1−2が制御する電源電圧103−n,104−nが変化(変動)しても出力クロック100の周波数の変化(変動)は従来のように全ての反転回路の遅延時間を変更制御する場合に比べて小さい。

(もっと読む)

DLL回路

【課題】 クロックの立ち上がり及び立ち下がりに同期した内部クロックを生成するDLL回路においては、高精度が要求されることから回路規模が大きくなるという問題がある。

【解決手段】 Rise用の遅延調整回路とFall用の遅延調整回路を備え、Fall用の遅延調整回路にはRise用の遅延調整回路でRise側を調整したクロックを入力する。入力されるクロックのRise側が調整されていることから、Fall側の遅延差は非常に小さくなる。そのため、Fall用の遅延調整回路、カウンタの回路規模が大幅に削減できる。その結果少ない回路規模で、高精度のDLL回路が得られる。

(もっと読む)

周波数比較器、周波数合成器及び関連方法

【課題】電圧に基づいて内部周波数を設定し、これを外部周波数と比較するアナログ周波数比較器と、アナログ周波数比較器の同じ原理でクロック信号を合成するアナログ周波数合成器、及び関連の方法を提供する。

【解決手段】周波数比較器は、第一信号と入力電圧に基づいて基準信号を生成する周波数検出回路と、該入力電圧に基づいて第二信号を生成する周波数発生器と、周波数検出回路と周波数発生器に結合され、基準信号と第二信号の一方に基づいて充電電流をイネーブルして電圧レベルを上げ、更に基準信号と第二信号のもう一方に基づいて放電電流をイネーブルして電圧レベルを下げる電荷ポンプ回路と、電荷ポンプ回路に結合され、該電圧レベルに基づいて第一信号と第二信号間の周波数関係を示す決定論理とを含む。

(もっと読む)

位相比較信号処理回路

【課題】位相比較回路の出力矩形波信号の処理する際に、簡単な回路構成を有し、PLLで引込み可能な周波数幅を拡げ、同期時間を短縮できる位相比較信号処理回路を提供する。

【解決手段】入力矩形波信号を双極性信号に変換する電圧シフタ2、入力矩形波信号のレベル変化時に制御パルス信号を発生する制御パルス信号発生器7、制御パルス信号の到来時に積分値をリセットし、その後双極性信号を積分して積分値を出力する積分回路3、積分値のリセット時のレベル変化分を微分パルスとして出力する微分回路4、制御パルス信号の到来時に微分パルスを出力するゲート回路6、前記保持回路は最新の入力微分パルスレベルを保持し、微分パルスレベルの更新時にその微分パルスレベルが保持されるように保持電圧値が順次変化する保持信号を形成するホールド回路8を備え、この保持信号を次段のループフィルタに供給する。

(もっと読む)

位相調整回路及びフェイズロックドループ回路

【課題】周波数の高いクロックを用いる事無く、小さな回路規模で実現でき、より細かい分解能で位相調整することができる位相調整回路及びフェイズロックドループ回路を提供する。

【解決手段】入力される水平同期信号SYNC_INは、位相シフト回路21により位相調整データCKPHASEの上位2Bitsの値に応じてシフトされ、その出力によりアップダウンカウンタ22はクロックNCKPをアップ及びダウンカウントして、逓倍回路32等経てラッチ回路23に出力し、ラッチ回路23は、データイネーブル用パルスENCKPによりラッチして、位相調整出力HD_SIGを出力する。

(もっと読む)

PLL回路

【課題】従来のPLL回路は、ループフィルタにかかるコンデンサの回路面積が回路面積全体に占める割合が大きい問題があった。

【解決手段】本発明にかかるPLL回路は、位相比較器12の出力信号に応じて出力電流を制御する第1のチャージポンプ回路13と、第1のチャージポンプ回路13が出力する電流に基づき発生する電圧信号から所定の周波数成分を除去する積分フィルタ14と、位相比較器12の出力信号に応じて第1のチャージポンプ回路13より大きな電流を出力し、当該電流を制御する第2のチャージポンプ回路16と、第2のチャージポンプ回路16が出力する電流に基づき発生する電圧信号からリップル成分を除去するリップルフィルタ17とを備え、積分フィルタ14の出力電圧に応じた電流とリップルフィルタ17の出力電圧に応じた電流との合計値に基づき出力信号の発振周波数を制御するものである。

(もっと読む)

周波数比較回路、PLL周波数シンセサイザテスト回路及びそのテスト方法

【課題】周波数比較回路を少ない素子数で構成できるようにすると共に、第1、第2の信号(例えば、NCLK信号およびMCLK信号)の周波数が一致しているか否かを正しく判定できるようにした周波数比較回路、PLL周波数シンセサイザテスト回路及びそのテスト方法を提供する。

【解決手段】NCLK信号の立ち上がりもしくは立ち下がりのエッジを検出し、基準クロックで同期化されたUP信号を生成するエッジ検出回路111aと、MCLK信号の立ち上がりもしくは立ち下がりのエッジを検出し、基準クロックで同期化されたDown信号を生成するエッジ検出回路111bと、UP信号及びDown信号をカウントし、そのカウント値をQ1、Q0信号で出力する2ビットアップダウンカウンタ112と、Q1、Q0信号に基づいて、NCLK信号の周波数とMCLK信号の周波数とが一致しているか否かを判定する判定回路113と、を有する。

(もっと読む)

集積回路、表示装置及びそれを用いた電子機器

【課題】DLLに求められる保証動作周波数帯域を低め、基準クロック信号が二逓倍された周波数をそれぞれ有し、位相差のある2つのクロック信号を生成することができる集積回路、表示装置及び電子機器を提供する。

【解決手段】タイミングコントロールICは、一周期Tの基準クロック信号ICLKと同一周波数の第1〜第4のクロック信号CLK1〜CLK4であって、第N(N=1,3のいずれか)のクロック信号に対する第(N+1)のクロック信号の位相遅れが位相差T/4で、かつCLK1に対するCLK3の位相遅れが位相差α(0<α<T/4)であるCLK1〜CLK4のクロック信号を発生させるDLL40と、CLK1が二逓倍されたデータ生成用のCLK5を生成し、かつ、CLK3が二逓倍されて、CLK5に基づき生成されデータ信号に対して位相差αの遅れで同期したCLK6を生成する二逓倍回路50とを有する。

(もっと読む)

インピーダンス回路およびこれを用いた信号生成回路

【課題】基準周波数を得る場合、安定した周波数、もしくは遅延要素を得る回路を提供する。

【解決手段】第1の温度変動率を持つ第1のインピーダンス回路1と第1の能動回路3で構成した第1の発振回路6と、第1の温度変動率とは逆の変動方向となる第2の温度変動率を持つ第2のインピーダンス回路2と第2の能動回路4で構成した第2の発振回路7との出力を時系列的に交互に切替器5で選択する。第1のインピーダンス回路1の温度係数の絶対値が第2のインピーダンス回路2の温度係数より大きいとき、第1の発振回路6の使用時間を短くし、温度係数の小さい第2の発振回路7の使用時間を長く動作させるように、温度係数の比と逆の比率で発振回路の使用時間の比率を設定する。温度変動方向が逆の2つの温度係数を有することから、平均値として温度変動がほぼなく軽減される。時間平均値として温度変動が極めて小さく温度変動率の改善された発振周波数を得る。

(もっと読む)

光ディスク装置のPLL回路

【課題】回路規模や消費電力の増加を抑えつつ、充分な性能を有するウオブルPLLを構成する。

【解決手段】ウオブリングされたトラックを有する光ディスク1の反射光に基づいてウオブリング信号を検出するウオブル検出器と、入力に応じて出力の発振周波数が変化するVCO10とを有し、ウオブリング信号出力とVCO10の出力との位相誤差により、VCOを制御する光ディスク装置のPLLにおいて、ウオブリング信号を所定のクロックでデルタシグマ変調する変調器7と、変調器出力とVCOの出力とをクロックで演算する演算器8と、演算器8の出力の低域成分だけを通過させるロー・パス・フィルタ9と、を有し、ロー・パス・フィルタ9の出力に基づいて、VCO10を制御する。

(もっと読む)

半導体集積回路装置およびそのテスト方法

【課題】PLL回路のテスト回路のチップ面積を小さくする。

【解決手段】分周器PSのテスト時に、バランT1を介してテスト制御電圧信号TCおよびRFテスト信号TSが入力端子IN1、IN2に供給される。テスト制御電圧信号TCは、抵抗R1、R2を流れ、NPNトランジスタQ0がオンとなることで、電圧制御発振器V1およびバッファB10は、電流源I1からの電流が供給されず動作を停止し、バッファB10の出力インピーダンスは高くなる。入力端子IN1、IN2の電位は、テスト制御電圧信号TCの電位にあるので、バラクタダイオードVD1、VD2は、順バイアス状態となって、容量値がより大きくなる。RFテスト信号TSは、出力インピーダンスの高いバッファB10の影響を受けることなく、バラクタダイオードVD1、VD2を介して分周器PSに入力される。

(もっと読む)

原子発振器及び原子発振器の温度制御方法

【課題】ランプ保持部材とガスセル保持部材の間にサーモモジュールを挟み、ランプ保持

部材とガスセル保持部材間の温度差を適切になるようにサーモモジュールを制御すること

により、ルビジウムガスセルとルビジウムランプ間の熱の影響を低減すると共に、光学系

を小型化することができる原子発振器を提供する。

【解決手段】この光学系100は、ルビジウム原子を封入したガスセルを保持するガスセ

ル保持部材4と、ガスセル中のルビジウム原子を励起するルビジウムランプを保持するラ

ンプ保持部材2と、ガスセル保持部材4を加熱するガスセルヒータ5と、ランプ保持部材

2を加熱するランプヒータ1と、熱エネルギと電気エネルギの直接相互交換による熱電効

果により対向面に温度差を生ずるサーモモジュール3と、電流の大小及び極性により対向

面に生じる温度差の大小と向きを制御する温度制御部7と、を備えて構成される。

(もっと読む)

チャージポンプ回路及び位相同期ループ回路

【課題】回路規模や消費電流の増大を抑えつつ、スプリアス成分を十分に抑制できるチャージポンプ回路とこれを備えたPLL回路を提供する。

【解決手段】第1駆動信号Supとその複数の遅延信号に応じて複数の電流が生成されて共通のノードN1へ流出し、第2駆動信号Sdnとその複数の遅延信号に応じて複数の電流が生成されて共通のノードN2から流入する。これにより、チャージポンプ回路自体に櫛型フィルタとしての機能を併せ持たせる。

(もっと読む)

位相同期ループ回路、半導体集積回路、および、受信装置

【課題】使用する電圧制御発振器の選択、および、その発振周波数範囲の設定をより効率的に行うことができる位相同期ループ回路を実現する。

【解決手段】位相同期ループ回路100の制御部103は、位相同期ループ回路100に接続する電圧制御発振器として、複数の電圧制御発振器VCO1〜VCOnのうちから、選局周波数を含む主発振周波数範囲をもつ電圧制御発振器を選択し、その後、選択された電圧制御発振器の発振周波数範囲を、選局周波数を含む副発振周波数範囲に設定する。

(もっと読む)

信号受信装置

【課題】小型化および低消費電力化が可能な信号受信装置を提供する。

【解決手段】本発明の信号受信装置は、N個の信号受信ブロック(Nは2以上の整数)を備え、N組のシリアル信号とサイクル数がそれぞれ等しいN個のクロックとを受信する。第1の信号受信ブロックは、第1のクロックと第1の内部クロックとの位相差を表す位相差信号を生成する位相差検出回路と、位相差信号の値に応じて第1のクロックの位相を遅延させた第1の内部クロックを生成する第1の位相遅延回路と、第1の内部クロックに基づいて第1組のシリアル信号を変換するシリアル−パラレル変換回路とを有する。他の第nの信号受信ブロックは、第1の信号受信ブロックからの位相差信号の値に応じて第nのクロックの位相を遅延させた第nの内部クロックを生成する第nの位相遅延回路と、第nの内部クロックに基づいて第n組のシリアル信号を変換するシリアル−パラレル変換回路とを有する。

(もっと読む)

ルビジウム原子発振器

【課題】放射用アンテナとルビジウム金属溜まり部の位置関係を適正化することにより、

マイクロ波共振器を小型化する際に生じる共振特性の悪化を抑制することができるルビジ

ウム原子発振器を提供する。

【解決手段】このマイクロ波共振器3は、ルビジウムガスを内部に保持すると共に、所定

の温度に維持する円筒状のガスセル熱筒30と、ガスセル熱筒30の円筒内の長さを調整

して同調周波数を調整する同調調整用リング21と、ルビジウムガスを充填し、気化し切

れないルビジウム金属を貯留する金属溜まり部23を備えた円筒状のRbガスセル6と、

マイクロ波を放射する放射用アンテナ4と、マイクロ波の強度を測定するために備えられ

た受信用アンテナ2と、Rbガスセル6を透過した光の強度を検出するフォトセンサ7と

、共振波長を短縮する誘電体22と、を備えて構成されている。

(もっと読む)

電圧制御発振器

【課題】部品点数を削減し、回路規模を低減させることが可能な電圧制御発振器を提供すること。

【解決手段】本発明にかかる電圧制御発振器は、発振回路(2)と、複数の共振回路(5,6)と、前記複数の共振回路のいずれか1つを選択的に前記発振回路と接続させる切り替え手段(4)と、を備える。ここで、各共振回路は、例えば、所定の共振周波数に対応するLC共振回路と当該共振周波数を制御する可変容量ダイオードと、を含んで構成される。

(もっと読む)

PLL回路

【課題】スプリアスの影響がなく追加される回路規模の小さい、ロックアップタイムの短縮されたPLL回路を提供する。

【解決手段】位相比較回路によって検出された位相差信号は外部トリガにより切断されるスイッチ1を備えたチャージポンプに接続し、チャージポンプの出力は、ローパスフィルタを経由して外部トリガにより切断されるスイッチ2を経由して電圧制御発振回路を駆動し、さらにチャージポンプの出力は電圧ホロワに入力され、電圧ホロワは外部トリガにより接続されるスイッチ3を経由して電圧制御発振回路を駆動し、分周期は初期化端子を備え帰還信号を出力し、フリップフロップ回路の出力が分周器の初期化端子に接続され、フリップフロップ回路は、外部トリガが入力されないときは基準信号によって分周器の初期化が解除されその状態を保ち、外部トリガが入力されたときは基準信号によって初期化されその状態を保つ信号を出力することを特徴とする。

(もっと読む)

141 - 160 / 224

[ Back to top ]