Fターム[5J106KK38]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 目的、効果 (3,441) | 小型化 (224)

Fターム[5J106KK38]に分類される特許

201 - 220 / 224

PLL変調器、通信機器、及び移動無線機

【課題】 アナログフィルタを除去してもノイズを除去できるような構成にすることにより、広帯域変調が可能なPLL変調器を小型かつ低コストで提供する。

【解決手段】 PLL変調器は、分周器4に分周比変調をかける第1の変調ルートと、VCOに直接変調をかける第2の変調ルートとの2点変調を行う。第2の変調ルートにおいて、D/A変換器6の前段にループフィルタ2の逆周波数特性を有するプリエンファシスフィルタ7を設ける。これにより変調信号の帯域幅が制限されないようにする。さらに、D/A変換器6からの変調信号S10をPLL部10におけるループフィルタ2の前段の加算器9へ印加する。これにより、D/A変換器6で発生するノイズをループフィルタ2で抑圧した変調信号S3をVCO3へ供給する。この構成により、D/A変換器6の後段のアナログフィルタを除去し、ディジタルのプリエンファシスフィルタを設置できる。

(もっと読む)

発振器、集積回路、通信装置

【課題】 良好な位相ノイズを有しつつ回路面積を抑えた発振器(例えば、局部発振器)を提供する。

【解決手段】 制御電圧に応じてその発振周波数が下限値および上限値間で変化する電圧制御発振回路を複数有するとともにこの複数の電圧制御発振回路から任意の電圧制御発振回路を選択する選択手段を備えた発振器であって、2つ以上の上記電圧制御発振回路においては、上限値および下限値の差と、下限値および上限値の中間値との比率が互いに異なっている。

(もっと読む)

ディジタルPLL回路

周波数比較器は、基準クロックおよび出力クロックの周波数を比較し、周波数比較信号を出力する。周波数可変回路は、直列接続された複数の反転回路を有する遅延回路と第1選択回路とから構成される。第1選択回路は、奇数番目の反転回路から出力される奇数出力信号のいずれかを周波数比較信号に応じて選択し、帰還信号として遅延回路の入力に帰還させる。位相比較器は、基準クロックおよび出力クロックの位相を比較し、位相比較信号を出力する。第2選択回路は、奇数出力信号のいずれかを位相比較信号に応じて選択し、出力クロックとして出力する。周波数可変回路は、帰還ループを構成する反転回路の接続段数を調整することで、出力クロックの周波数を変更する可変発振器として機能する。遅延回路は、出力クロックの周波数調整および位相調整の両方に共通して用いられる。このため、回路規模を低減できる。  (もっと読む)

(もっと読む)

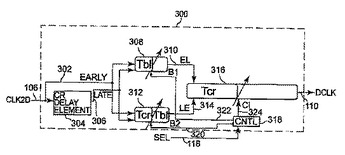

ブレンダー遅延を2つ用いた可変遅延線

可変遅延線は、第1の信号を供給するように構成された第1のブレンダー遅延と、この第1の信号に相補的な第2の信号を供給するように構成された第2のブレンダー遅延と、偶数番号の粗遅延素子が選択された場合には上記第1の信号を遅延し、奇数番号の粗遅延素子が選択された場合には上記第2の信号を遅延するように構成された粗遅延とを有する。  (もっと読む)

(もっと読む)

PLL回路、受信チューナ、通信機器、PLL回路のロック検出方法

【課題】本発明は、小型かつ低雑音でありながら、そのロック/アンロックを検出して高精度のフィードバックループ制御を行うことが可能なPLL回路の提供を目的とする。

【解決手段】本発明に係るPLL回路1は、基準信号発生器11と、分周器12と、位相比較器13と、チャージポンプ14と、ループフィルタ15と、VCO16と、PLLがロック状態であるか否かを検出するロック検出器17と、を有して成るPLL回路であって、チャージポンプ14は、入力される位相差信号に応じてその駆動電流が変動する構成とされており、ロック検出器17は、チャージポンプ14の駆動電流変動を検出してPLLがロック状態であるか否かを検出する構成とされている。

(もっと読む)

発振周波数制御回路

【課題】小型で設計や調整が容易な発振周波数制御回路を提供すること。

【解決手段】入力されるアナログ制御電圧に応じた周波数の発振信号を生成する発振回路から出力される、発振信号の周波数を計数する周波数カウンタと、入力されるデジタル値に応じて前記アナログ制御電圧を生成する複数のD/Aコンバータと、入力される制御信号に応じたデジタル値を生成するデジタル値生成回路と、周波数カウンタにより計数される周波数を基準の周波数と比較して、比較の結果に応じて前記デジタル値生成回路に入力する制御信号を生成する演算回路とを備える発振周波数制御回路を提供する。

(もっと読む)

位相比較器

【課題】比較演算に係る論理回路の回路規模を削減し、その結果、その回路面積を縮小し、遅延時間を短縮し、消費電力を低減することができる位相比較器を提供する。

【解決手段】位相比較器は、データとデータのハーフレートの位相が90°ずつずれた4相の第1〜第4のクロックとの間の位相を比較するもので、データを4相の第1〜第4のクロックで各々サンプリングする第1〜第4のサンプリング回路と、第1および第2のサンプリング回路によって、その位相が隣接する2相の第1および第2のクロックで各々サンプリングされた2つのデータ同士を比較し、両者が異なる場合に第1のアップ信号を出力する第1の比較回路と、第4および第1のサンプリング回路によって、その位相が隣接する2相の第4および第1のクロックで各々サンプリングされた2つのデータ同士を比較し、両者が異なる場合に第1のダウン信号を出力する第2の比較回路とを備える。

(もっと読む)

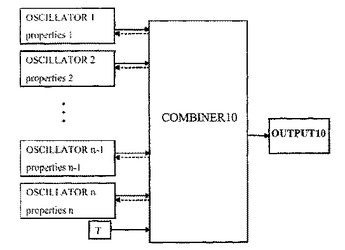

広帯域周波数を発振する装置および方法

図5に示すような、位相ロックループと可変周波数分割器(560)とを備えた、周波数を発振する装置が示されている。可変周波数分割器(560)は、第1の周波数の信号をある分割比で分割して第2の周波数(Fout)の信号を発生し、この周波数分割は、位相/周波数検出器(510)へ入力される参照周波数クロック入力(Fref)とフィードバック周波数の信号入力との比較に基づいて行われる。チャージポンプ(520)およびループフィルタ(530)が、第2の周波数の信号(355)を分割して正しいフィードバック周波数の実現を可能にする分割器(550)とともに示されている。VCO(540)には、選択されるキャパシタを備える共振回路と、動作周波数を設定する制御電圧と、適当な利得のための能動回路(320)とが内在する。  (もっと読む)

(もっと読む)

遅延ロックループ回路

【課題】基準クロック信号/クロック信号間の位相を合致させるように位相制御の遅延ロックループ(DLL)回路で、回路規模縮小化、低消費電力化を図かった、電圧制御可変遅延線(VCDL)を使用するアナログDLL回路を提供

【解決手段】イニシャル信号入力により第1のクロック信号の初期位相設定を行う遅延ロックループ回路で、基準クロック信号位相と第1のクロック信号位相の比較結果に応じた信号を出力の位相比較器と、イニシャル信号入力時に位相比較器出力信号に応じた選択信号を発生の初期位相差検出器と、イニシャル信号入力時に初期位相差検出器からの選択信号で位相が異なる第2のクロック信号中の基準クロック信号に最近接位相の第2のクロックを選択し、第3のクロック信号として出力の初期位相差設定回路と、第3のクロック信号に位相比較器からの信号に応じた位相遅延を付加の第1のクロック信号を出力の電圧制御可変遅延線とを備える遅延ロックループ回路を提供。

(もっと読む)

クォターレートクロック復元回路、及びクロック復元方法

【課題】 受信データレートの4分の1の周波数を有するクロックとして動作しかつ、四つの位相補間器を用いるクロックデータ復元回路を提供する。

【解決手段】 受信データレートの4分の1の周波数で0°、90°、180°および270°の位相差を有する第1クロック乃至第4クロックを生成するクロック生成部360と、制御信号に基づいて前記第1クロック乃至第4クロックを位相補間して受信データレートの4分の1の周波数で受信データの位相を追従する0°、45°、90°および135°の位相差を有する第5クロック乃至第8クロックを生成する位相補間部350と、受信データと前記第5クロック乃至第8クロックとの位相差に対応する信号を出力する位相検出部310と、位相検出部の出力信号を受信して位相補間部を制御するための制御信号を生成する位相補間部制御回路320とを含む。

(もっと読む)

容量性チャージ・ポンプ

容量性チャージ・ポンプ(111)は、例えばフェーズ・ロックド・ループ(PLL)(105)のようなデバイスに用いることが可能である。チャージ・ポンプは少なくとも一つのキャパシタ(211,217)を充電経路及び放電経路に含み、PLLのフィルタ・キャパシタ(115)に供給される、もしくはフィルタ・キャパシタから排出される電荷の量を制限する。一つの実施例では、第2キャパシタ(511,513)を充電経路または放電経路に設けて容量を小さくすることにより(直列に設けられる場合)、もしくは容量を大きくすることにより(並列に設けられる場合)、フィルタ・キャパシタに移動させる電荷の最大量を調整する。一つの実施例では、複数の容量回路を並列に設けてフィルタ・キャパシタに移動させる電荷の最大量を大きくする。各回路は、前段の回路が有効にされた時点から遅延期間が経過した後に有効にされる。  (もっと読む)

(もっと読む)

PLL回路を内蔵する半導体集積回路

【課題】 発振回路と位相比較回路とチャージポンプ回路とループフィルタを含むPLL回路において、複数の容量素子を設けることなくつまり占有面積をそれほど増大させることなくPLLの特性を抵抗素子や容量素子の製造ばらつきに応じて調整することができ、それによってループフィルタをオンチップ化できるようにする。

【解決手段】 ループフィルタ(17)を構成する抵抗素子と容量素子を半導体チップに形成しこのうち抵抗素子は抵抗値の異なる複数の素子を設けてスイッチにより切り替えることで抵抗値を調整可能に構成し、またチャージポンプ回路(16)の電流も調整可能に構成し、抵抗素子の抵抗値の切り替えに応じてチャージポンプ回路の電流を調整するようにした。

(もっと読む)

通信用半導体集積回路

【課題】 使用周波数帯を決定するまでに要する時間が長くならないとともに回路の占有面積を小さくすることができ、また、リセット信号等の遅延により誤った周波数帯が選択されない自動バンド選択回路を備えたPLL回路を内蔵した高周波ICを提供する。

【解決手段】 VCO11の発振周波数を制御するPLLループにおいて、所定の周波数の基準信号に対する可変分周回路12の出力の位相の進みまたは遅れを判別する判別回路22と、該判別回路の出力に基づいてVCOの周波数帯を切り替える信号を生成する自動バンド選択回路20と、信号の遅延に基づく位相判別におけるずれを測定しそれを補償するような遅延を固定分周回路14で分周された信号に与える遅延補償回路25とを設け、2分探査方式でVCOの周波数帯を切り替えながら最適な周波数帯を見つけて使用周波数帯を決定するようにした。

(もっと読む)

インテグレーテッドPLLを備えたPWMコントローラ

位相ロックループ(PLL)を用いた電子部品に電力を供給するためのパルス幅変調(PWM)コントローラが、提供される。PWMコントローラは、基準信号を受信する入力ノードと、位相ロックループ(PLL)とを備えている。このPLLは、誤り訂正信号を受信し且つ前記誤り訂正信号に関係する周波数を有する発振器信号を生成する発振器と、前記発振器に結合され、前記基準信号を受信し、且つ前記基準信号と、フィードバック信号との間の位相差に基づいて誤り訂正信号を生成させる位相周波数検出器(PFD)と、前記PFDに結合され、周期的にPFDが誤り訂正信号を生成することができるようにする抑制回路とを備えている。  (もっと読む)

(もっと読む)

スイッチトキャパシタフィルタ及びフィードバックシステム

ループフィルタ(30)は、電流信号の入力端と基準電圧との間に設けられた第1の容量素子(31)と、上記入力端と第1の容量素子(31)との間に設けられたスイッチトキャパシタ回路(32)と、第1の容量素子(31)及び前記スイッチトキャパシタ回路(32)に並列に設けられた第2の容量素子(33)とを備えている。スイッチトキャパシタ回路(32)において、第3の容量素子(321)が第1の容量素子(31)側に接続されるとき、第4の容量素子(322)は第2の容量素子(33)側に接続される。上記構成のループフィルタ(30)において、第2の容量素子(33)の容量値を、第3及び第4の容量素子(321,322)の容量値よりも大きく設定する。 (もっと読む)

周波数分割器を有する装置

セクション(21−27)を有する周波数分割器(2)は、調整信号(p,,)に依存して、かつ、後のセクションから生じる制御信号(c,,)に依存して、調整可能な数によって、周波数信号(f,,)を分割する第1種の基本セクション(21、22、23)を備えており、付加的な回路55、56、64、66、67を有する第2種の高度なセクション(22)を備えている。この付加的な回路55、56、64、66、67は、限られた数の早いセクションに対して実施されるべき何らかの変調を可能にし、後のセクションは影響を受けない。結果として、周波数分割器(2)は、例えば、いかなる変調も適応化される必要なしに、アクティブ及び非アクティブモードを有するプログラム可能なセクション(26、27)によって拡張されることができる。これに対し、回路55、56、64、66、67は、変調信号(mo、ml)及び付加的な制御信号(c3)を受け取る。前記のような周波数分割器(2)は、コストが低く、信頼でき、ロバスト性を有し、容易に実施化されることができる。  (もっと読む)

(もっと読む)

サブμ技術に適したデジタル位相同期回路

本発明は、デジタル制御発振器(4)と、位相検出器(11、12、13)と、デジタルループフィルタ(14)とを含む、デジタル位相同期回路に関するものである。上記デジタル制御発振器(4)は、出力周波数を生成するためのものである。上記の位相検出器(11、12、13)は、基準周波数と発振器(4)の出力周波数との位相差を検出するためのものであり、デルタシグマ周波数決定器(11)を含んでいる。上記デジタルループフィルタは、位相検出器の下流に接続されており、デジタル制御発振器(4)を駆動するためのものである。  (もっと読む)

(もっと読む)

基準発振器の周波数安定化

従来技術の不利な点を取り除き、特性(1)高い長期安定性、(2)低位相雑音、(3)高耐熱性、(4)その基準発振器の周波数についての正確な値、を改善したMEMS基準発振器を提供することが、本発明の目的である。  (もっと読む)

(もっと読む)

通信システム

無線周波数送信機及び受信機における標準の周波数発生回路は、第1の基準周波数信号を出力するように動作する第1の電圧制御発振器と、第2の基準周波数信号を出力するように動作する第2の電圧制御発振器とを含む。また、位相同期ループ回路は、第1及び第2の基準周波数信号を受信するように接続され、第1の基準周波数信号から発生される一組の出力基準周波数信号の第1サブセット、及び第2の基準周波数信号から発生される出力基準周波数信号の第2サブセットとを有する一組の出力基準周波数信号を出力するように動作する一組の切替可能な分周器を含む。さらに、位相同期ループ回路は、外部の基準周波数信号及びフィードバック基準周波数信号を受信するように接続され、かつ、所望の第1及び第2の基準周波数信号を維持するために、受信した外部の基準周波数信号及びフィードバック基準周波数信号に従って第1及び第2の電圧制御発振器へ制御電圧を供給するように動作するVCO制御手段を含む。第1及び第2の基準周波数信号は、一組の出力基準周波数信号における出力基準周波数信号の周波数に等しくない。 (もっと読む)

クロックリカバリ回路及び通信デバイス

本発明に係るクロックリカバリ回路は、第1遅延量でデータ信号を順次遅延させる複数段の第1可変遅延素子と、第1遅延量より大きい第2遅延量で、クロック信号を順次遅延させる複数段の第2可変遅延素子と、複数段の第1可変遅延素子によって遅延された複数のデータ信号を、同一段の第2可変遅延素子によって遅延されたクロック信号によりサンプリングする複数のタイミングコンパレータと、連続する2つのタイミングコンパレータの2つのサンプリング結果を排他的論理和演算する複数のEOR回路と、複数のEOR回路の演算結果に基づいて、クロック信号を遅延させるリカバリ可変遅延回路とを有する。 (もっと読む)

201 - 220 / 224

[ Back to top ]